X 6801 : 1998

(1)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

まえがき

この規格は,工業標準化法に基づいて,日本工業標準調査会の審議を経て,通商産業大臣が制定した日

本工業規格である。

この規格に従うことは,次に示す特許権の使用に該当するおそれがある。

発明の名称

システムバス制御方法(特許第2504323号)

設定登録日

平成8年4月2日

発明の名称

データ転送制御方式(特許第2504548号)

設定登録日

平成8年4月2日

発明の名称

データ転送制御方式(特開平2-159661号)

設定登録日

平成10年1月16日

発明の名称

キャッシュメモリ一致制御方式(特開平3-214337号)

設定登録日

審査中

なお,この記載は,上記に示す特許権の効力,範囲などに関して何ら影響を与えるものではない。

上記特許権の使用者は,日本工業標準調査会に対して,非差別的,かつ,合理的な条件で,いかなる者

に対しても当該特許権の実施を許諾する意志があることを保証している。

この規格の一部が,上記に示す以外の技術的性質をもつ特許権,出願公開後の特許出願,実用新案権,

又は出願公開後の実用新案登録出願に抵触する可能性がある。主務大臣及び日本工業標準調査会は,この

ような技術的性質をもつ特許権,出願公開後の特許出願,実用新案権,又は出願公開後の実用新案登録出

願にかかわる確認について責任はもたない。

JIS X 6801には,次に示す附属書がある。

附属書A 性能(推定)

附属書B ロック転送時のアンサ返送

附属書C ロック転送とコピーバックキャッシュの書き戻し

X 6801 : 1998

(1)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

目次

ページ

1. 概要 ······························································································································ 1

1.1 適用範囲 ······················································································································ 1

1.2 用途 ···························································································································· 1

2. 定嚢 ······························································································································ 2

2.1 用語 ···························································································································· 2

2.2 表記 ···························································································································· 4

3. インタフェース ··············································································································· 4

3.1 インタフェース信号 ······································································································· 4

4. バス動作説明 ·················································································································· 7

4.1 基本動作プロトコル ······································································································· 7

4.2 転送プロトコル ············································································································ 10

4.2.1 バスオペレーションの種別 ··························································································· 10

4.2.2 コマンドフォーマット ································································································· 11

4.2.3 転送シーケンス ·········································································································· 16

4.3 アービトレーション ······································································································ 18

4.4 受信状態報告 ··············································································································· 18

4.5 データ転送 ·················································································································· 19

4.5.1 メモリアクセス(ライト) ··························································································· 19

4.5.2 メモリアクセス(リード) ··························································································· 25

4.5.3 制御空間アクセス(ライト) ························································································ 28

4.5.4 制御空間アクセス(リード) ························································································ 30

4.5.5 メッセージ転送 ·········································································································· 32

4.5.6 制御レジスタアクセス(ライト) ·················································································· 34

4.5.7 制御レジスタアクセス(リード) ·················································································· 36

4.6 ロック動作 ·················································································································· 38

4.7 キャッシュ関連動作 ······································································································ 39

4.7.1 キャッシュ無効化指示動作 ··························································································· 40

4.7.2 リトライ指示動作 ······································································································· 42

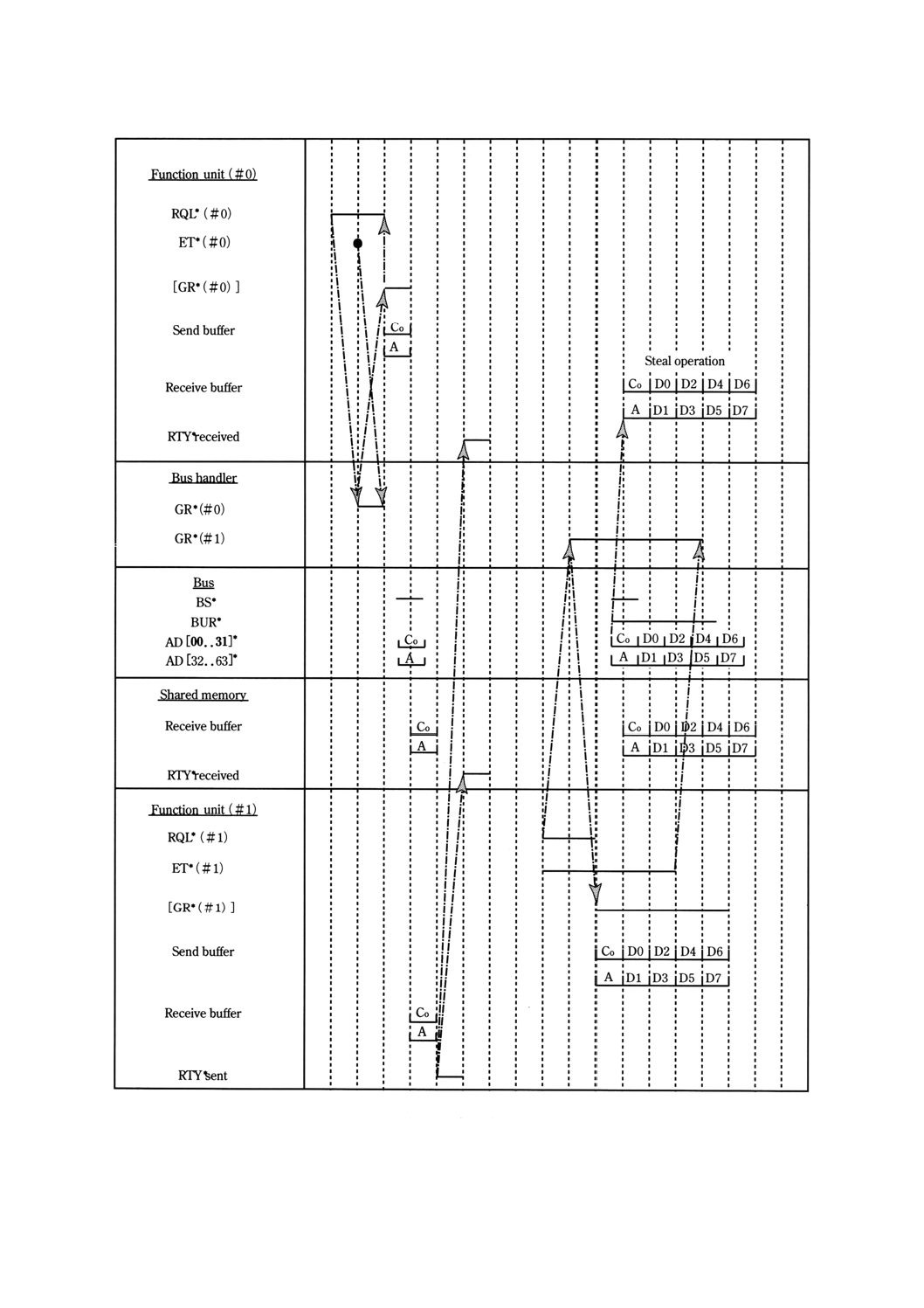

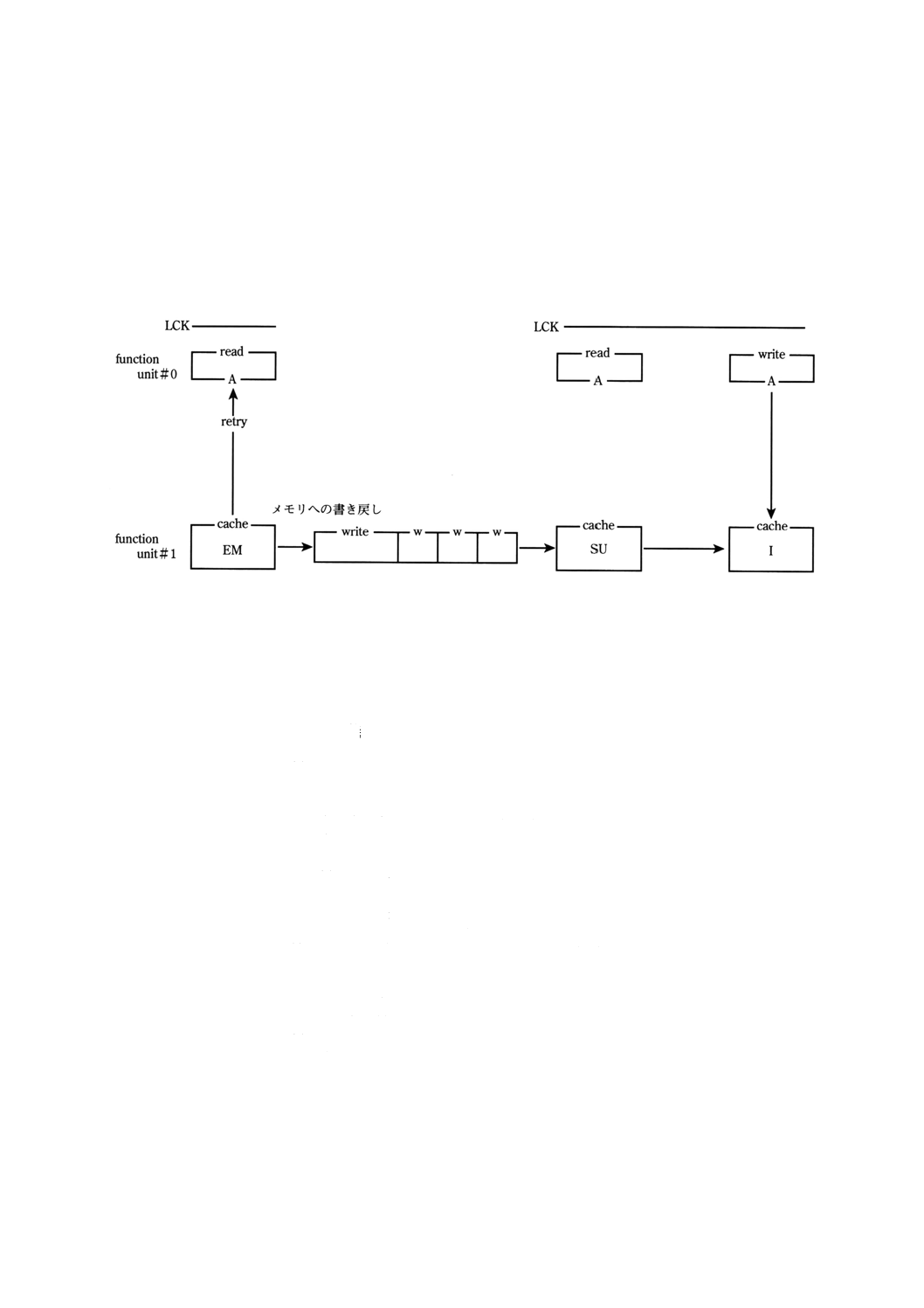

4.7.3 リトライ指示後のコピーバック動作とスチール動作 ··························································· 44

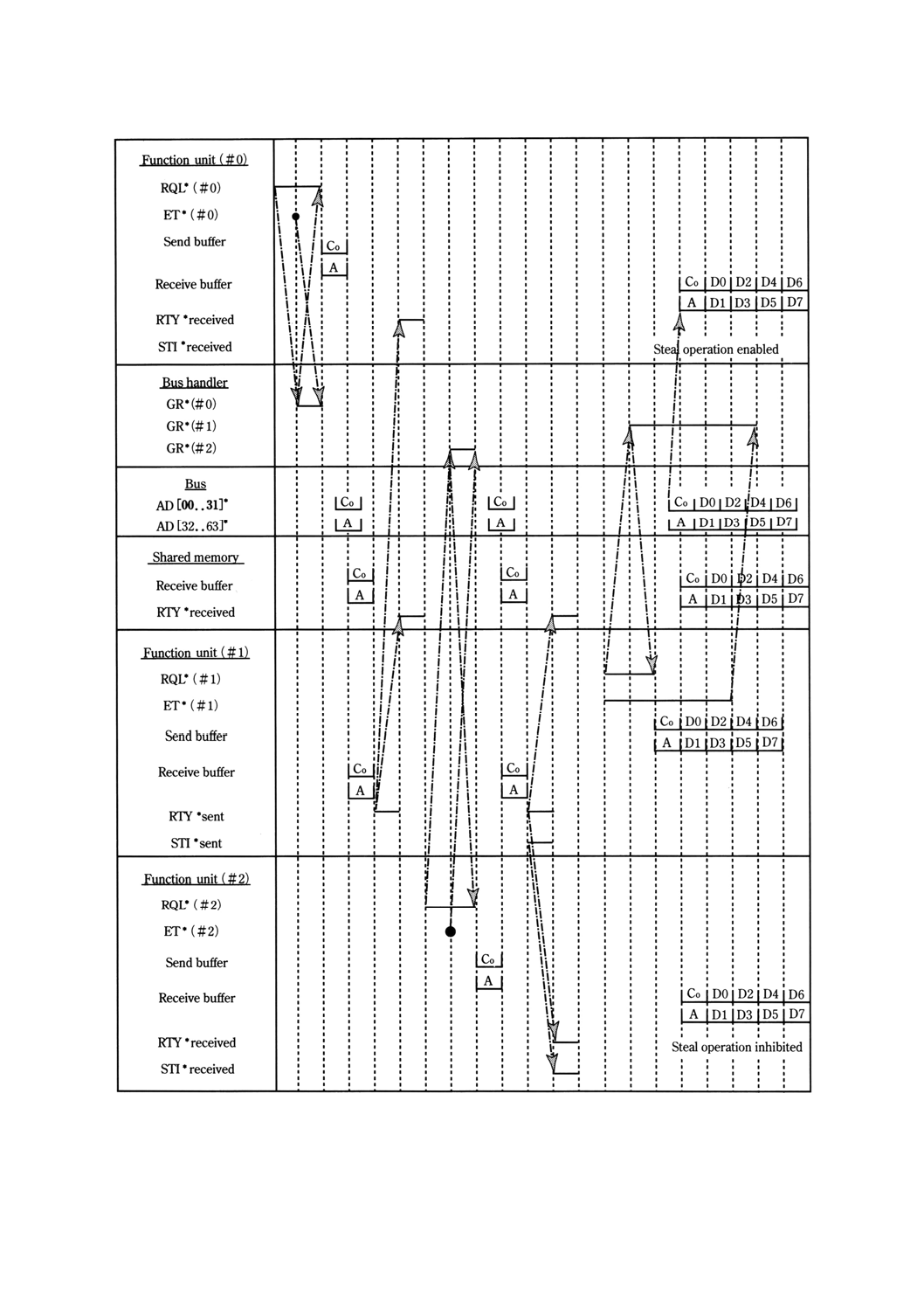

4.7.4 スチール禁止指示動作 ································································································· 46

4.8 異常処理 ····················································································································· 48

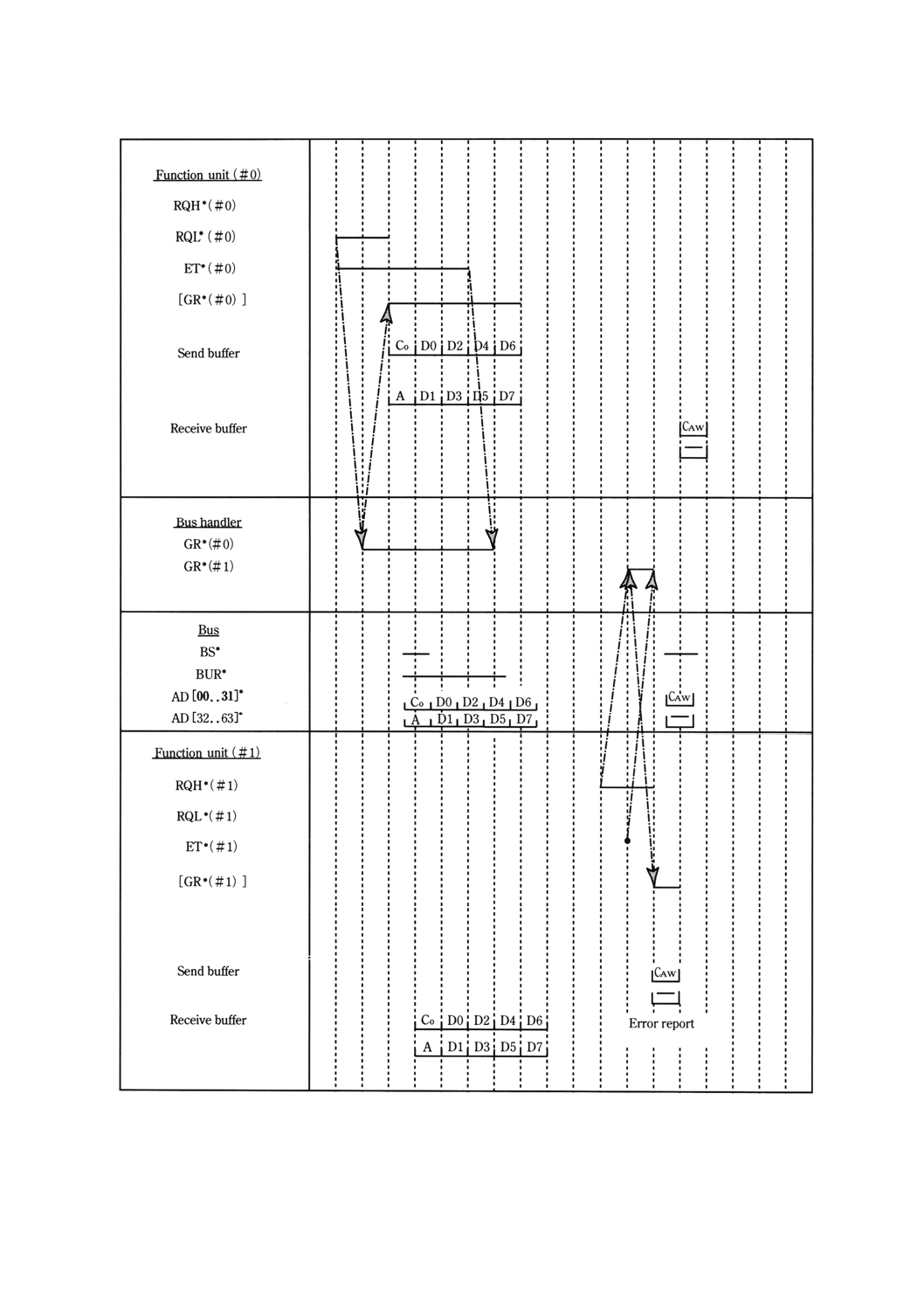

4.8.1 アンサによって報告される異常処理 ··············································································· 48

4.8.2 その他の異常処理 ······································································································· 50

5. キャッシュのコヒーレンシ制御 ························································································· 50

5.1 キャッシュ制御方式の種類······························································································ 50

X 6801 : 1998 目次

(2)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ページ

5.2 キャッシュデータの属性································································································· 50

5.3 システムバス上の動作···································································································· 51

5.4 リトライ指示動作 ········································································································· 53

5.5 スチール動作 ··············································································································· 53

5.6 キャッシュデータ管理と状態遷移 ····················································································· 53

5.6.1 ライトスルーのキャッシュ ··························································································· 54

5.6.2 コピーバックキャッシュ ······························································································ 56

5.7 メモリアクセス時の注意事項 ··························································································· 60

6. 高信頼化機能 ················································································································· 60

6.1 冗長構成 ····················································································································· 60

6.2 障害検出 ····················································································································· 61

6.3 障害波及の防止 ············································································································ 61

6.4 障害処理・診断のサポート······························································································ 61

附属書A(参考) 性能(推定) ··························································································· 62

附属書B(参考) ロック転送時のアンサ返送 ·········································································· 63

附属書C(参考) ロック転送とコピーバックキャッシュの書き戻し ············································ 64

図の一覧

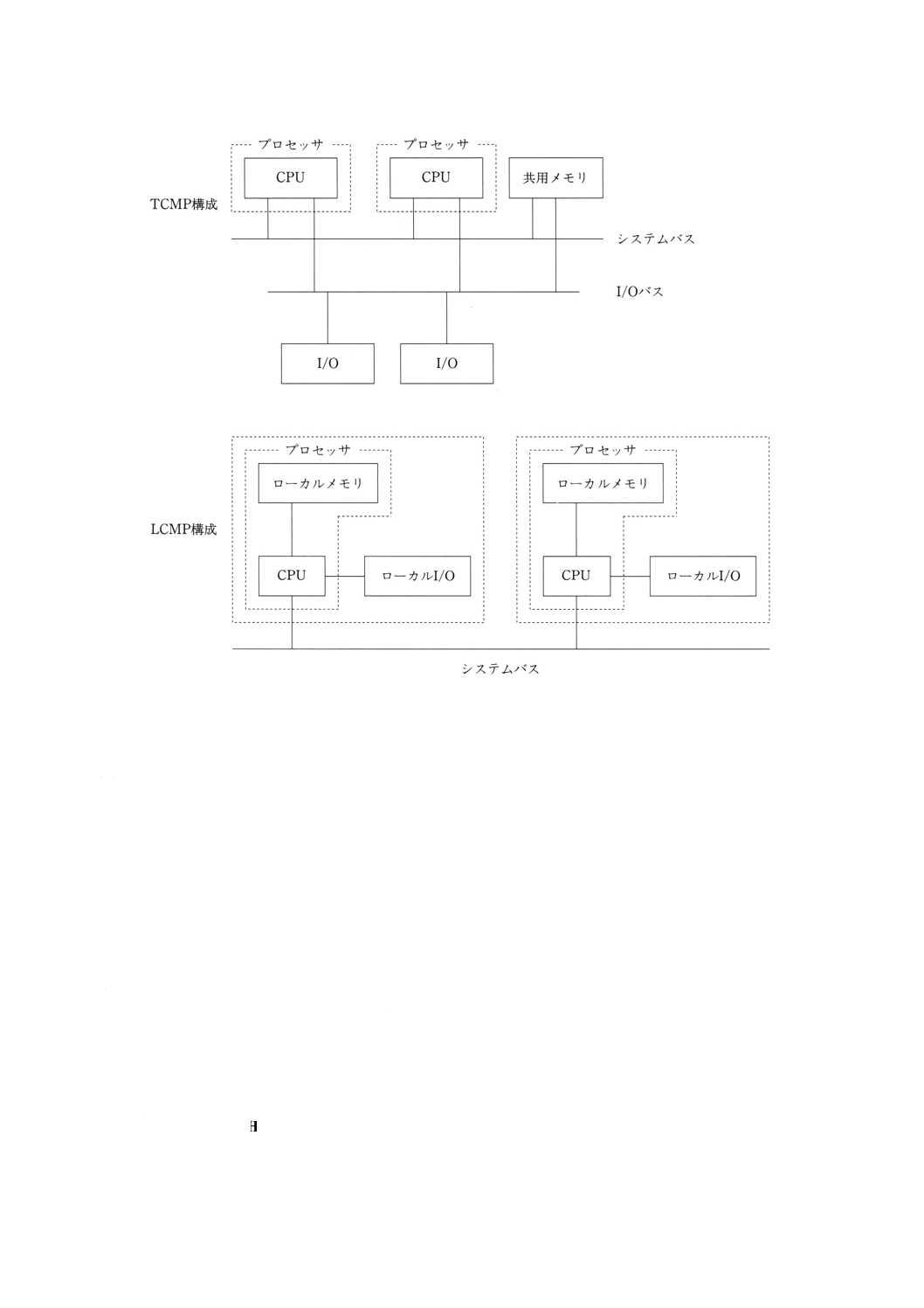

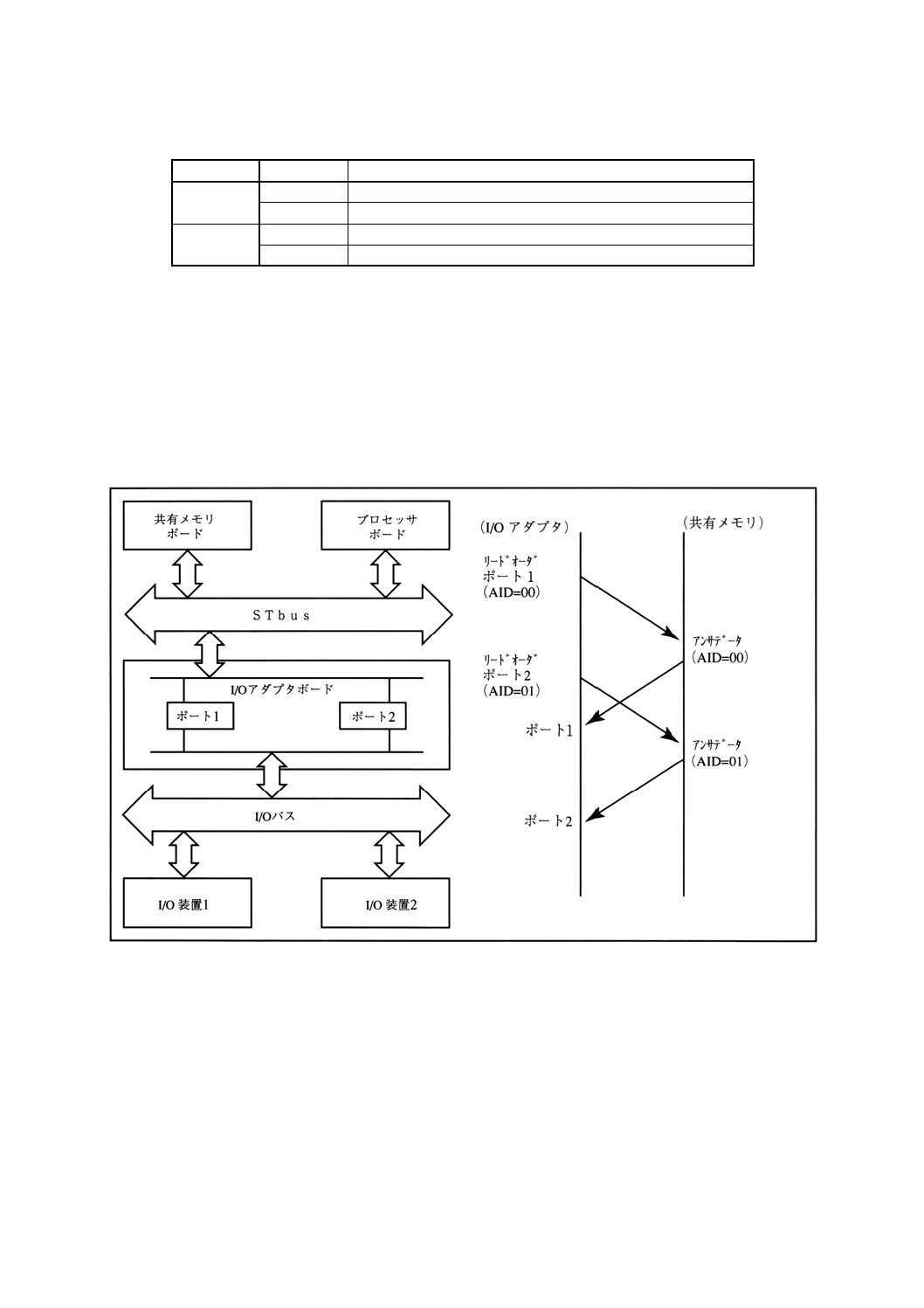

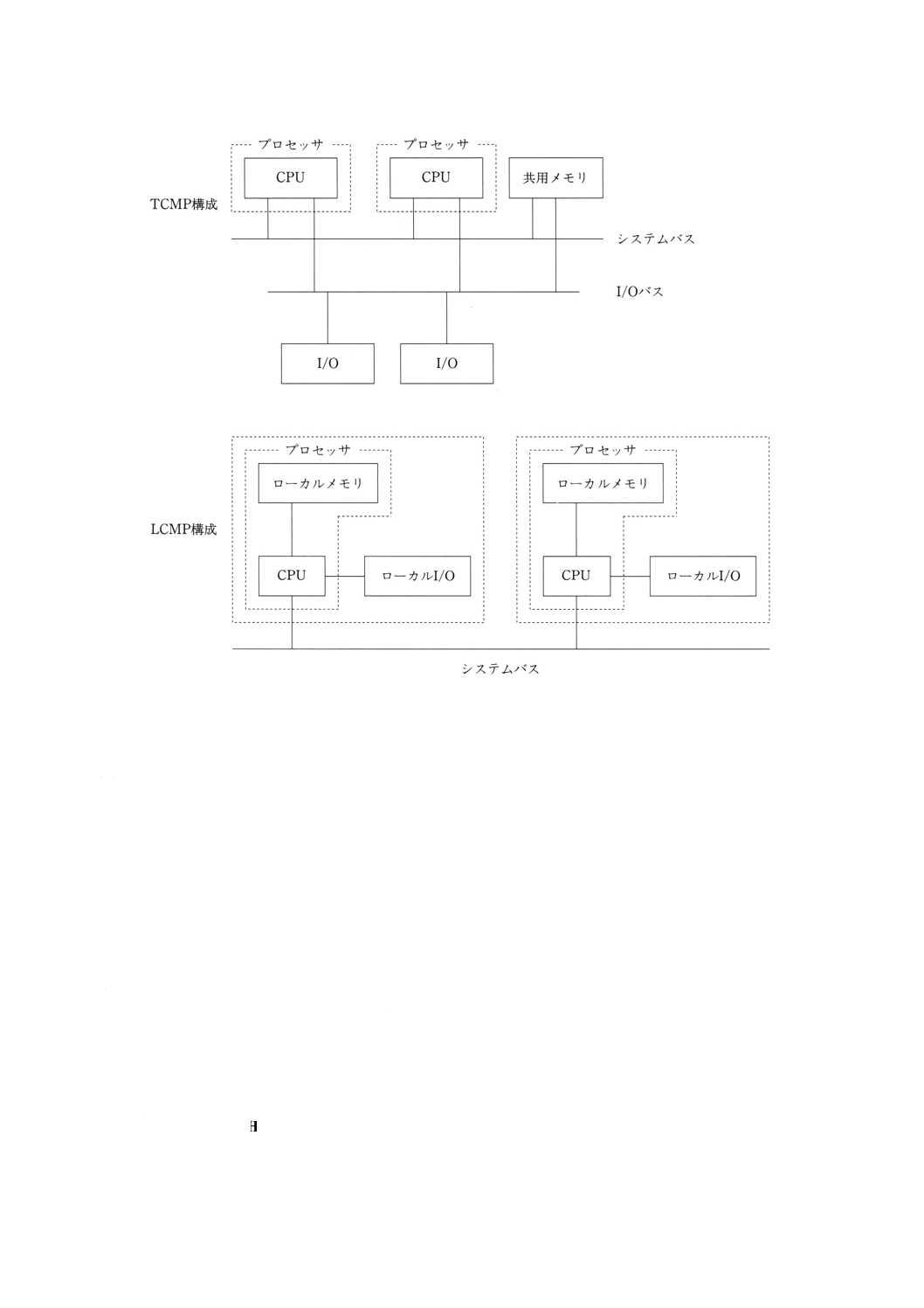

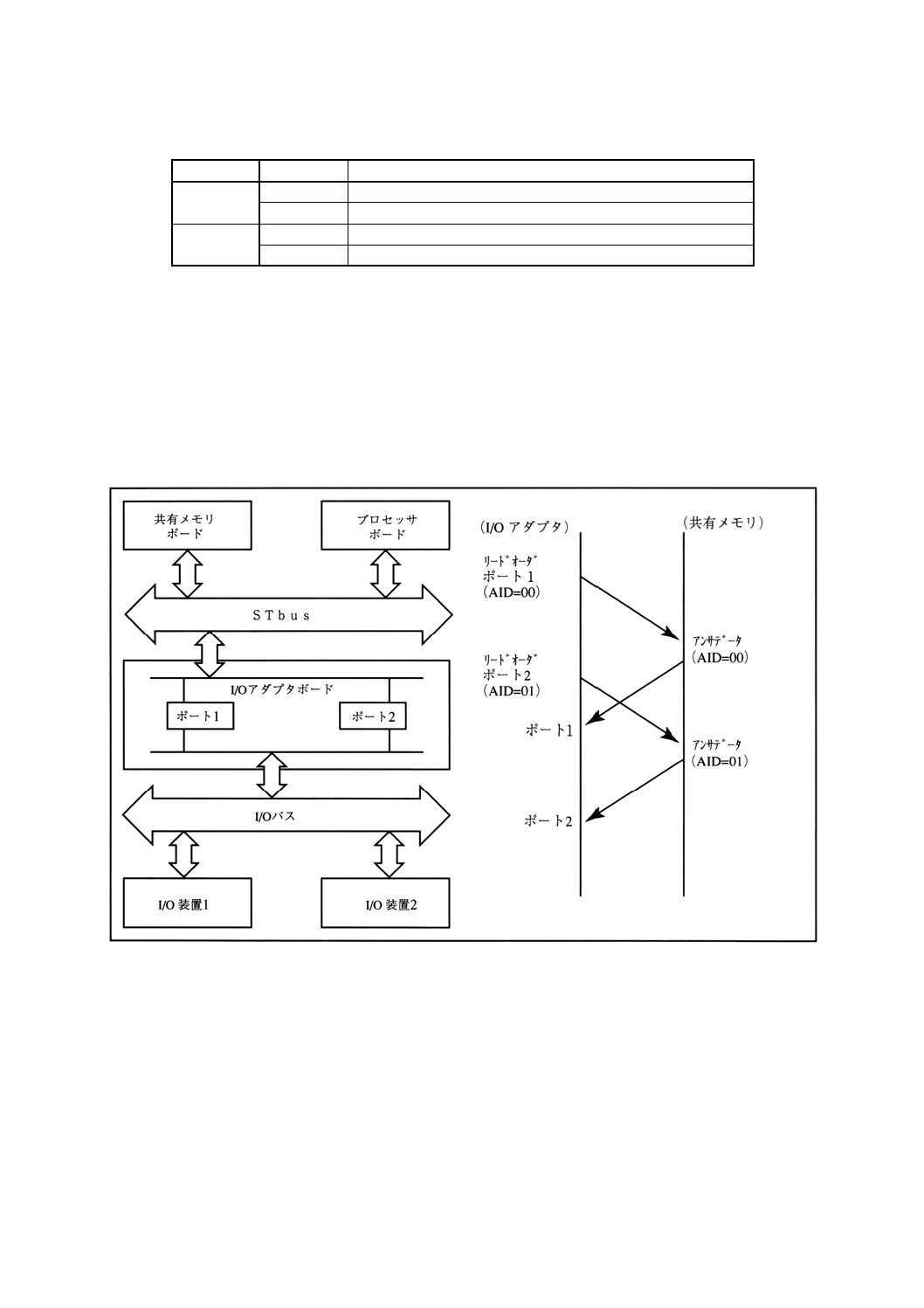

図1 STbusの用途················································································································ 2

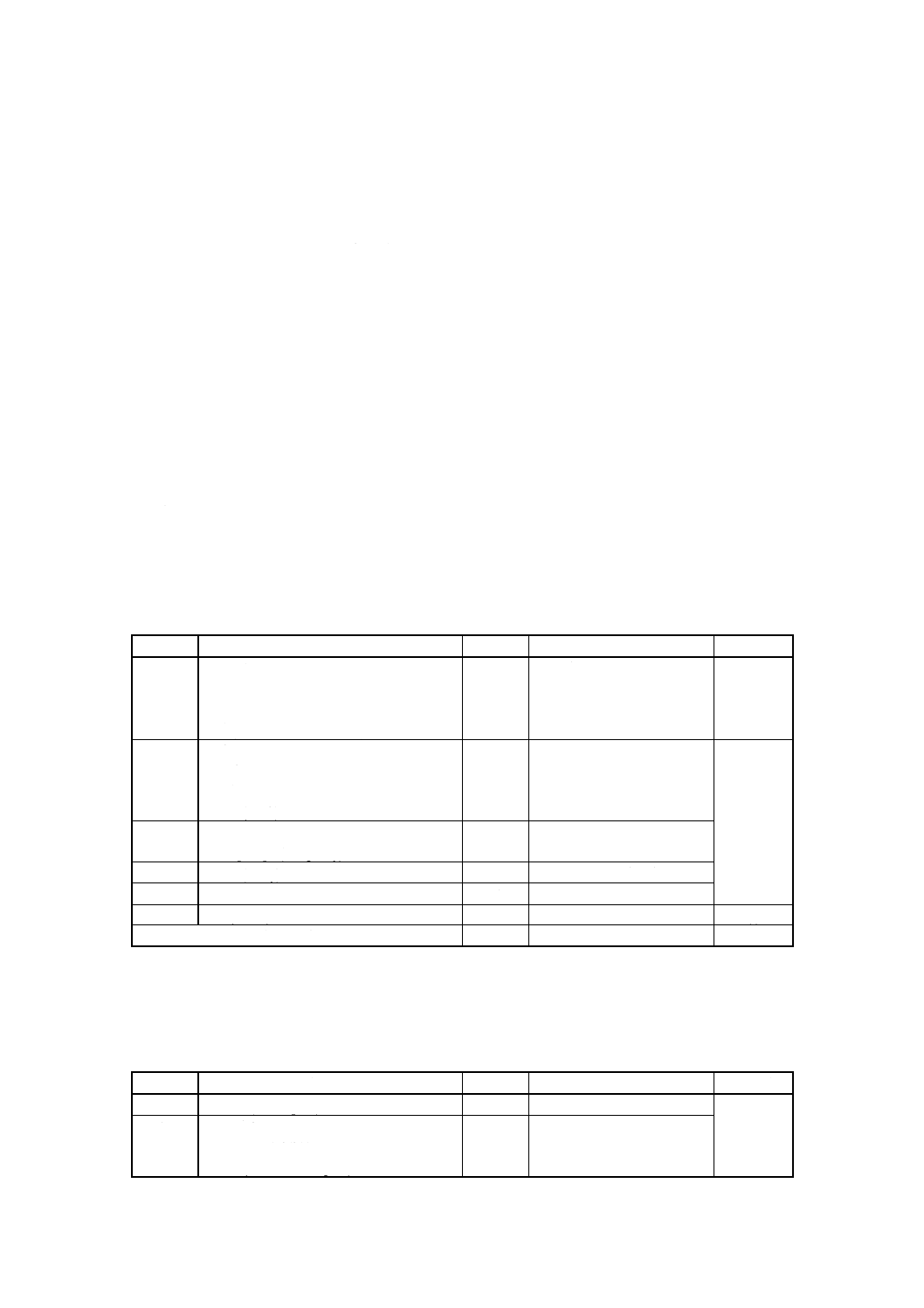

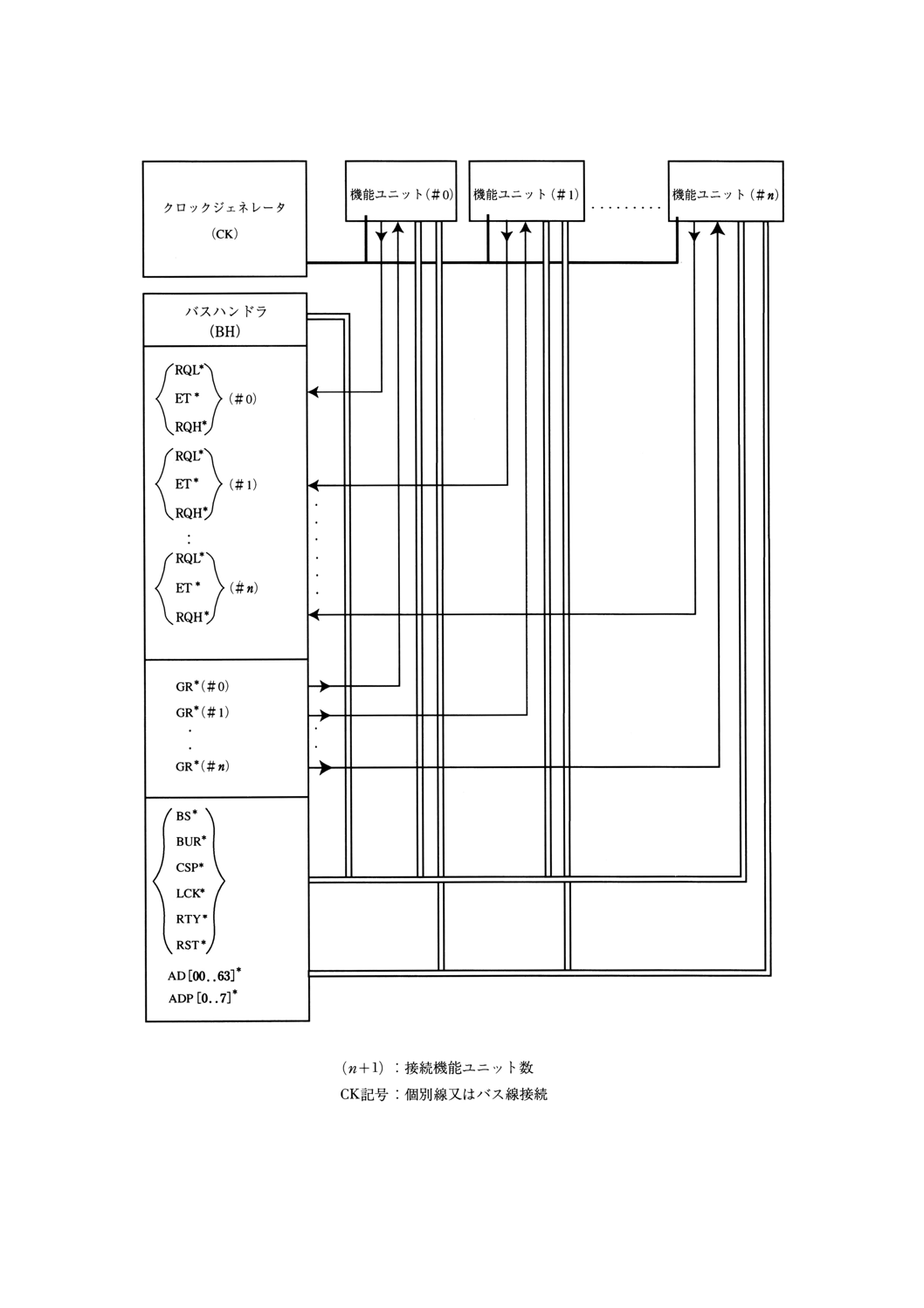

図2 機能ユニット間接続インタフェース(基本形) ·································································· 5

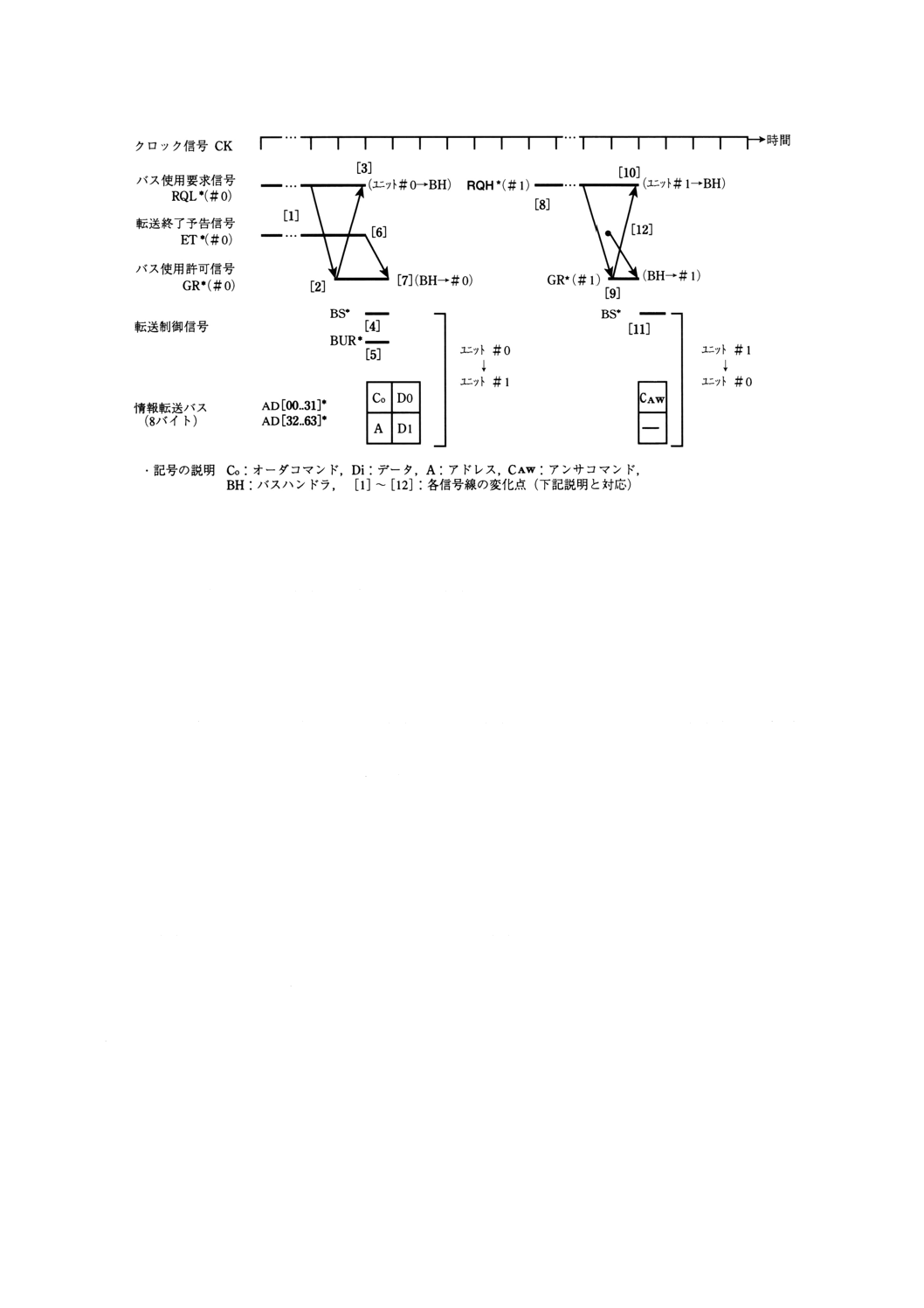

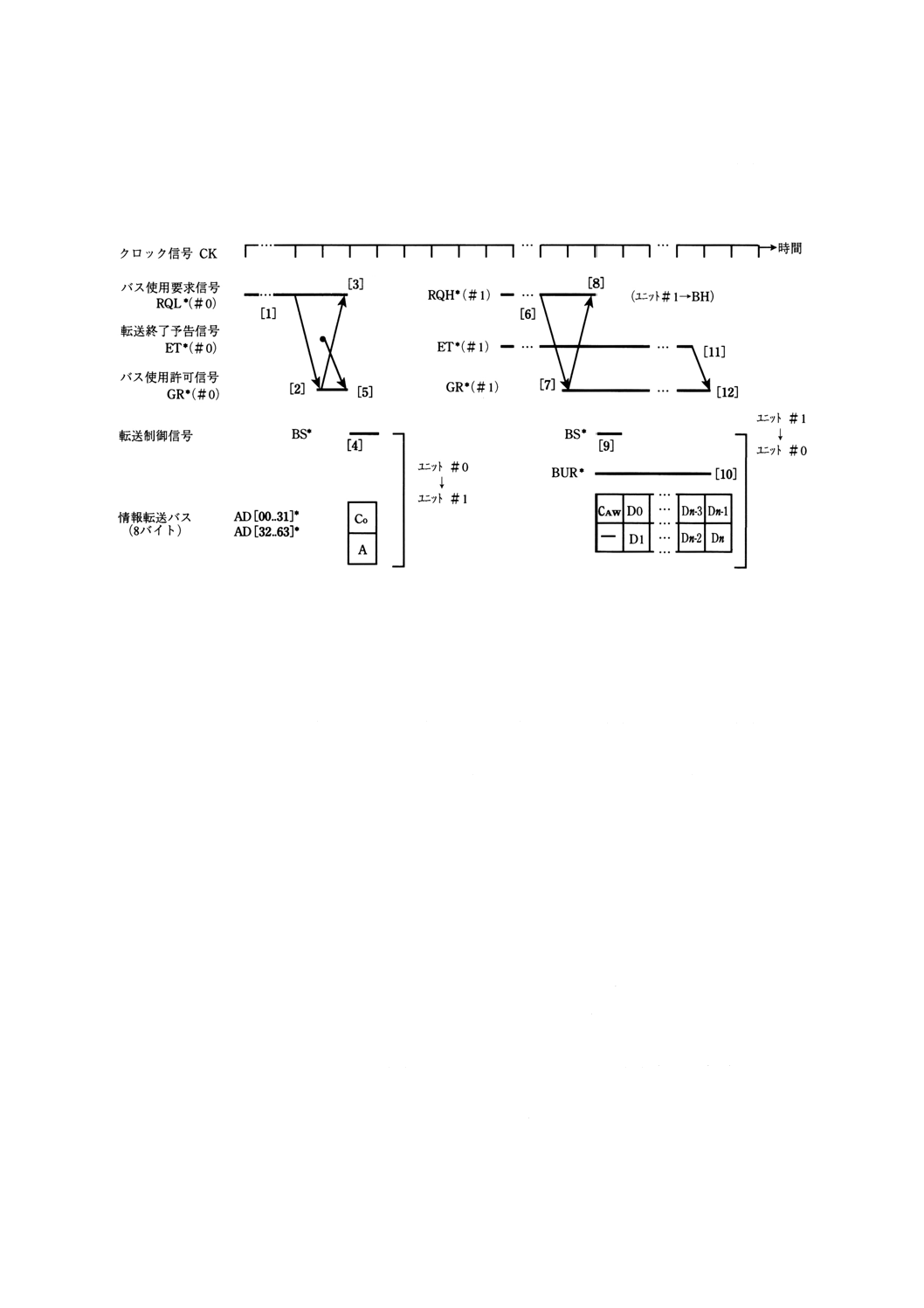

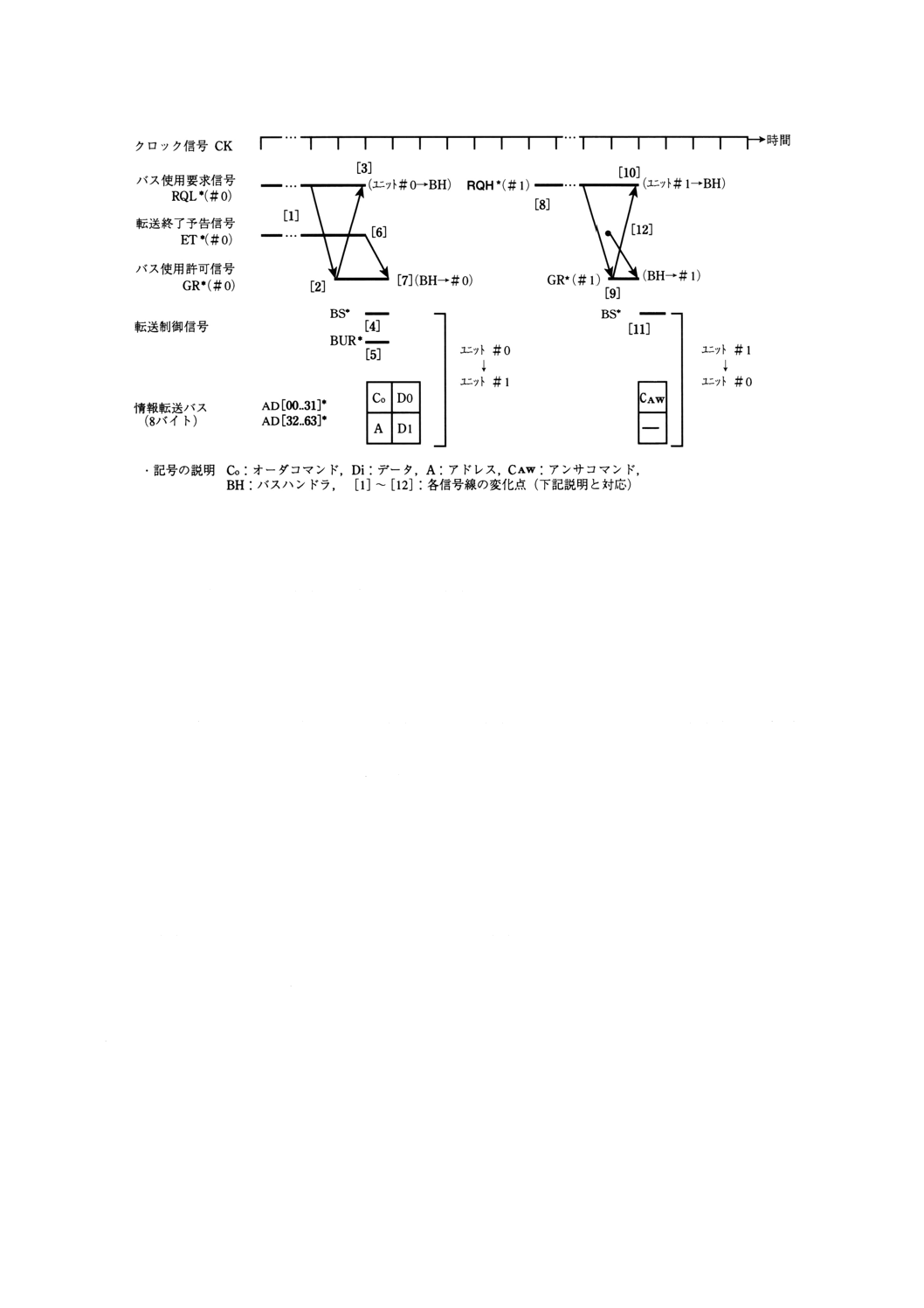

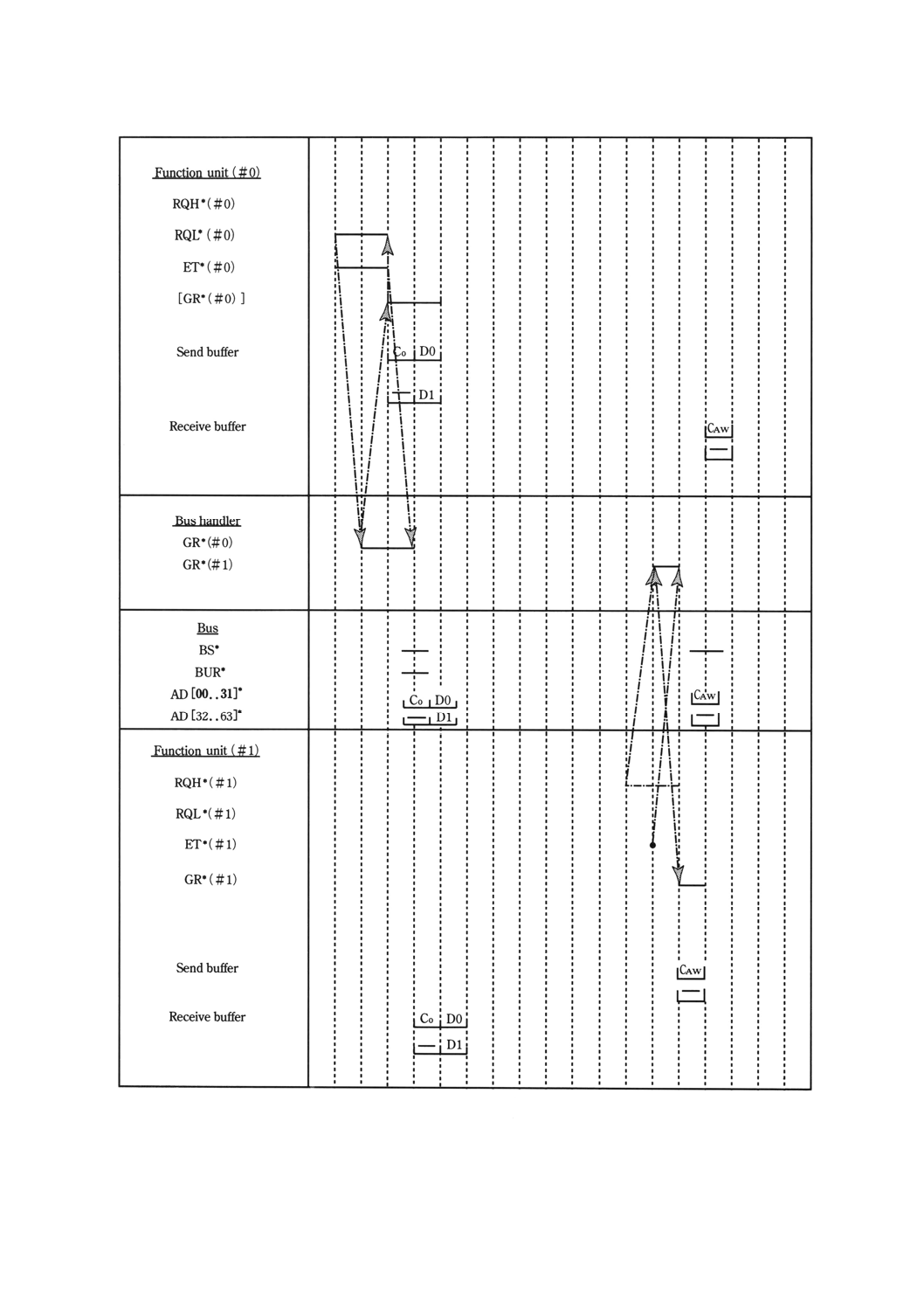

図3 バス動作プロトコルの概念

(1−サイクル,2−サイクル転送時:バス幅8バイトで,かつライト動作) ··························· 8

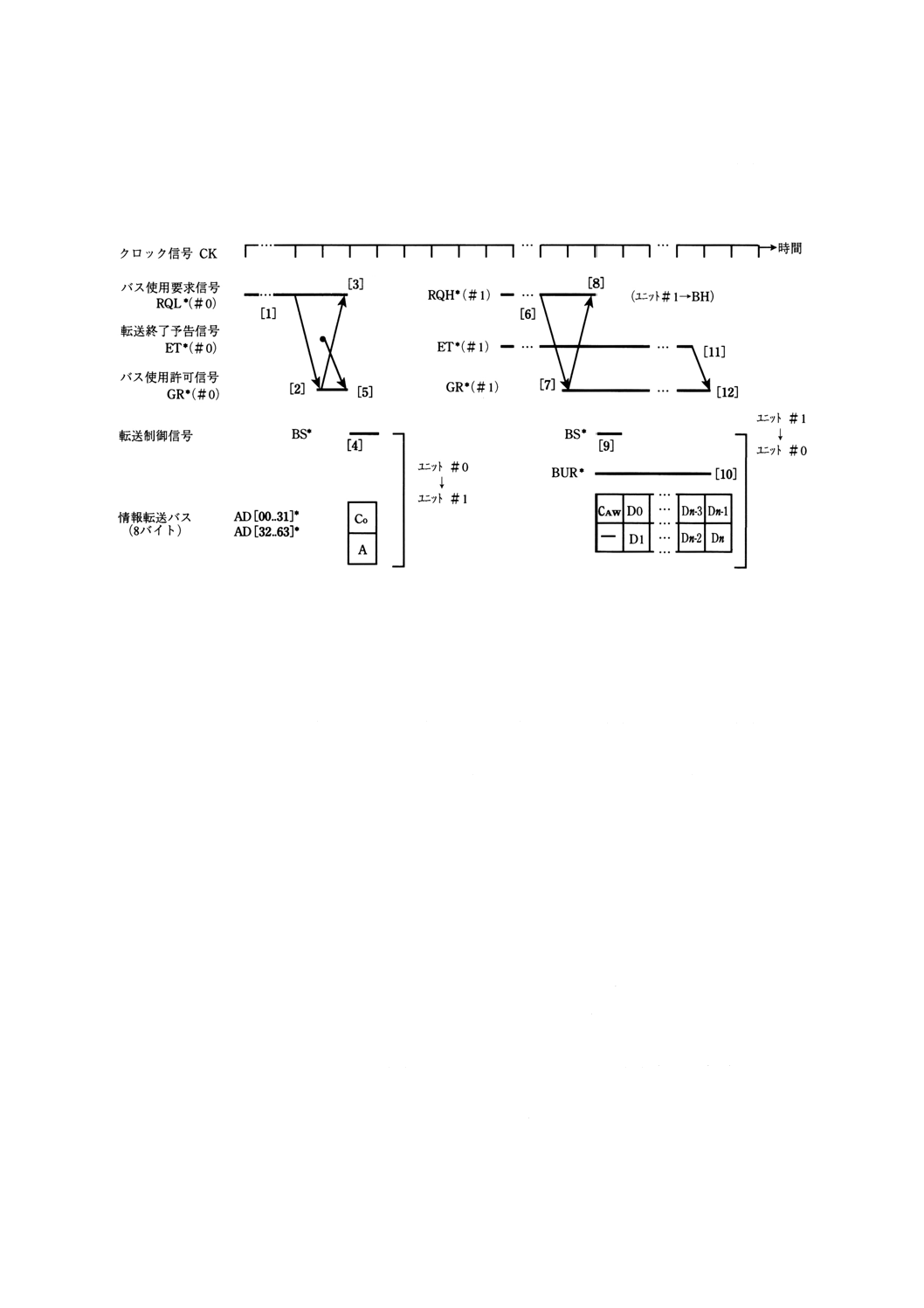

図4 バス動作プロトコルの概念

(3−サイクル以上の転送時:バス幅8バイトで,かつリード動作) ····································· 9

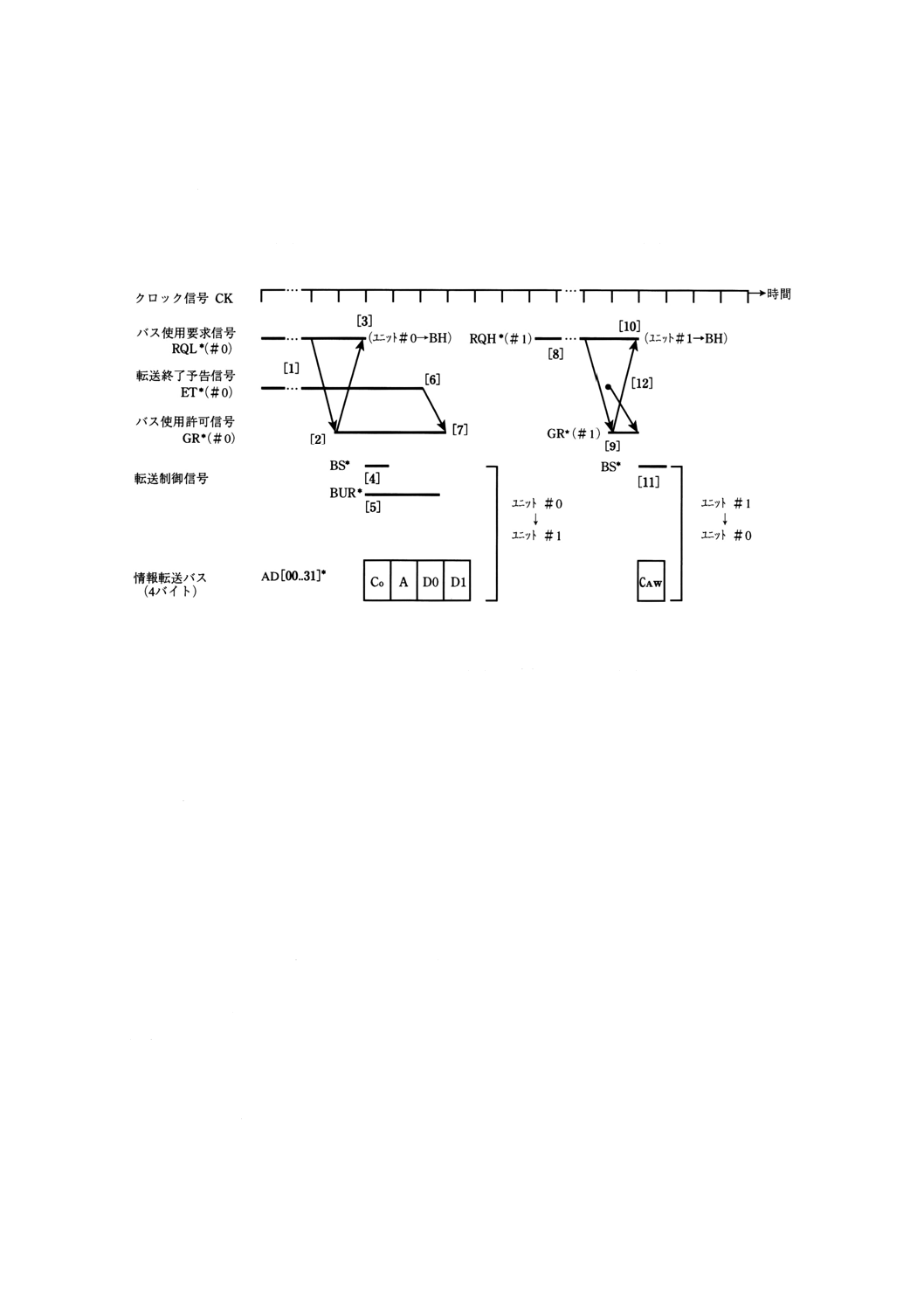

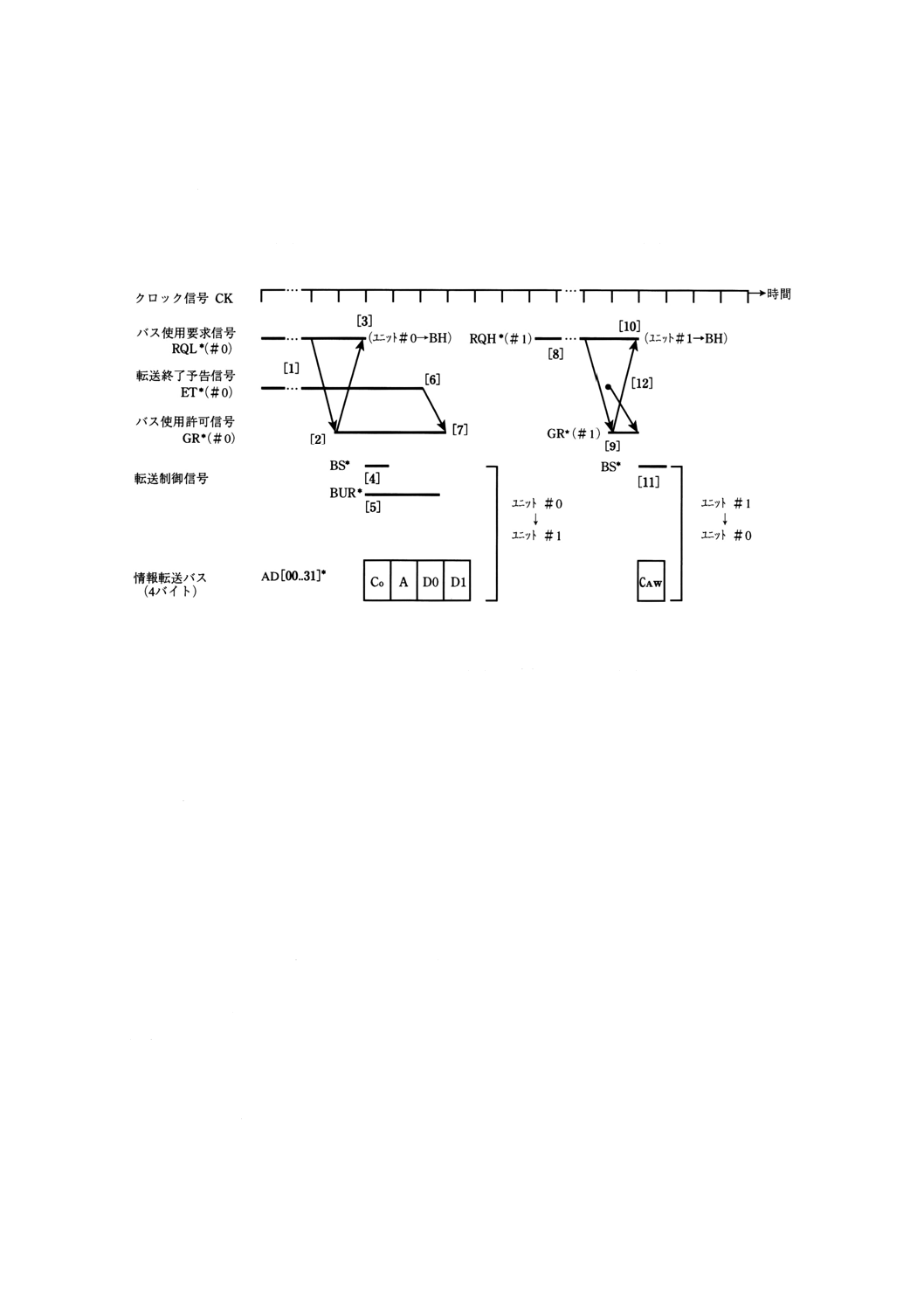

図5 バス動作プロトコルの概念

(1−サイクル,2−サイクル転送時:バス幅4バイトで,かつライト動作) ·························· 10

図6 パイプライン動作 ········································································································ 13

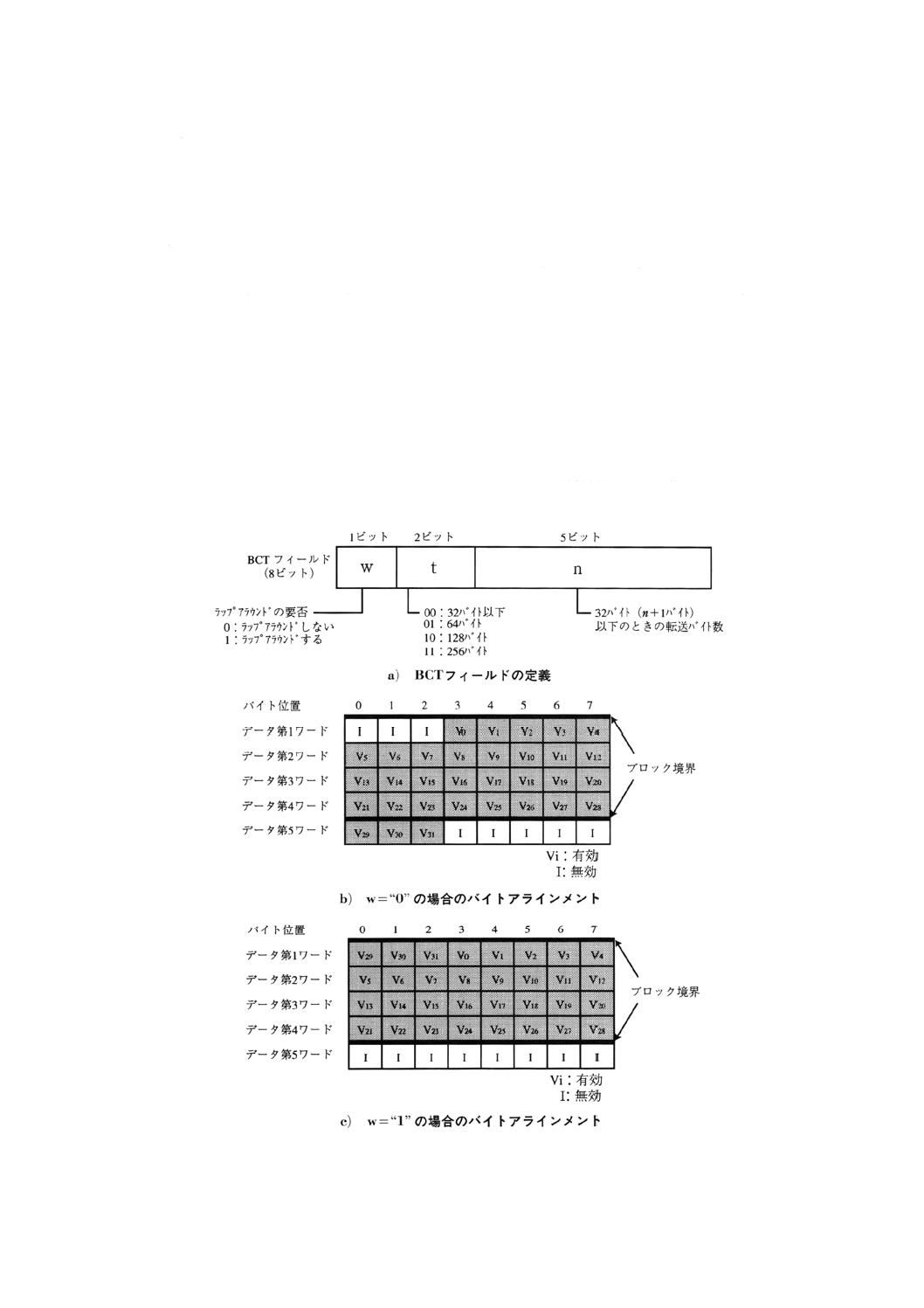

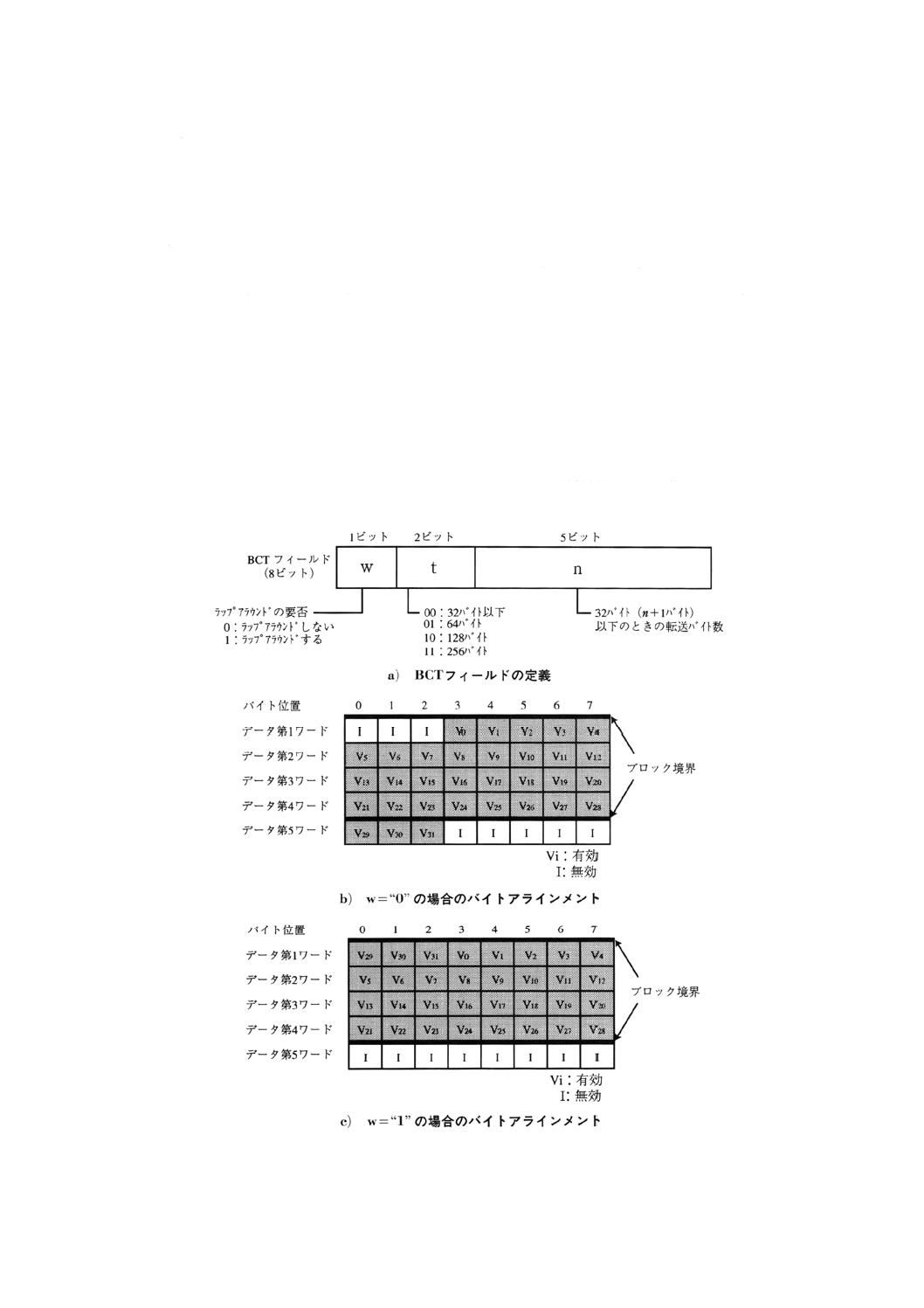

図7 BCTフィールド ·········································································································· 14

図8 RAとバイトアラインメント ·························································································· 16

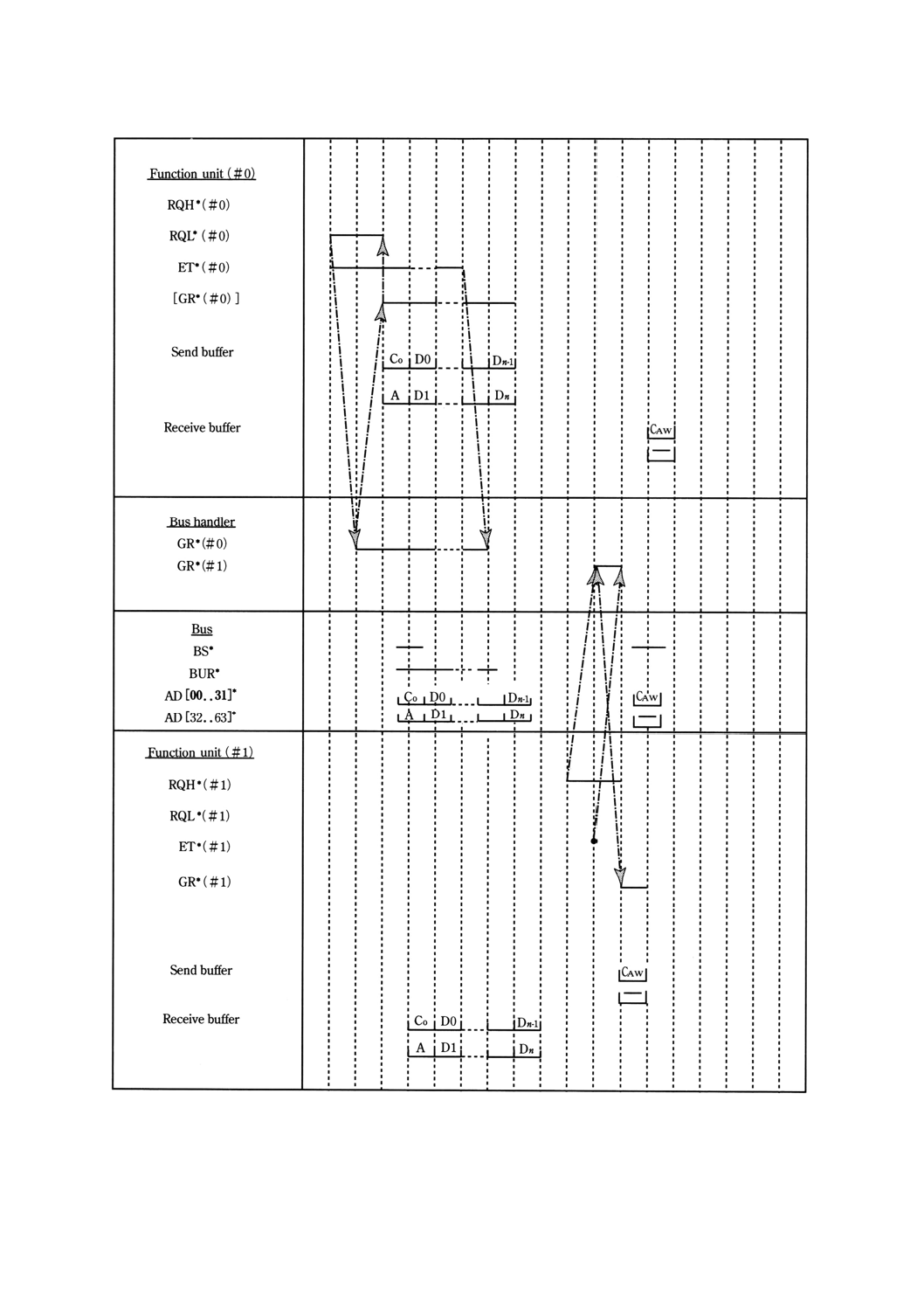

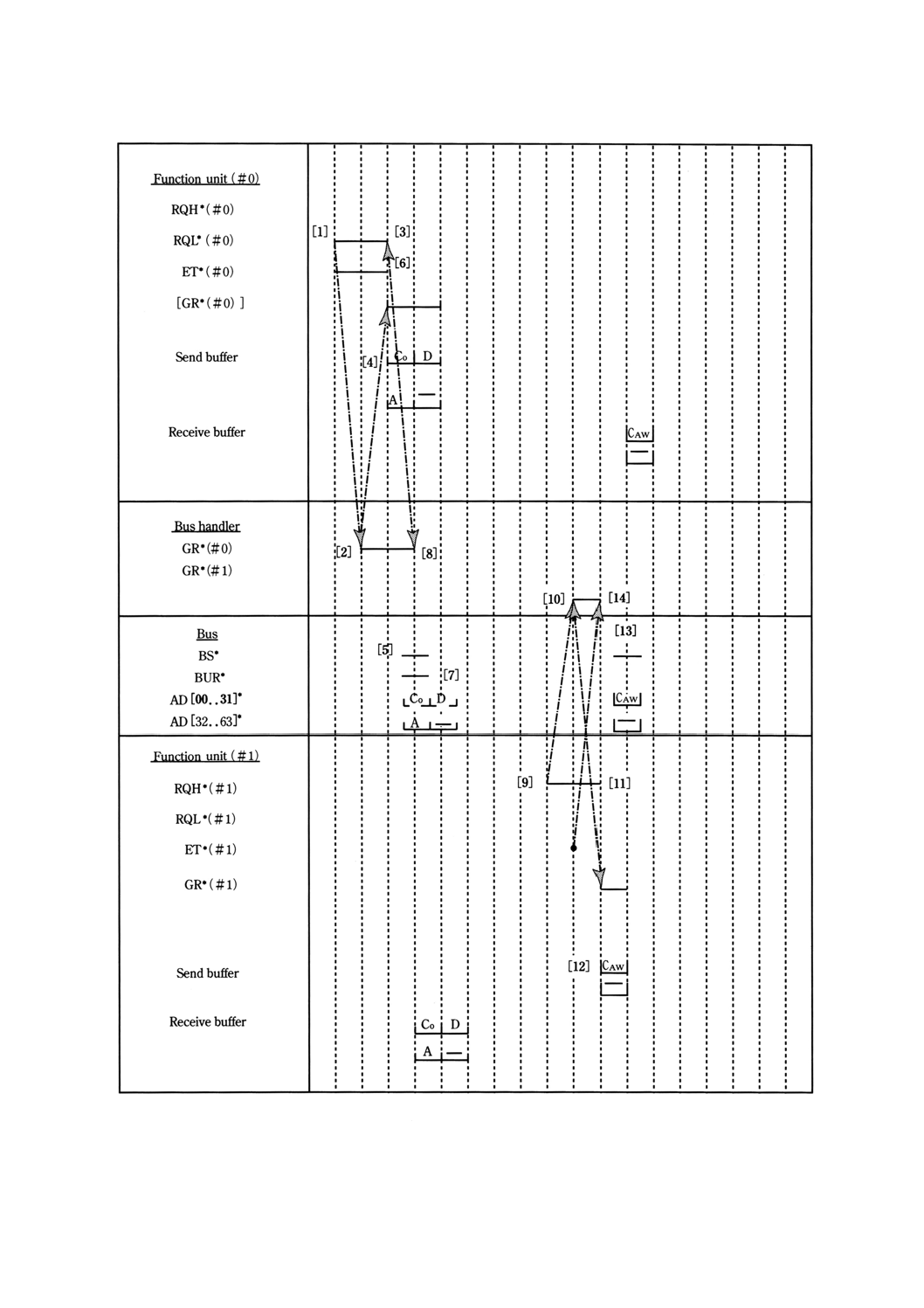

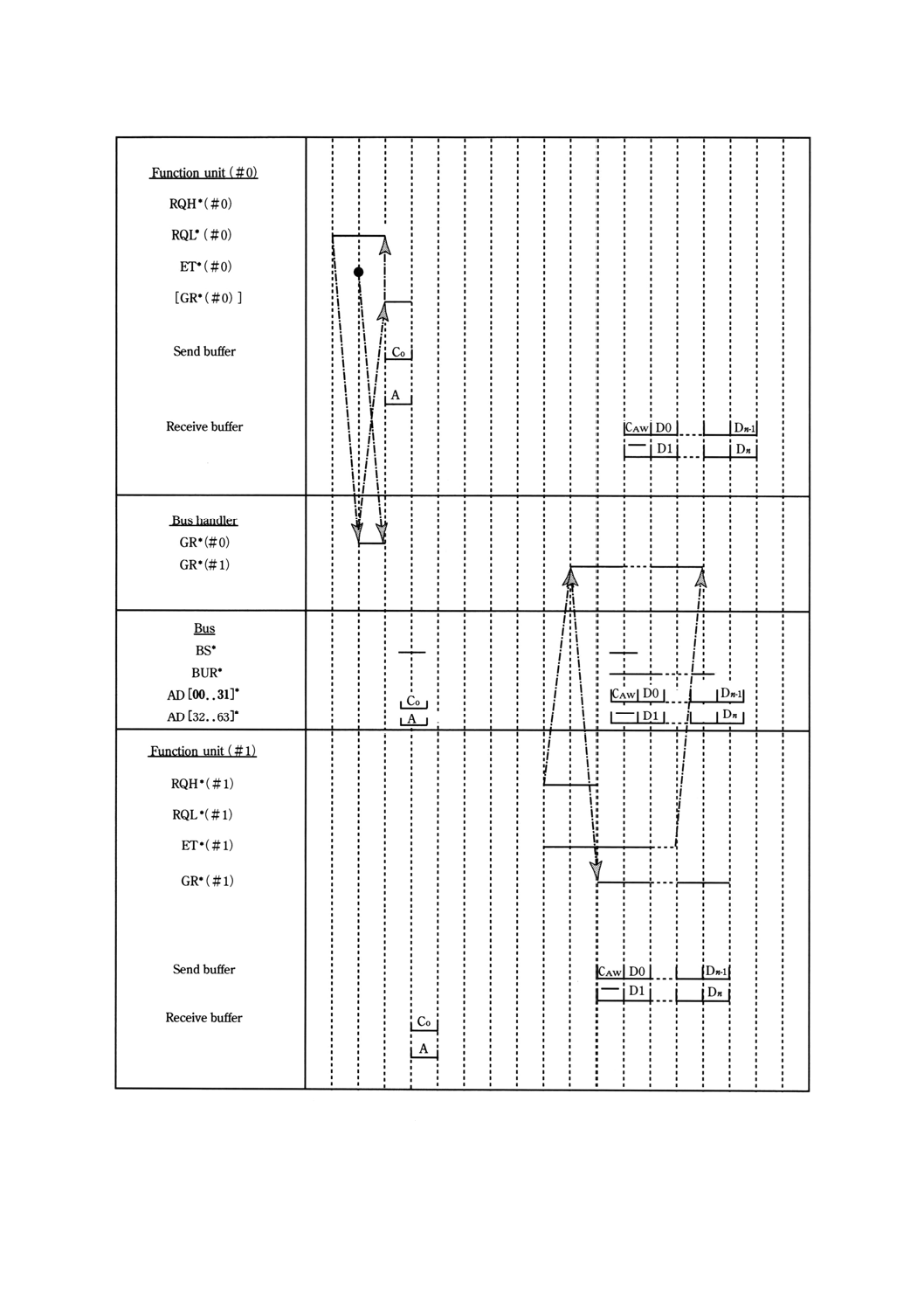

図9 a) 1語メモリライト(アンサを伴わない転送) ·································································· 21

図9 b) 1語メモリライト ····································································································· 22

図9 c) n語メモリライト(アンサを伴わない転送) ·································································· 23

図9 d) n語メモリライト ····································································································· 24

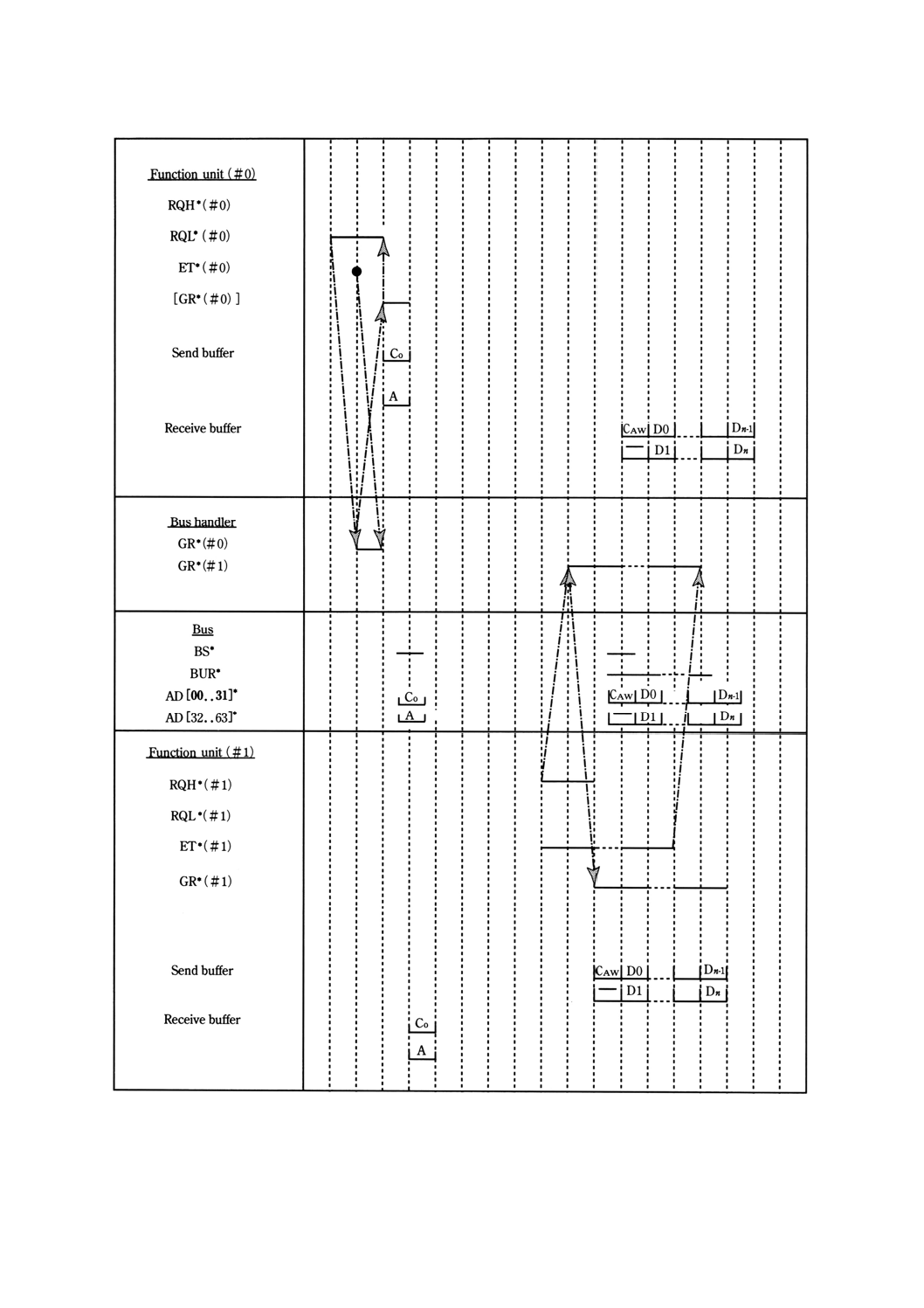

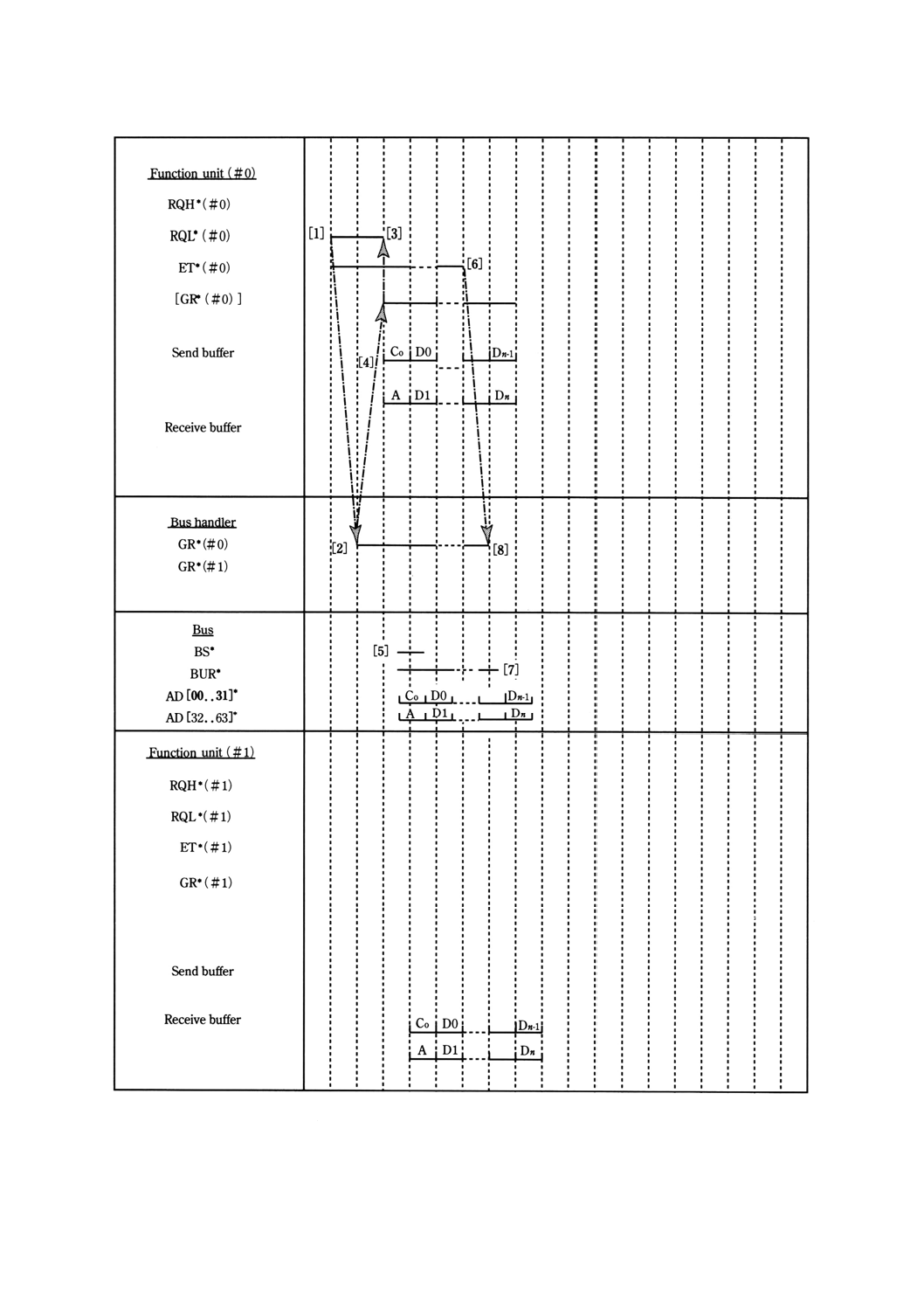

図10 a) 1語メモリリード ···································································································· 26

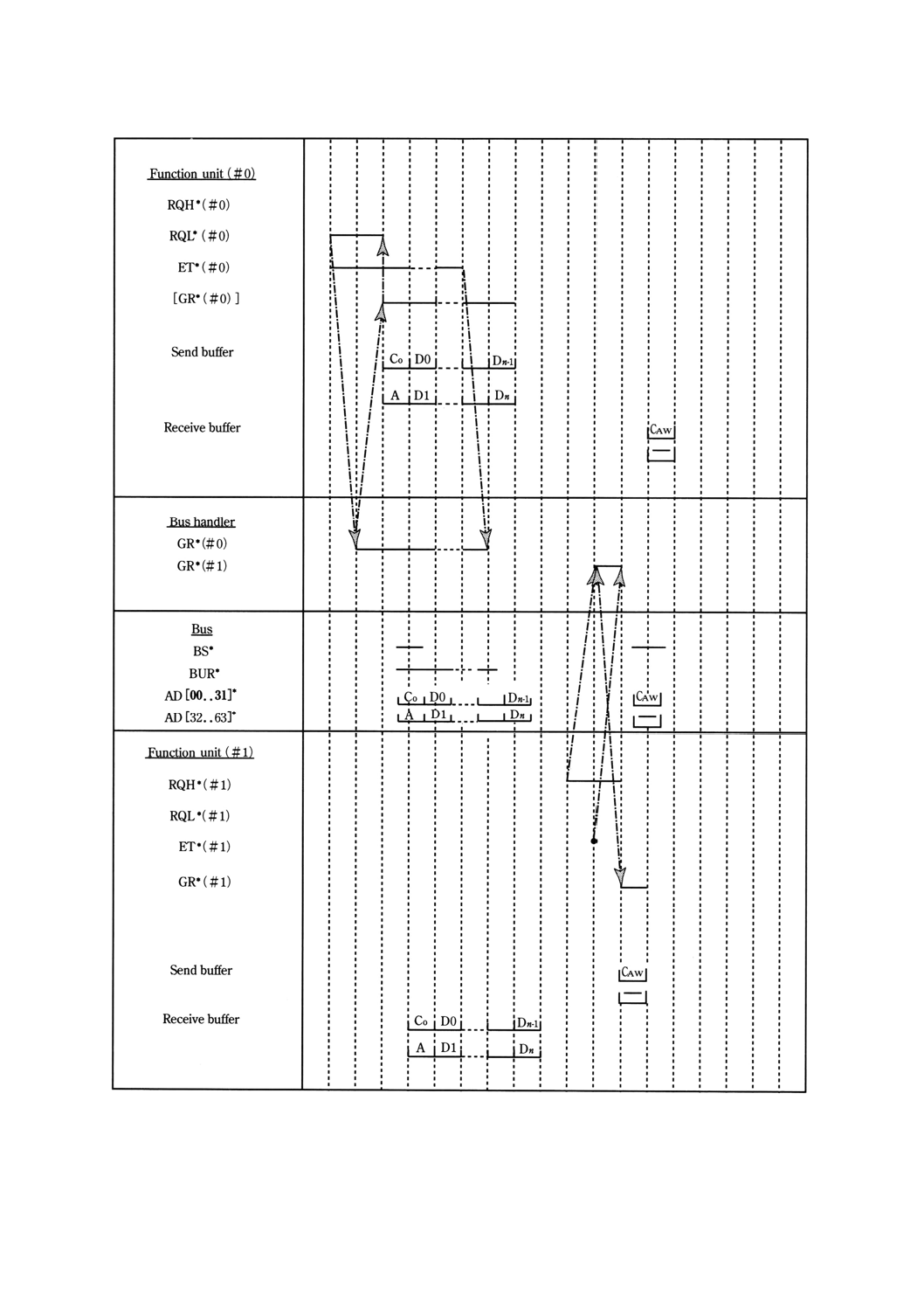

図10 b) n語メモリリード ···································································································· 27

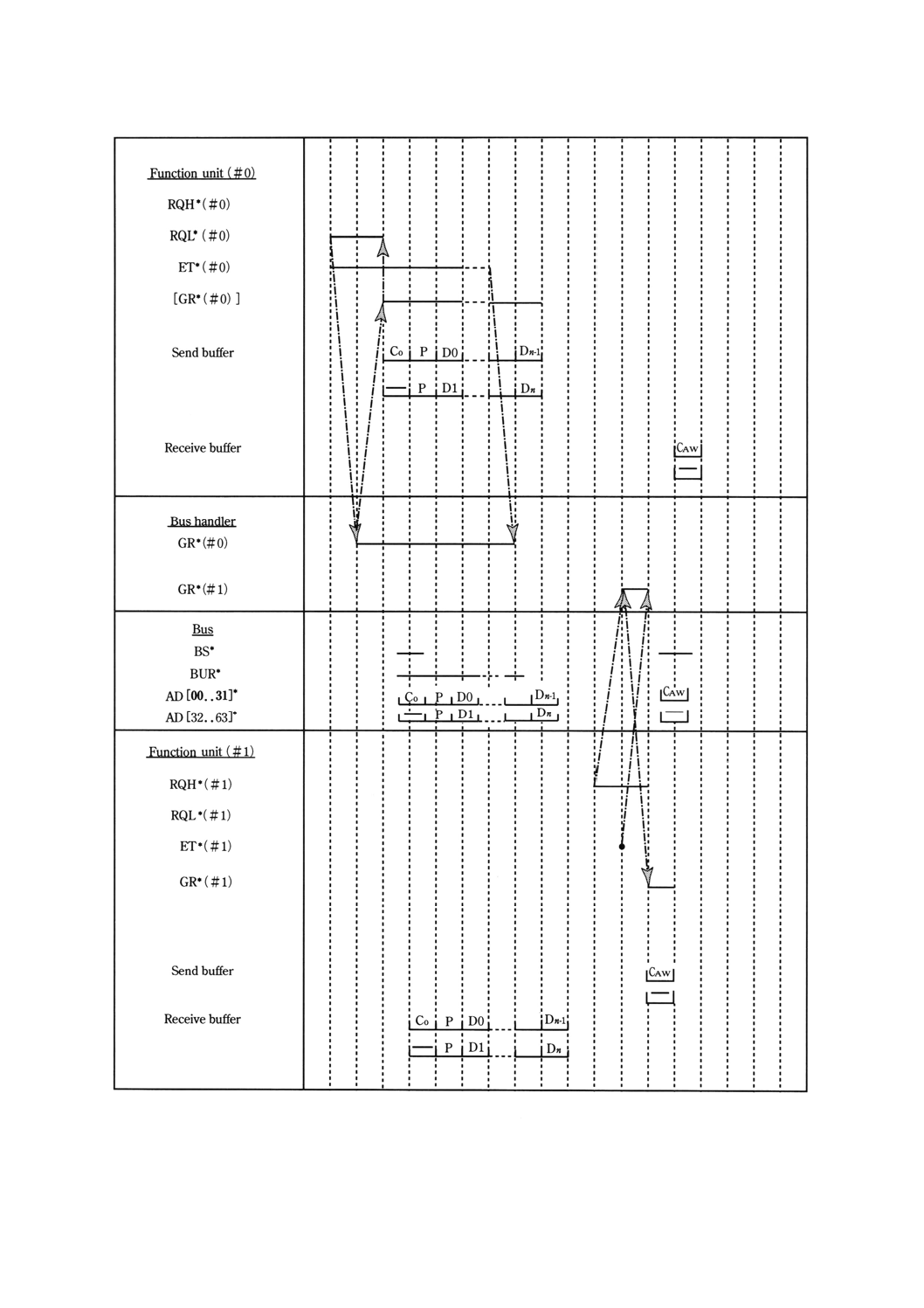

図11 n語ライト:制御空間アクセス ····················································································· 29

図12 n語リード:制御空間アクセス ····················································································· 31

図13 n語メッセージ転送 ···································································································· 33

図14 1語ライト:制御レジスタアクセス ··············································································· 35

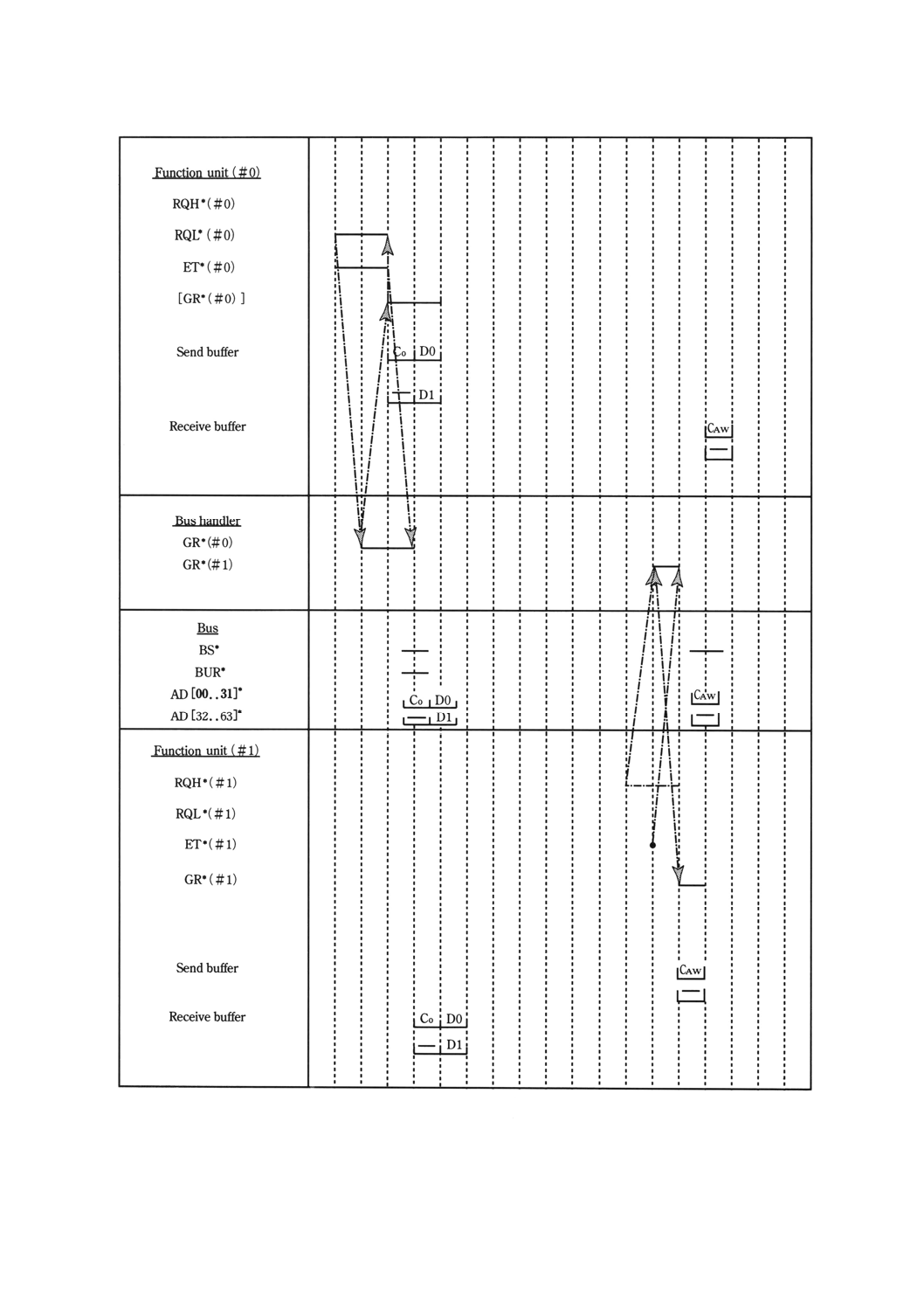

X 6801 : 1998 目次

(3)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ページ

図15 1語リード:制御レジスタアクセス ··············································································· 37

図16 バスロック転送 ········································································································· 39

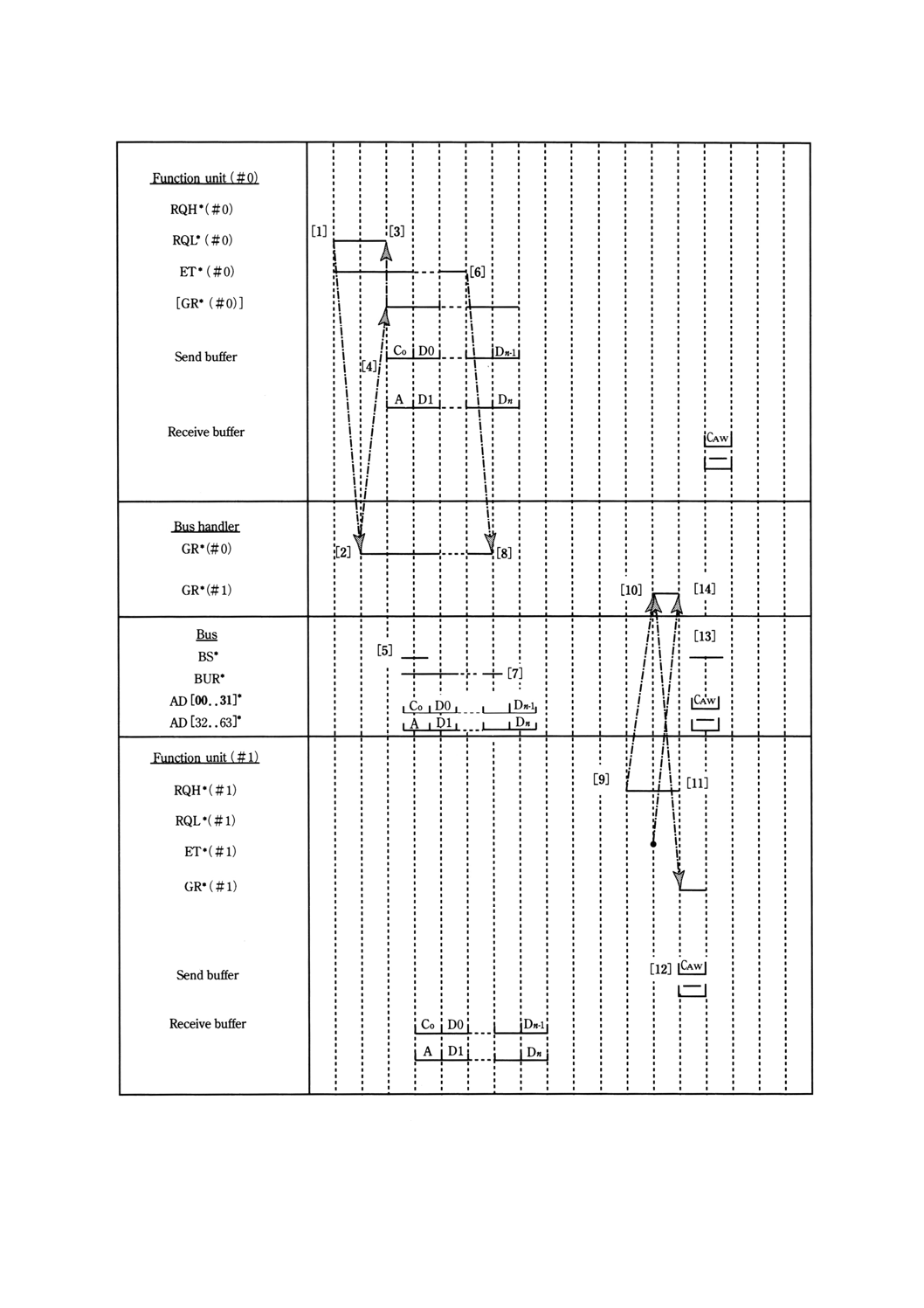

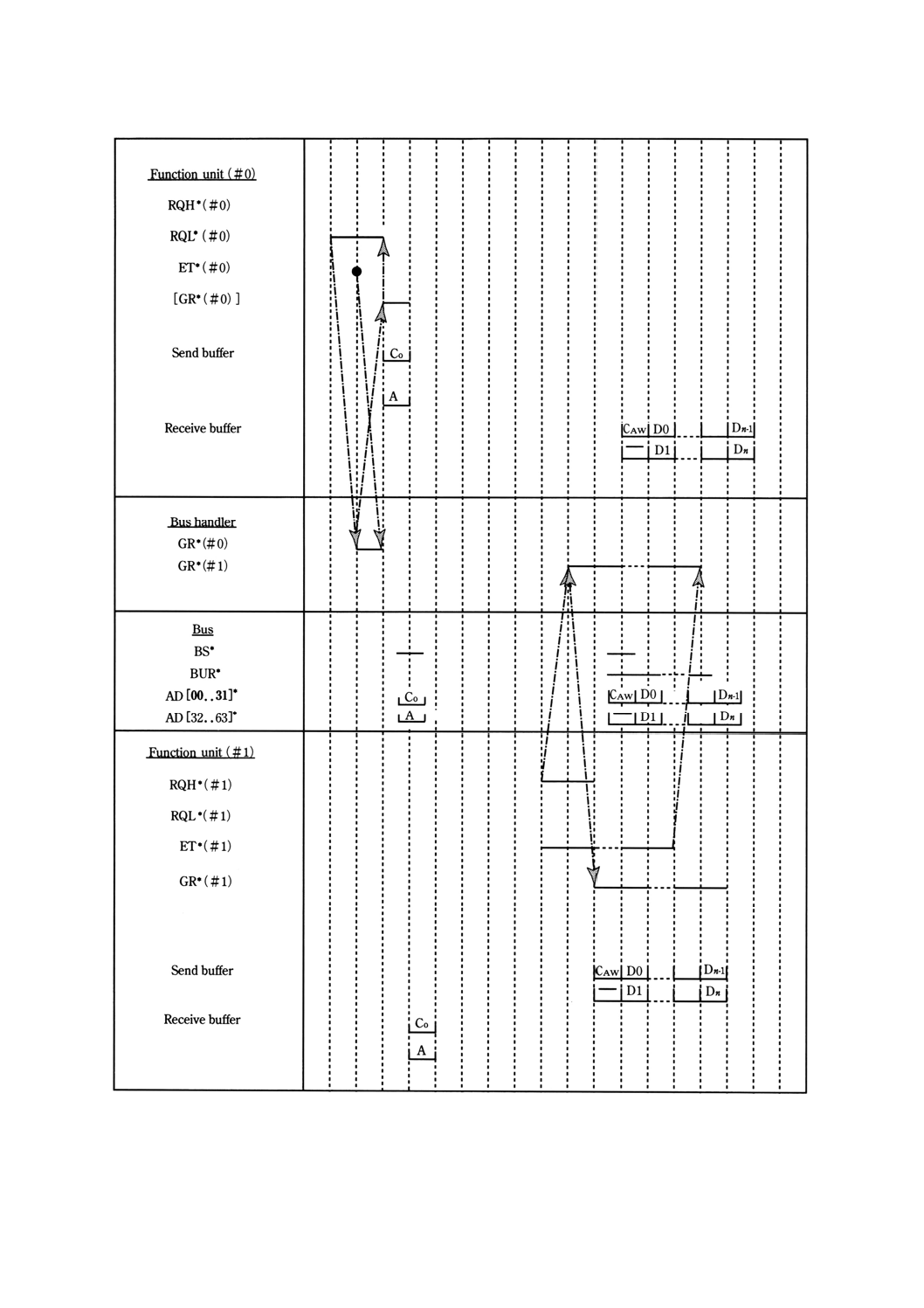

図17 キャッシュ無効化指示動作 ··························································································· 41

図18 リトライ指示動作 ······································································································ 43

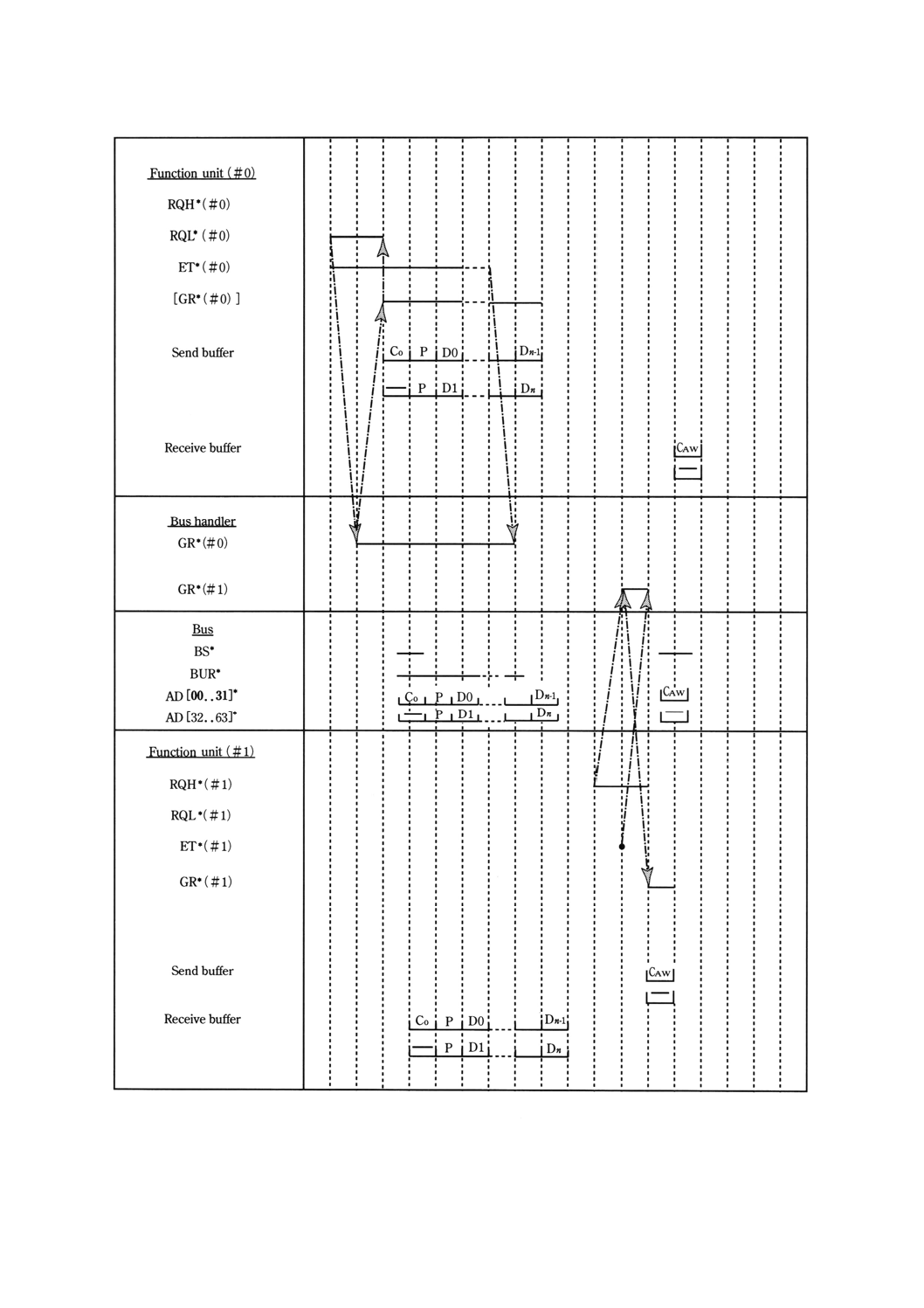

図19 リトライ指示後のコピーバック動作とスチール動作 ·························································· 45

図20 スチール禁止指示動作································································································· 47

図21 DUTで異常を検出しアンサで応答する場合 ····································································· 49

図22 機能ユニット (#0) がタイムアウトを検出したケース ························································ 50

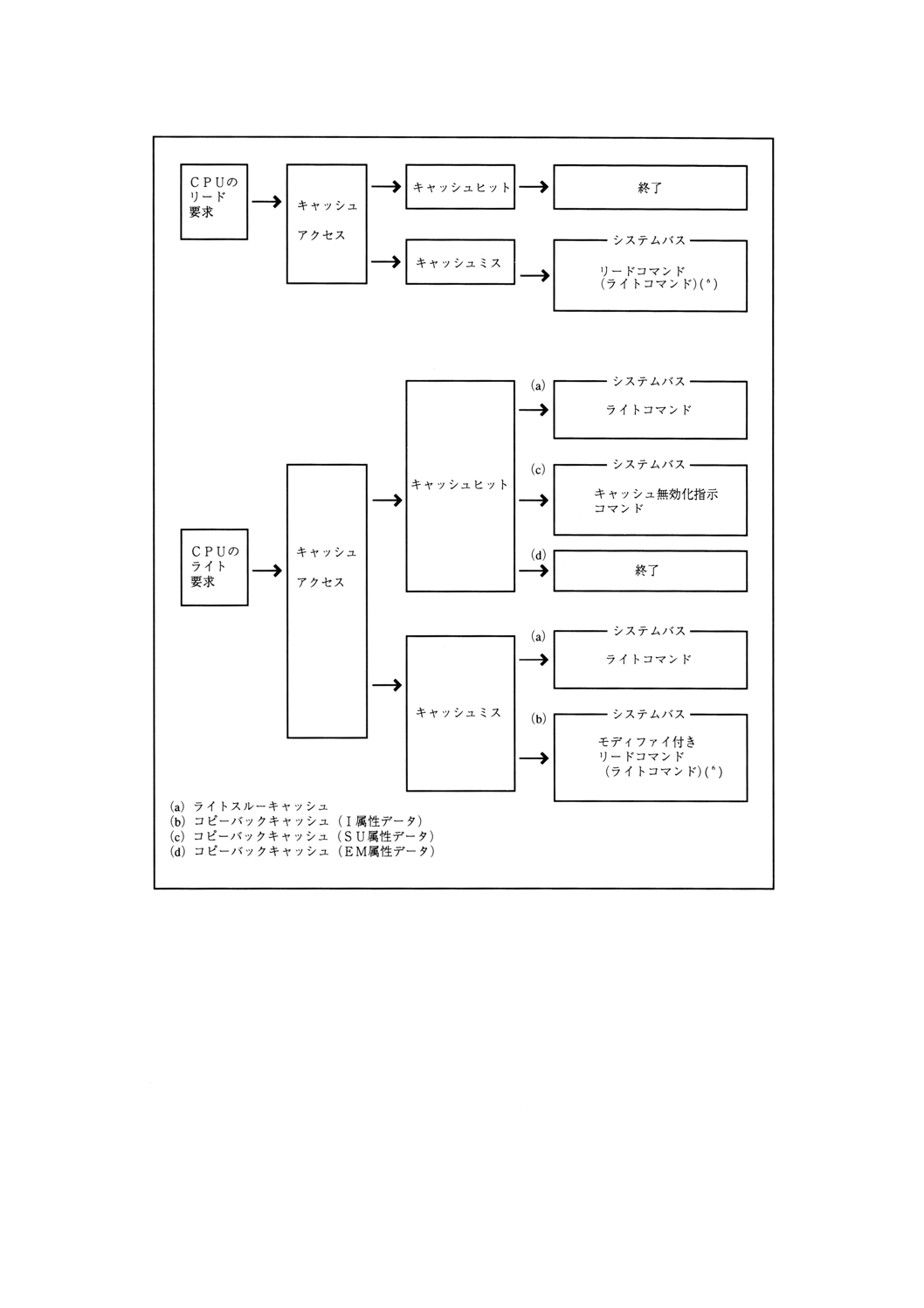

図23 CPUの動作とシステムバス上のコマンドの関係 ······························································· 52

図24 STbusのライトスルーキャッシュ一致制御プロトコル ······················································· 55

図25 STbusのコピーバックキャッシュ一致制御プロトコル ······················································· 59

表の一覧

表1 基本インタフェース信号(バスハンドラを除く機能ユニットインタフェース) ························· 4

表2 オプションインタフェース信号(バスハンドラを除く機能ユニットインタフェース) ················ 4

表3 情報転送バスのコマンドフォーマット ············································································· 11

表4 OPTコード定義··········································································································· 12

表5 Mビットの定義··········································································································· 13

表6 メッセージのシーケンス ······························································································· 15

表7 アンサコードの定義 ····································································································· 19

表8 システムバスコマンドタイプ ························································································· 51

表9 ベース信号とスペア信号が不一致した場合の意味付け ························································ 60

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

日本工業規格 JIS

X 6801 : 1998

同期スプリット転送形システムバス

(STbus) −論理仕様

Synchronous split transfer type system bus (STbus) −Logical layer

1. 概要

1.1

適用範囲 この規格は,高性能,高信頼なシステムバスであるSTbusの論理仕様を規定している。

STbusは高速クロックに同期した転送方式と,バスの無効保留時間を削減しバスを効率よく使用できるス

プリット転送方式を採用している。この規格では,主に以下の内容を規定している。

a) システムバス信号の規定

b) バスオペレーションの種別と転送プロトコル

c) コピーバックキャッシュのコヒーレンシ制御機能(共有メモリの内容と各プロセッサ内の個別メモリ

の内容との整合性を保証する機能)

d) パリティチェック機能や信号の2重化構成による障害検出機能

1.2

用途 STbusはマルチプロセッサにおける高性能なシステムバスやI/Oバスに適用できる。STbusの

適用例を図1に示す。

a) TCMPにおけるシステムバスやI/Oバス(1)

b) LCMPにおけるシステムバス(2)

注(1) TCMP: Tightly Coupled Multi−Processor system

(共有メモリと複数のプロセッサから構成され,単一OSでシステム全体が制御される

マルチプロセッサ方式)

(2) LCMP: Loosely Coupled Multi−Processor system

(各プロセッサが共有メモリ以外の媒体で結合され,各プロセッサは別のOSで動作す

るマルチプロセッサ方式)

2

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図1 STbusの用途

2. 定嚢

2.1

用語 3.以降で使用する用語の定義を,以下に述べる。

1) 機能ユニット バスに接続され,バスインタフェース制御機構をもつ各機能単位をさす。通常,1機

能ユニットが1ボードで構成される。

2) バスマスタ バス使用権を得て(バス使用許可信号がアサートされて),バスに情報を転送中である送

信元の機能ユニットをいう。

3) バススレーブ バスマスタから情報を転送される受信側の機能ユニットをいう。

4) オーダ転送 コマンドを送出して相手機能ユニットに対し,処理要求を行うための一連の情報転送を

いう。

5) アンサ転送 コマンドを受け付けた機能ユニットが,コマンドを送出した機能ユニットに対して,コ

マンドの終結状態(及び要求されたデータが付随している場合もある)及び受信状態情報をアンサ情

報として通知するための一連の転送をいう。

6) SUT (Source Unit) オーダ転送を行う機能ユニットをさす。

7) DUT (Destination Unit) アンサ転送を行う機能ユニットをさす。

8) バスハンドラ (BH) 各機能ユニットからのバス使用要求の競合を整理して複数の要求から一つの

要求を選択し,機能ユニットに対してバス使用許可を与える集中形バス制御機構である。

3

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

9) 基本信号 バスインタフェース信号のうち,システムインプリメント時に使用が義務付けられる信号

であり本信号の範囲で,異なるシステム間での互換性が保証される。

10) オプション信号 バスインタフェース信号のうち,システムインプリメント時のユーザ選択信号であ

り,採否はユーザ依存である。

11) CPU 命令の解読や命令実行機能をもつ演算素子のことを示し,マイクロプロセッサ又はマイクロプ

ロセッサ+キャッシュのことを示す。

12) I/Oアダプタ プロセッサの制御下で入出力機器の制御を行う機能ユニットをいう。

13) コピーバック方式 プロセッサ又は命令実行部からの書き込みデータを,直接外部メモリに反映せず

キャッシュ内だけを更新しておく方式。STbusのコピーバックキャッシュでは,内部3状態のキャッ

シュをサポートする。内部状態は以下の三つの異なる状態からなる。

無効状態 (I) ,共有未変更状態 (SU) 及び非共有変更状態 (EM)

14) ライトスルー方式 プロセッサ又は命令実行部からの書き込みデータを,直接メモリに反映する方式。

内部状態は,無効状態 (I) と共有未変更状態 (SU) からなる。

15) バス・スヌープ システムバス上の,外部メモリからの読み出し,外部メモリヘの書き込みを監視す

ること。

16) ブロック キャッシュメモリに登録される最小の単位。STbusでは32バイトに限定している。

17) リトライ指示動作 コピーバックキャッシュ内で変更済となり主記憶に反映していない領域に対して,

外部のデバイスがアクセスした場合に,そのアクセスを一時中断させ,再送の指示を行う動作のこと。

18) キャッシュ無効化指示動作 キャッシュ内のあるブロックの無効化を要求すること。共有未変更状態

(SU) の領域に対する書き込み動作時に,他のキャッシュ内の同一領域を無効化する場合などに使用す

る。

19) リードヒット/リードミス プロセッサからの命令又はオペランドの読み出し対象がキャッシュに登

録されている場合にリードヒット,登録されていない場合にリードミスという。リードミスの場合,

読み出し対象がキャッシュ可能な領域であれば,対象を含む1ブロックがキャッシュに新規登録され

る。

20) ライトヒット/ライトミス プロセッサからの書き込み領域がキャッシュに登録されている場合にラ

イトヒット,登録されていない場合にライトミスという。

ライトスルーキャッシュの場合には書き込みデータを即座に共有メモリへ反映する。

コピーバックキャッシュの場合,ライトヒット時は書き込みデータをキャッシュ内にだけ反映し,

ライトミス時には書き込み領域の1ブロックを共有メモリから読み込んで新規登録し,その上で書き

込みデータをキャッシュ内にだけ反映する。

21) 無効状態 (I:Invalid) プロセッサからのアクセス領域がキャッシュ上に登録されていない状態。

22) 共有未変更状態 (SU:Shared Unmodified) ライトスルーキャッシュ又はコピーバックキャッシュの

内部状態名で,アクセス領域が登録されていて,共有メモリと内容が一致している状態。複数のキャ

ッシュで共有している可能性がある。

23) 非共有変更状態 (EM:Exclusive Modified) コピーバックキャッシュの内部状態名で,共有メモリと

内容が一致していない状態。すなわち,キャッシュ内だけ更新されている状態。

24) モディファイ付きリードコマンド コピーバックキャッシュに対してプロセッサからの書き込みアク

セスがライトミスした場合に,キャッシュからシステムバスに出されるコマンドである。

25) パリティ この規格に表記しているパリティは特に明記していない場合,すべて奇数パリティを示す。

4

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ここで奇数パリティとは,対象としている信号線(例えば,8bit単位)とそのparity-bitを含めたbit

(例では8+1=9bit)において論理的に1のビットの数が偶数個(0個を含む)のときにエラーとな

ることを意味する。

26) プロセッサ 命令の解読や命令実行機能をもつ機能ユニットをいう。プロセッサではプログラムが動

作し,各種I/Oアダプタ (I/O Adapter) の制御を行う。通常,プロセッサはCPUとメモリで構成され

る。

2.2

表記 この規格では,以下に示す表記方法を用いて記述している。

・ 機能ユニット番号は (#n) で示しており,各ユニットに対する制御信号についてはRQL* (#n) ,GR*

(#n) といったように“信号線名+(機能ユニット番号)”という表記とする。

・ 制御信号の値を表記する際には,以下のように記述している。

・ 信号線の論理的な値を示す場合:1,0としアサートを1,ネゲートを0とする。

・ 信号線上の実際の値を示す場合: “H” , “L” とし “H” が高電位, “L” が低電位を示す。

・ 規格中の16進数表記は,H'##としている。(例:H'FF,H'00など)

3. インタフェース

3.1

インタフェース信号 表1に一つの機能ユニットからみた場合のSTbus基本インタフェース信号一

覧を示す。

表中RQL*,RQH*,GR*,ET*は機能ユニットごとに個別に接続される信号である。

表1 基本インタフェース信号(バスハンドラを除く機能ユニットインタフェース)

項番

信号名(3)

本数

機能分類

接続形態

1

RQL* (Request low)

1

バス権制御

個別接続

2

RQH* (Request high)

1

3

GR* (Grant)

1

4

ET* (End of bus transaction)

1

5

BS* (Bust ransaction start)

1

転送指示

バス接続

6

BUR* (Burst)

1

7

CSP* (Control signal parity)

1

8

LCK* (Lock)

1

9

AD [00..63] * (Command/address/data)

64

コマンド/アドレス/データ

10

ADP [0..7] * (AD parity)

8

11

RTY* (Retry)

1

キャッシュ一致制御

12

RST* (Reset)

1

リセット信号

13

CK (Clock)

1

クロック

(4)

信号数合計

83

注(3) 信号名の*記号は負論理であることを示す。

(4) CKの接続形態は別に規定する物理仕様を保証する構成とする。

表2に機能ユニットから見た場合のオプションのインタフェース信号線一覧を示す。

この表の信号はオプション扱いであり,システムを構築するユーザが任意に選択できる。

表2 オプションインタフェース信号(バスハンドラを除く機能ユニットインタフェース)

項番

信号名

本数

機能分類

接続形態

14

LCKS* (Lock spare)

1

転送指示

バス接続

15

RTYS* (Retry spare)

1

キャッシュ一致制御

16

STI* (Steal inhibit)

1

17

STIS* (Steal inhibit spare)

1

5

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

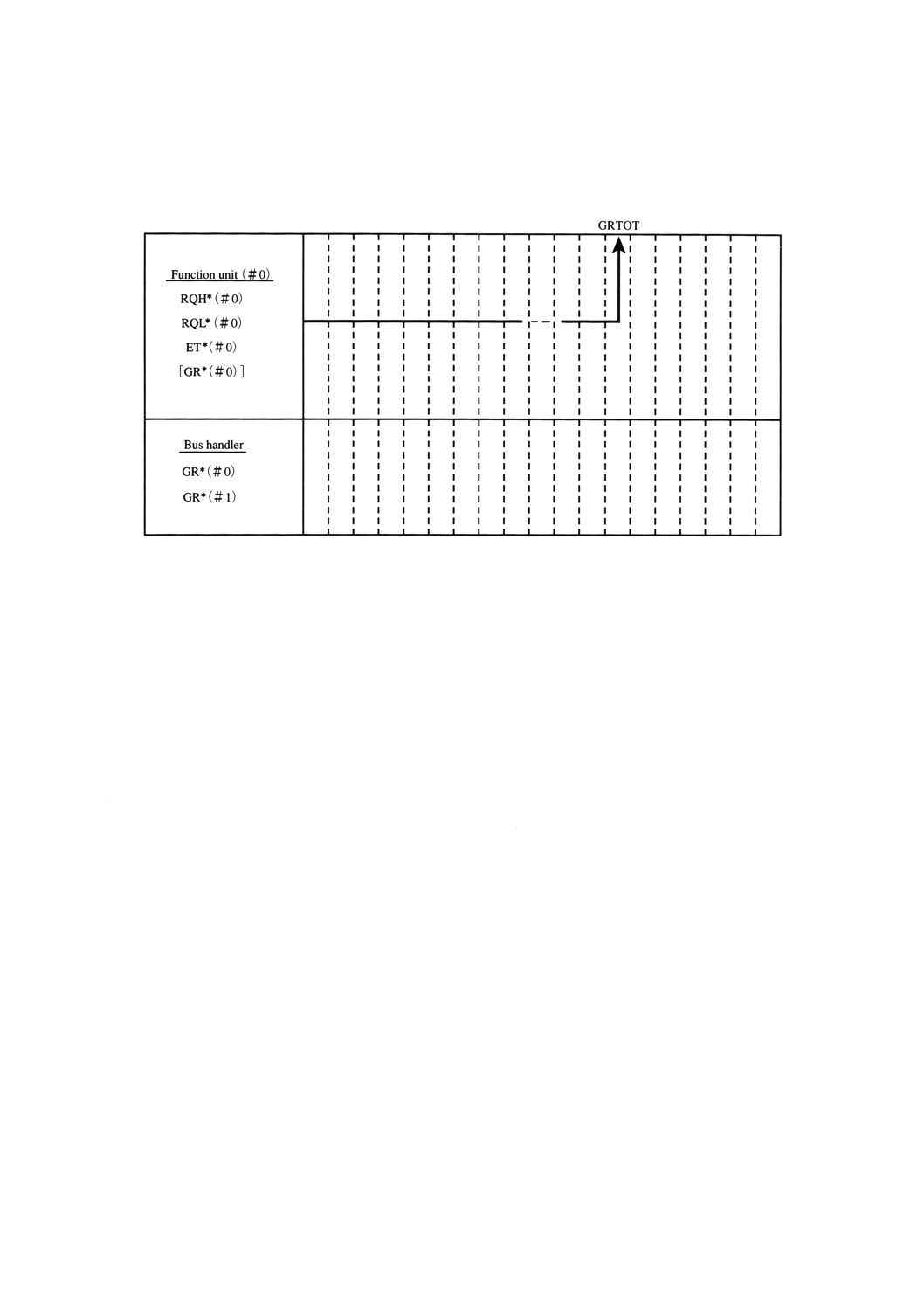

接続形態 図2にバスハンドラと各機能ユニット間の基本接続形態を示す。

備考 CKの接続については物理仕様で規定するスキューを保証可能な接続構成とする。

図2 機能ユニット間接続インタフェース(基本形)

6

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

各信号の説明

1) RQL* (Request low) SUTのバス使用要求信号である。各機能ユニットは,オーダ転送を行う場合に

本信号をアサートしてバスハンドラに対してバス使用権を要求する。バスハンドラによってバス使用

許可信号であるGR*がアサートされた機能ユニットは,本信号をネゲートしなければならない。

この信号は,各機能ユニットから個別線でバスハンドラへ通知される。

この信号はRQH*よりも優先度は低い。また,RQL*とRQH*を同時にアサートしてはならない。

2) RQH* (Request high) DUTのバス使用要求信号である。各機能ユニットは,アンサ転送を行う場合

に本信号をアサートしてバスハンドラに対してバス使用権を要求する。バスハンドラによってバス使

用許可信号であるGR*がアサートされた機能ユニットは,本信号をネゲートしなければならない。

この信号は,各機能ユニットから個別線でバスハンドラへ通知される。

この信号はRQL*よりも優先度が高い。また,RQH*とRQL*を同時にアサートしてはならない。

バスハンドラはLCK*信号がアサート中は他の機能ユニットからのRQL*に対するGR*をアサートし

ない。

ただしRQH*に対するGR*はアサートするので,どの機能ユニットもアンサ転送は実行可能である。

3) GR* (Grant) RQL*又はRQH*でバス要求したバスマスタに対するバス使用許可信号であり,本信号

がアサート中だけ各機能ユニットは転送指示,情報転送バス(表1の項番5〜7,9,10)のバスドラ

イバをイネーブルにして情報をバスに送出することができる。この信号はバスハンドラから各機能ユ

ニットに個別線で供給される。

4) ET* (End of bus transaction) バスマスタから送出する,転送データ終了を予告する信号である。

この信号はデータ転送が終了する2サイクル前にネゲートされる。

なお,RQL*やRQH*と同時にアサートしない場合には要求している転送が1サイクル転送であるこ

とを示す。

2バスサイクル以上の転送の場合,ET*はRQL*又はRQH*信号と同時にアサートされる。

この信号は各機能ユニットから個別線でバスハンドラへ通知される。

5) BS* (Bus transaction start) バス使用権を得た各機能ユニットがオーダ転送又はアンサ転送を行う場

合に,情報転送バスにコマンド又はアンサ情報を送出すると同時にこの信号をアサートし,宛先の機

能ユニットに対して転送が開始されたことを通知する。

この信号はオーダ転送又はアンサ転送の最初の1バスサイクルだけアサートされる。

最初のコマンド又はアンサ情報の送出に引き続いて,データが送出される場合の情報受信は,BS*

信号を基準にして,受信側の機能ユニットが自律的に受信する必要がある。

6) BUR* (Burst) 複数のデータ転送サイクルからなるバースト転送モードであることを示す。この信号

は送信側の機能ユニットがアサートし,アサート中は受信側の機能ユニットは継続してデータを受信

する。

この信号はデータ転送が終了する1サイクルに前にネゲートされ,受信側の機能ユニットはネゲー

トを検知した1サイクル後にデータを受信して転送動作を終了する。

BS*信号がアサートされてこの信号がアサートされない場合は,1サイクルの転送である。

7) CSP* (Control signal parity) 転送指示信号である,BS*,BRS*に対するパリティ信号である。奇数パ

リティを表す。

8) LCK* (Lock) 双方向のバスロック信号である。この信号はSUTがオーダ転送開始と同時にアサート

し,SUT自身が転送終了を指示するときにネゲートする。

7

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

システムバスはスプリット転送を基本にするが,本信号を使用してインタロック転送も可能となる。

9) AD [00..63]* (Command/Address/Data 00-63) コントロール情報,アドレス情報,データ情報が時分割

的に転送される64ビット幅の双方向の情報転送バスである。

10) ADP [0..7]* (AD Parity 0-7) AD [00..63] *のバイトごとのパリティ信号である。奇数パリティを表す。

11) RTY* (Retry) TCMPのキャッシュ制御方式がコピーバックキャッシュのときの一致制御に使用され

る信号である。この信号がアサートされた場合,バスマスタは現在の転送の再送を行う必要がある(5.4

参照)。

12) RST* (Reset) STbusに接続するある機能ユニットから他の機能ユニットへリセットを指示する。こ

の信号は有効な期間アサートしつづける。

13) CK (Clock) STbusの共通クロック信号である。バス動作はこの信号の立ち下がりに同期して行われ

る。

14) LCKS* (Lock spare) LCK*信号のスペア信号である。この信号を使用する場合,LCK*信号も同時に使

用しなければならない。LCK*信号とこの信号のどちらか一方の信号がアサートされた場合,ロック転

送は行われない。LCK*信号とLCKS*信号の両方がアサートされたときだけロック転送を実行する。こ

の信号はオプションである。

15) RTYS* (Retry spare) RTY*信号のスペア信号である。この信号を使用する場合,RTY*信号も同時に使

用しなければならない。

RTY*信号とこの信号のどちらか一方の信号がアサートされた場合,バスマスタは現在の転送の再送

を行う必要がある。この信号はオプションである。

16) STI* (Steal inhibit) コピーバックキャッシュ一致制御の場合に使用される信号である。この信号は各

機能ユニット間でだけ接続される。この信号はオプションである。

この信号がアサートされた場合,バスマスタは当該データのコピーバック時のスチール動作が禁止

される。この信号の詳細は5.5スチール動作を参照のこと。

17) STIS* (Steral inhibit spare) STLI*信号のスペア信号である。この信号を使用する場合,STLI*信号も同

時に使用しなければならない。STLI*とこの信号のどちらか一方の信号がアサートされた場合,バスマ

スタは当該データのコピーバック時のスチール動作が禁止される。この信号はオプションである。

4. バス動作説明

4.1

基本動作プロトコル 以下に,STbusの基本動作例(1−サイクル転送,2−サイクル転送)及び動

作説明を示す。

8

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図3 バス動作プロトコルの概念(1−サイクル,2−サイクル転送時:バス幅8バイトで,かつライト動

作)

各機能ユニット及びバスハンドラはすべて共通クロックCKに同期して動作する。

[1] 上図では機能ユニット (#0) が機能ユニット (#1) に対して2-wordの情報転送を行う場合を示してい

る。まずバス使用要求信号RQL* (#0) をアサートし,バスハンドラにバス権獲得要求を行う。転送語

数が2-wordのため同時に転送終了予告信号ET* (#0) をアサートする。

[2] バスハンドラはRQL* (#0) 信号が受付け可能になると機能ユニット (#0) に対するバス使用許可信号

GR* (#0) をアサートして,機能ユニット (#0) にバス使用権を与える。

[3] バス使用権を獲得した機能ユニット (#0) は,GR* (#0) アサートによってRQL* (#0) 信号をネゲート

する。

[4] 上記と同時に機能ユニット (#0) はGR* (#0) を受けて情報転送バスを有効化して情報をバス上に送出

する。情報転送時の最初のサイクルで転送制御信号のBS*信号をアサートする。

[5] 上記例の場合,2-wordの情報転送を行うため,BS*と同時にBUR*信号をアサートしバースト転送開始

を他の機能ユニットに対して通知する。BUR*信号は転送終了の1サイクル前にネゲートする。

[6] GR* (#0) と同時にアサートしたET* (#0) は転送終了の2サイクル前にネゲートすることで,バスハン

ドラに対して事前にバスが開放されることを通知する。

[7] ET* (#0) のネゲートを検出したバスハンドラはGR* (#0) をネゲートする。

[8] 機能ユニット (#0) からの情報に対してアンサ情報 (1-word) を返送する場合,機能ユニット (#1) は

バス使用要求信号RQH* (#1) をアサートしバスハンドラにバス権獲得要求を行う。アンサ転送で転送

語数が1-wordの場合にはET* (#1) はアサートしない。

[9] バスハンドラはRQH* (#1) 信号が受付け可能になると機能ユニット (#1) に対するバス使用許可信号

GR* (#1) をアサートする。

[10] バス使用権を獲得した機能ユニット (#1) は,GR* (#1) によってRQH* (#1) 信号をネゲートする。

[11] 上記と同時に機能ユニット (#1) はGR* (#1) を受けて情報転送バスを有効化して情報をバス上に送出

する。情報転送時の最初のサイクルで転送制御信号のBS*信号をアサートする。このとき,転送語数

9

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

が1-wordであるためBUR*信号はアサートしない。

[12] RQH* (#1) 及びET* (#1) がネゲートしているため,バスハンドラは1-word転送でGR* (#1) をネゲー

トする。なお,スプリット転送方式を採用しているため,上記[7]〜[9]間は他の機能ユニット間でバス

使用可能となる。以下に,STbusの基本動作例(3−サイクル以上の転送時)を示す。

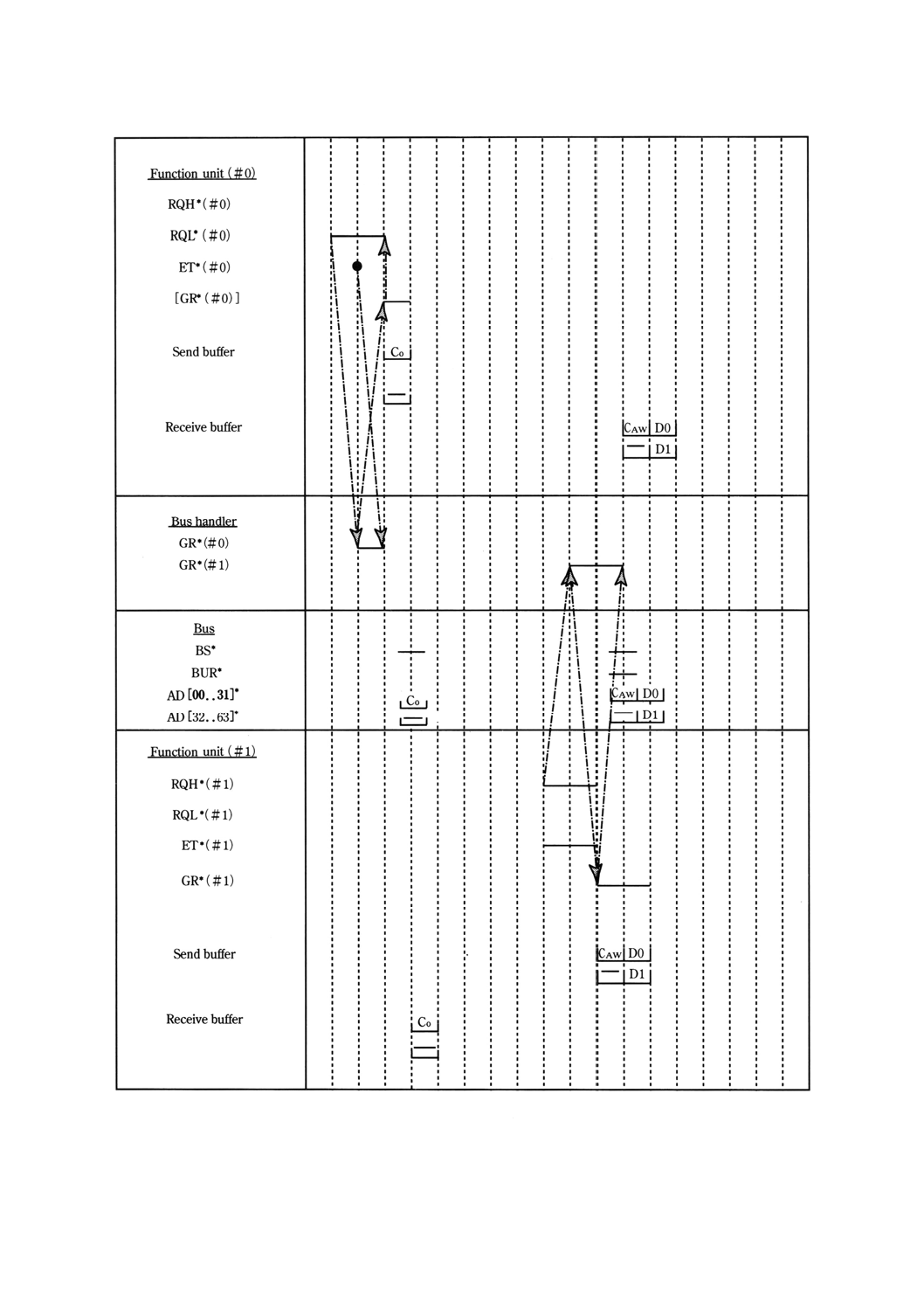

図4 バス動作プロトコルの概念(3−サイクル以上の転送時:バス幅8バイトで,かつリード動作)

[1] 上図では機能ユニット (#0) が機能ユニット (#1) に対して1-wordの情報転送を行う場合を示してい

る。まずバス使用要求信号RQL* (#0) をアサートし,バスハンドラにバス権獲得要求を行う[転送語

数1-wordのためET* (#0) はアサートしない。]。

[2] バスハンドラはRQL* (#0) 信号が受付け可能になると機能ユニット (#0) に対するGR* (#0) をアサー

トして機能ユニット (#0) にバス使用権を与える。

[3] バス使用権を獲得した機能ユニット (#0) は,GR* (#0) のアサートによってRQL* (#0) 信号をネゲー

トする。

[4] 上記と同時に機能ユニット (#0) はGR* (#0) を受けて情報転送バスを有効化して情報をバス上に送出

する。情報転送時の最初のサイクルで転送制御信号のBS*信号をアサートする。

上記例の場合,転送語数1-wordのためBUR* (#0) はアサートしない。

[5] RQL* (#0) 及びET* (#0) がネゲートされているため,バスハンドラはGR* (#0) を1サイクルでネゲー

トする。

[6] 機能ユニット (#0) の情報に対して3-word以上の情報を返送する場合,機能ユニット (#1) はRQH*

(#1) をアサートしてバス権獲得要求を行う。複数word転送のためET* (#1) も同時にアサートする。

[7] バスハンドラはRQH* (#1) 信号が受付け可能になると機能ユニット (#1) に対するバス使用許可信号

GR* (#1) をアサートする。

[8] バス使用権を獲得した機能ユニット (#1) は,GR* (#1) によってRQH* (#1) 信号をネゲートする。

[9] 上記と同時に機能ユニット (#1) はGR* (#1) を受けて情報転送バスを有効化して情報をバス上に送出

する。情報転送時の最初のサイクルで転送制御信号のBS*信号をアサートする。このとき,転送語数

が3-word以上であるためBUR*信号をアサートする。

10

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

[10] 上記例の場合,3-word以上の情報転送を行うため,BS*と同時にBUR*信号をアサートしバースト転送

開始を他の機能ユニットに対して通知する。BUR*信号は転送終了の1サイクル前にネゲートする。

[11] GR* (#1) と同時にアサートしたET* (#1) は転送終了の2サイクル前にネゲートすることで,バスハン

ドラに対して事前にバスが開放されることを通知する。

[12] バスハンドラはET* (#1) 信号のネゲートを監視し,確認した時点でGR* (#1) 信号をネゲートする。

以下に,バス幅が4バイトの場合の動作例(1−サイクル,2−サイクル転送)を参考に示す。

図5 バス動作プロトコルの概念(1−サイクル,2−サイクル転送時:バス幅4バイトで,かつライト動

作)

情報転送バス幅4バイトの場合に,機能ユニット (#0) が機能ユニット (#1) に対して2-wordの情報を

転送する動作は基本的に8バイト幅のときと同じである。

ただし情報転送バス幅が4バイトのため,8バイト幅1サイクルの情報を2サイクルで転送することに

なり上図のようになる。

各信号の変化点に対する解説は,8バイト仕様時と同じである。

4.2

転送プロトコル

4.2.1

バスオペレーションの種別 STbusにおけるバスオペレーションは,次の4種類に大別される。

1) メモリアクセス 任意の機能ユニットが,共有メモリ又は他の任意の機能ユニットの個別メモリへの

リード/ライトを行う場合に使用されるバスオペレーションである。バス基本仕様では転送単位とし

て最大256バイトまで任意のバイト数指定が可能である。

2) 制御空間アクセス 任意の機能ユニットで走行するプログラムが,他の任意の機能ユニットの制御空

間にマッピングされたデータを直接リード/ライトする場合に使用されるバスオペレーションである。

バス基本仕様では転送単位として最大256バイトまで任意のバイト数指定が可能である。

3) メッセージ転送 任意の機能ユニットが,他の任意の機能ユニットへメッセージ転送を行う場合に使

用されるバスオペレーションである。

4) 制御レジスタアクセス 任意の機能ユニットで走行するプログラムが,他の任意の機能ユニットの制

御レジスタ類(最大256個まで)を8バイト以内で直接リード/ライトする場合に使用されるバスオ

ペレーションである。

11

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.2.2

コマンドフォーマット 情報転送バスは64ビット幅(又は32ビット幅)でありエンディアンには

ビッグエンディアンを採用して,MSBからAD [00..63] *(又はAD [00..31] *)の並びとする。

また,情報転送バスはバイト単位に分割し,MSB側から第0バイト〜第7バイトとする。

転送される情報は,コマンド,アドレス,データ及びメッセージ通信オペランドの4種類に大別される。

情報転送においては,コマンドが最初に相手機能ユニットに送出される。そのフォーマットを表3に示

す。

表3に具体的に記載されていないが,上述のバイト単位にパリティ1ビットが付与される。

表3 情報転送バスのコマンドフォーマット

情報転送バスの内容

第0バイト

第1バイト

第2バイト

第3バイト

OPT

0

OPT

1

OPT

2

00

01……07

08

09……15

16

17

18

19 20

21

22 23

24……31

メモリアクセス

0

BMID

0

BSID

0

BT R/W A64 M NAT AID

BCT

制御空間アクセス

0

BMID

0

BSID

1

BT R/W A64 0 NAT AID

BCT

メッセージ転送

0

BMID

1

BSID

0

BT MD

SQ

NAT AID

BCT

制御レジスタアクセス

0

BMID

1

BSID

1

BT R/W

BCT

AID

RA

Reserved

1

BMID

0

BSID

0

BT

*

*

*

*

* * * * * * * * * *

Reserved

1

BMID

0

BSID

1

BT

*

*

*

*

* * * * * * * * * *

Reserved

1

BMID

1

BSID

0

BT

*

*

*

*

* * * * * * * * * *

アンサ

1

BMID

1

BSID

1

BT

ROPT

RNAT

RAID

ANS

[略号の説明]

OPT:Operation Type

BCT:Byte Count

BMID:Bus Master ID

MD:Mode

BSID:Bus Slave ID

SQ:Sequence

BT:Bus Type

RA:Register Address

R/W:Read/Write

ROPT:Return Operation Type

A64:64-bit Address Space

RNAT:Return NAT

M:Modify

RAID:Return Access ID

NAT:No-Answer Transaction

ANS:Answer code

AID:Access ID

* :Reserved

1) オペレーションタイプコード コマンドには,SUTからDUTへのオーダ転送用とDUTからSUTへ

のアンサ転送用の2種類がある。コマンドはReservedも含めて8タイプある。これらを総称してオペ

レーションタイプと呼び,情報転送バスの第0バイトのbit0,第1バイトのbit8及び第2バイトのbit16

の合計3bitでOPT (Operation Type) コードを定義する。

12

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表4 OPTコード定義

OPT

オペレーションタイプ

0

1

2

0

0

0

メモリアクセス

0

0

1

制御空間アクセス

0

1

0

メッセージ転送

0

1

1

制御レジスタアクセス

1

0

0

Reserved

1

0

1

Reserved

1

1

0

Reserved

1

1

1

アンサ

2) ID (Identifier) とパスタイプ (BT:Bus Type) コマンド転送の場合,情報転送バスの第0バイト,第

1バイトにBMID (Bus Master Identifier) ,BSID (Bus Slave Identifier) が送出される。

第2バイトのbit17は,BT (Bus Type) を示す。

各フィールドの意味を下記に示す。

BMID (Bus Master Identifier)

バスマスタの機能ユニットIDを示す。7ビットからなる。

BSID (Bus Slave Identifier)

バススレーブの機能ユニットIDを示す。7ビットからなる。

BT (Bus Type)

0:4バイトバス

1:8バイトバス

3) メモリアクセス 各フィールドの意味を下記に示す。

R/W (Read/Write)

0:SUTがDUTへ書き込みを行う動作である。

1:SUTがDUTから読み出しを行う動作である。

A64 (64bit Address Space)

0:アドレス空間が32ビット空間である。

1:アドレス空間が64ビット空間である。

M (Modify)

この信号はTCMP構成時のプロセッサのキャッシュの一致制御に使用する。

R/Wとの組合せによって使用する。表5に動作を規定する。

13

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表5 Mビットの定義

R/W

M(5)

バスの動作

0

0

メモリ書き込み動作

1

キャッシュの無効化指示

1

0

メモリ読み出し動作

1

メモリ読み出し動作及びキャッシュの無効化指示

R/Wフィールドが “0” で,Mフィールドが “1” の場合,BCTフィールドは無効となり,

バス上に転送されるものはコマンド,アドレスだけである。

メモリヘの書き込みも行わない。他の機能ユニットのキャッシュにヒットした場合,キャ

ッシュを無効化する。

注(5) コピーバックキャッシュをサポートしない場合は,Mフィールドは “0” とすること。

AID (Access Identifier)

メモリアクセス多重動作を行うための識別子として使用する。

使用用途は複数のDMAポートの同時動作や,単一DMAポートのパイプライン動作などである。

スプリット転送でのメモリアクセス多重動作の例を図6に示す。

図6 パイプライン動作

NAT (No̲Answer Transaction)

これから行う転送を突き放し転送(アンサを伴わない転送)によって行うことを指示する。

スレーブ側はこのビットが設定されたコマンド転送に対してアンサ転送を行わない。

コマンド転送時にエラーが発生した場合には,エラーを示すアンサをスレーブからマスタに返

送する。

0:アンサのある転送

1:突き放し転送

14

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

BCT (Byte Count)

SUTからDUTへ転送するバイト数(ライト時),又はDUTからSUTへ返送するバイト数(リ

ード時)を指定する。図7 a)にBCTフィールドの定義を示す。

1回のバスオペレーションでは,最大256バイトまで連続転送が可能である。

t= “00” のとき,バス上に転送される有効バイト数はBCTの内容に1を加えたものと一致しな

ければならない。例えば,t= “00” &n= “00000” の場合は1バイト転送であり,t= “00” &n=

“11111” の場合は32バイト転送となる。バイトアラインメントは8バイトバスの場合,アドレス

の下位3ビットの値とBCTの内容によって実現される。アドレスの下位3ビットで決定する第1

ワードのデータのバイト位置から,BCTで決定するバイト数が有効データとなる。アドレスが8n

+3でBCTがt= “00” &n= “11111” &w= “0” (32バイト転送)の場合の有効データを図7 b)に

示す。

転送時の各データについてはInvalidなものについても正当なparityをつけるようにする。

w= “1” の場合(一般にブロック転送時に使用する),ブロック境界においてラップアラウンド

する。例えば,アドレスが8n+3でBCTがt= “00” &n= “11111” &w= “1” の場合,有効データ

は図7 c)に示すとおりである。

図7 BCTフィールド

15

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4) 制御空間アクセス 各フィールドの意味を下記に示す。

R/W (Read/Write)

:メモリアクセスに同じ。

A64 (64bit Address Space)

:メモリアクセスに同じ。

AID (Access Identifier)

:メモリアクセスに同じ。

NAT (No−Answer Transaction)

:メモリアクセスに同じ。

BCT (Byte Count)

:メモリアクセスに同じ。

(BCTとアドレスの関係もメモリアクセスと同じである。)

5) メッセージ転送 各フィールドの意味を下記に示す。

MD (Mode)

:メッセージにおける処理の緊急度の違いを示す。

0:緊急メッセージ

1:一般メッセージ

SQ (Sequence)

:表6に従ってメッセージの意味を規定する。

表6 メッセージのシーケンス

SQ

意味

内容

20

21

0

0

Single

メッセージ長が256バイト以下であり,1回のバスオペレーションによ

って転送が終了することを示す。受信側は,本バスオペレーションの

受付けによって,プロセッサにメッセージ受信完了を通知できる。

0

1

First

メッセージ長が256バイトを超える場合の最初のバスオペレーション

を示す。受信側は引き続くバスオペレーション受信待機状態に入る。

1

0

Middle

First又はMiddleに継続するメッセージであることを示す。Middle受信

時に,受信側は次のメッセージ受信待機状態になり,バスオペレーシ

ョンを受信するとBMID,AIDが同一であることを確認後,そのバス

オペレーションを受け付け,さらに次のバスオペレーション受信待機

状態に入る。

1

1

Last

First又はMiddleに継続するメッセージであり,受信側の動作はMiddle

受信と同様であるが最終メッセージであることを示す。これを受け付

けた場合,プロセッサにメッセージ受信完了を通知できる。

NAT (No−Answer Transaction) :メモリアクセスに同じ。

BCT (Byte Count)

:メモリアクセスに同じ。ただし,このコマンドではアドレスは転

送されないため,データの第1ワードのバイト0よりBCTで指

定されたデータが有効となる。

備考 メッセージ転送パラメータ:メッセージ転送パラメータは,メッセージ通信コマンドに継続し

て転送される8バイトの付加情報である。オペランドの内容としては,サブシステム間通信を

行う場合のサブシステムIDなどがある。詳細内容に関してはユーザ開放とする。

6) 制御レジスタアクセスコマンド 各フィールドの意味を下記に示す。

R/W (Read/Write)

:メモリアクセスに同じ。

BCT (Byte Count)

:転送すべきデータのバイト数を指定する。1回のバスオペレーシ

ョンで8バイトまで指定できる。

バス上に転送される有効バイト数は,BCTの内容に1を加えた

ものと一致しなければならない。例えば,BCT=H'7の場合8バイ

ト転送となる。

16

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

RA (Register Address)

:レジスタアドレスを指定する。

バイトアラインメントはRAの下位3ビットの値とBCTの内容

によって定義される。RAの下位3ビットで決定する第1ワードの

データのバイト位置からBCTで決定するバイト数が有効データと

なる。

例えば,RAが8n+3でBCTが6(7バイト転送)の場合の有効

データを図8に示す。

バイト位置

0

1

2

3

4

5

6

7

データ第1ワード

I

I

I

V0

V1

V2

V3

V4

データ第2ワード

V5

V6

I

I

I

I

I

I

Vi:有効

I:無効

図8 RAとバイトアラインメント

7) アンサ アンサコマンドはアンサ転送において,DUTがSUTに対し最初に返送する情報である。

BMID及びBSIDのペアの組合せはコマンドと同じであるが,バスマスタがDUTであるので,BMID

=DUTの機能ユニットID,BSID=SUTの機能ユニットIDとなる。

各フィールドの意味を下記に示す。

ROPT (Return Operation Type)

SUTからDUTへオーダ転送されたOPTコードを埋め込む。

RNAT (Retum NAT)

オーダ転送で指定されたNATをこのフィールドに埋め込む。

RAID (Retum Access Identifier)

オーダ転送で指定されたAIDを埋め込む。

ANS (Answer Information)

アンサ情報であり,8ビットで構成される。オーダ転送において要求された動作の終結状態が

示される。一部のフィールドはバススレーブ側での受信状態を示す情報を規定するために使用さ

れる。それ以外の内容定義はユーザ開放である。

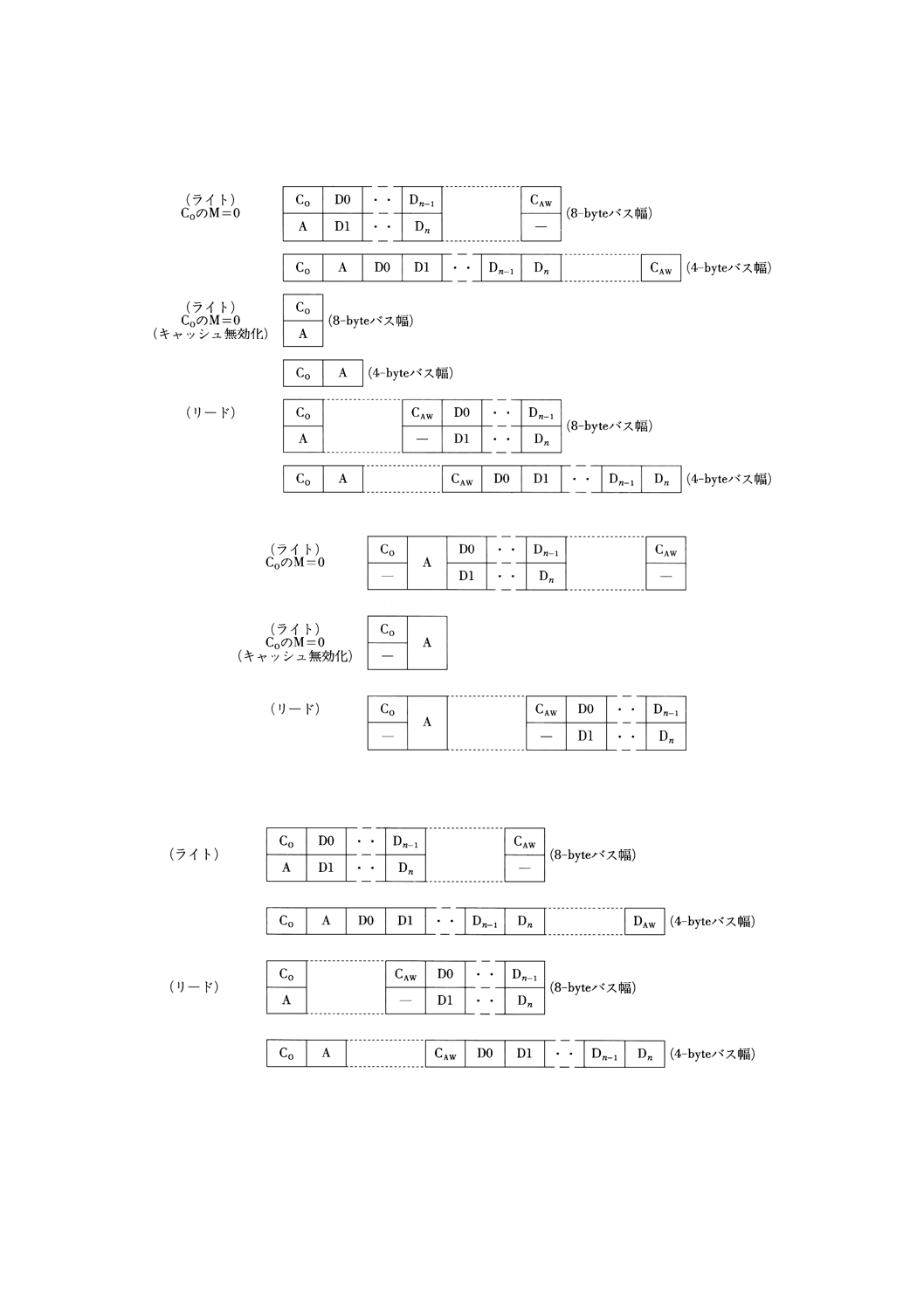

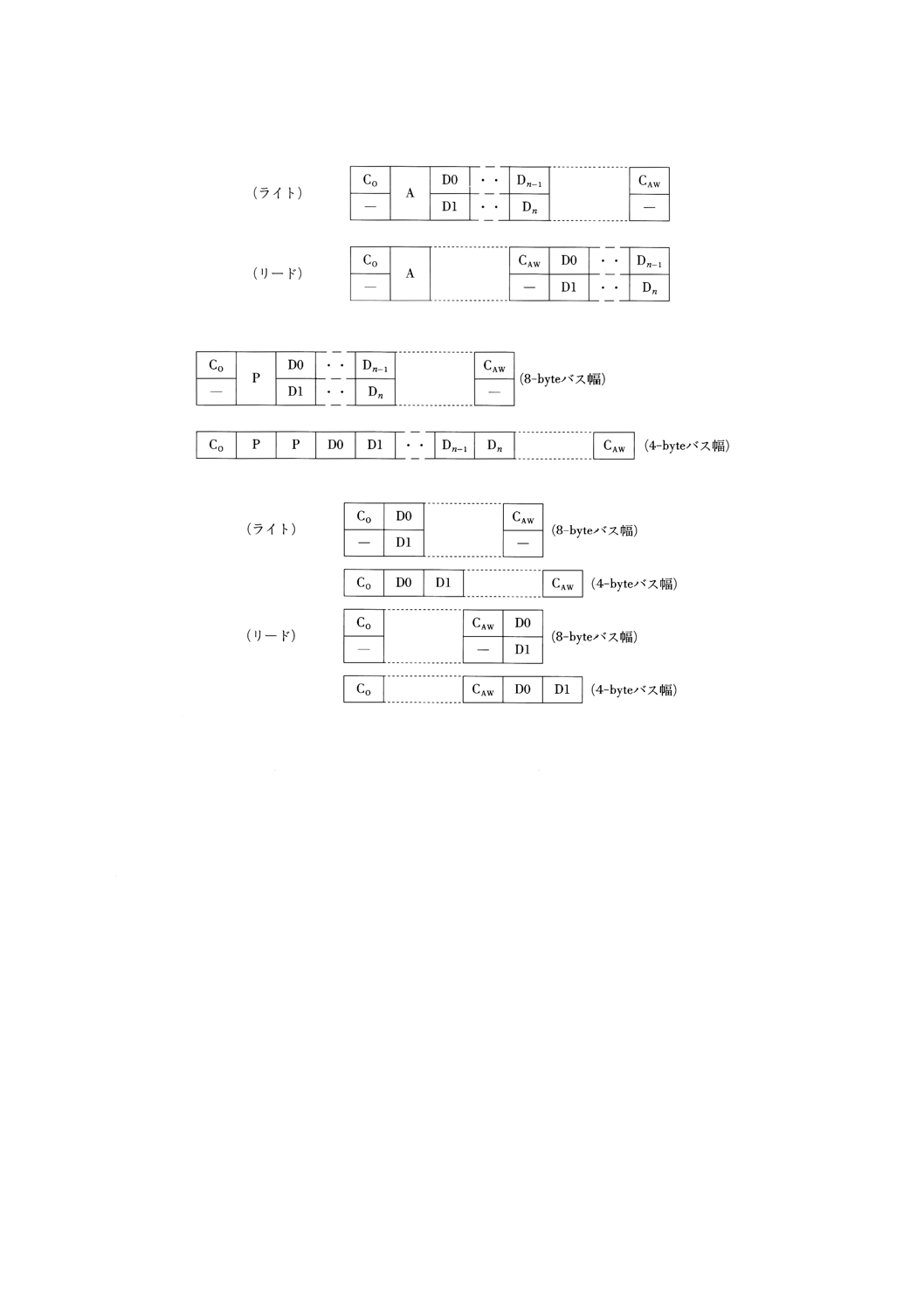

4.2.3

転送シーケンス このシーケンスは固定的であり,コマンドの種類によってバスの動作シーケンス

が決定される。

以下のシーケンス図中に用いられる枠内記号の意味は,以下のとおりである。

Co:オーダコマンド(オーダ転送)

Di:データ

CAW:アンサコマンド(アンサ転送)

A:アドレス

P:パラメータ

17

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

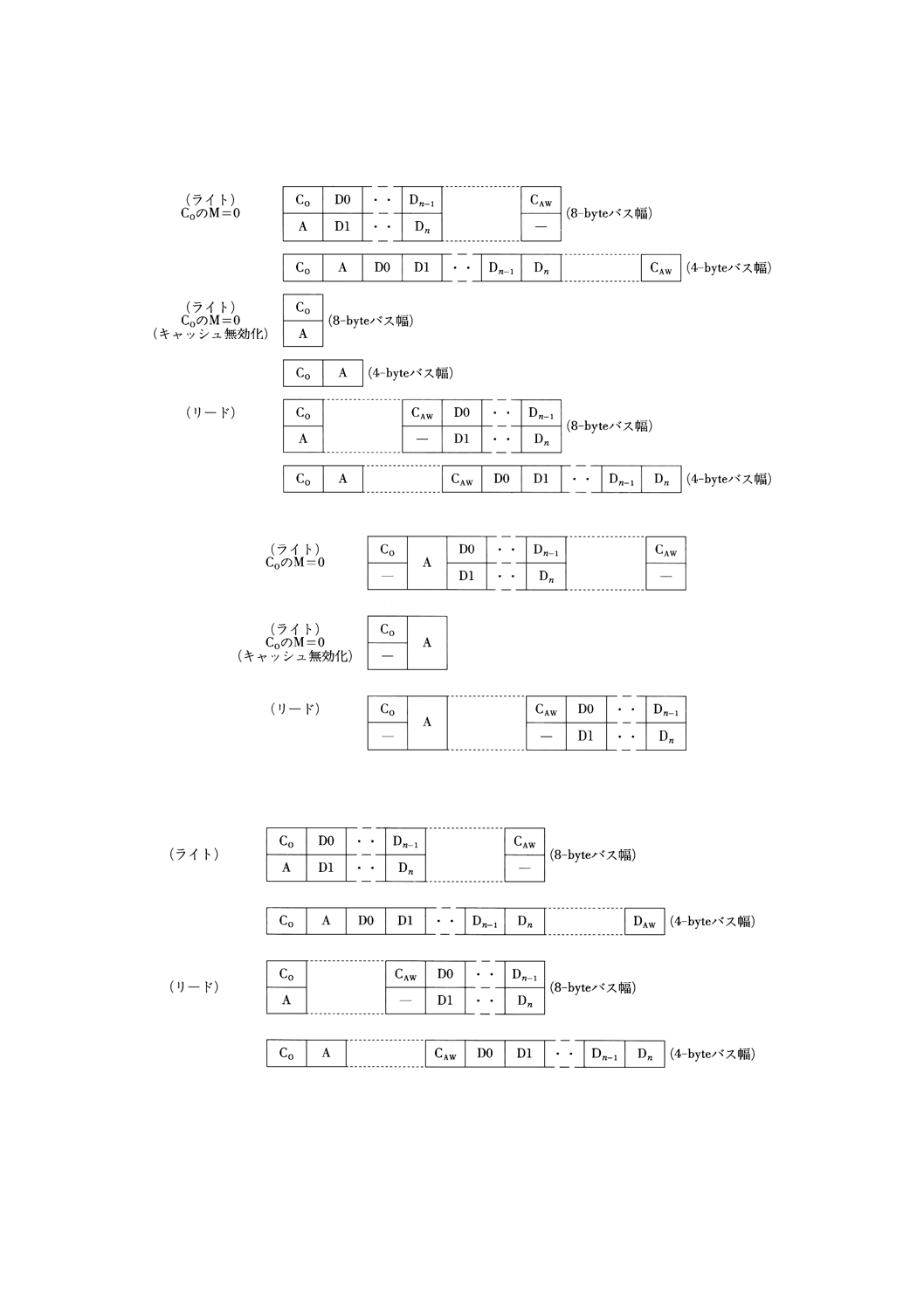

1) メモリアクセス

a) 32ビットアドレッシングの場合

b) 64ビットアドレッシングの場合(8-byteバス幅)

2) 制御空間アクセス

a) 32ビットアドレッシングの場合

18

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

b) 64ビットアドレッシングの場合(8-byteバス幅)

3) メッセージ転送

4) 制御レジスタアクセス

4.3

アービトレーション STbusのアービトレーションは3.1 インタフェース信号で示した構成のバス

ハンドラによって行われる集中アービトレーションである。各ユニットからの2種のバス使用要求線によ

って,バスハンドラに要求される。バスハンドラはこれらの要求に対し,バス使用許可信号を通知する。

アービトレーション制御信号の取扱いについては,システム構成によって信号変化をスルーで使用する

場合(比較的小さな範囲での制御)と動作クロック単位で信号レベルを確認して制御する場合(広い範囲

にわたる制御)とに分けられる。どちらを採用するかはユーザ依存とする。

優先制御のアルゴリズムに関しては,STbusでは規定しない。

4.4

受信状態報告 アンサ転送によって報告される“バススレーブ側における転送データの受信状態”

の情報をこの項で規定する。

アンサ転送によるバススレーブからバスマスタへの状態報告は,オーダ転送に対する状態通知を行うた

めのものであり,以下のようにアンサフィールド内ビットを用いて定義される。

19

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表7 アンサコードの定義

アンサコードの値

意味付け

ニーモニック

0

1

2

3

4

5

6

7

0

0

0

0

0

0

0

0

No error

システム管理者用

0

0

0

0

0

1

No error (Lock transfer)

(エラーがない場合)

0

0

0

0

1

0

Reserved

…

…

1

1

1

1

1

1

Reserved

1

0

0

0

0

0

0

User dependent

ユーザ用

…

…

…

…

(エラーがない場合)

1

1

1

1

1

1

User dependent

1

0

0

0

0

0

0

0

Hardware error

システム管理者が使用する

0

0

0

0

0

1

Illegal command

エラー規定

0

0

0

0

1

0

Bus sequence error

0

0

0

0

1

1

Reserved

…

…

…

…

1

1

1

1

1

1

Reserved

1

0

0

0

0

0

0

User dependent

ユーザが使用できる

…

…

エラー規定

1

1

1

1

1

1

User dependent

1) No error

2) No error

(Lock transfer)

3) Hardware error

4) Illegal command

5) Bus sequence error

:

:

:

:

:

DUTが正しくオダを受信したことを示す。

ロック転送において,DUTが正しくオーダを受信したことを示す。

DUT側でバス信号のパリティ異常が検出されたことを示す。

オーダ転送の場合,受付け不可能なバスオペレーションを受信したこ

とを示す。例えば,サポートしていないOPTやBTなどを受信した場

合に返送される。

SUTが送出したデータ量とオーダコマンドで指定した転送データ量

にDUT側で不一致を検出したことを示す。又は,BS*が2サイクル以

上アサートされたことを示す。

4.5

データ転送 この節では,各バスオペレーションにおける動作内容を規定する。

メモリアクセスのライト動作を例に詳細を説明し,その他のバスオペレーションについては概要だけ説

明する。この節で記述されている動作シーケンスは32ビットアドレッシングの場合である。64ビットア

ドレッシング時のシーケンスはこの節の動作シーケンスと併せて4.2.3 転送シーケンスを参照されたい。

なお,この節では正常動作シーケンスについてだけ説明する。転送中の異常動作のシーケンスについて

は4.8 異常処理を参照のこと。

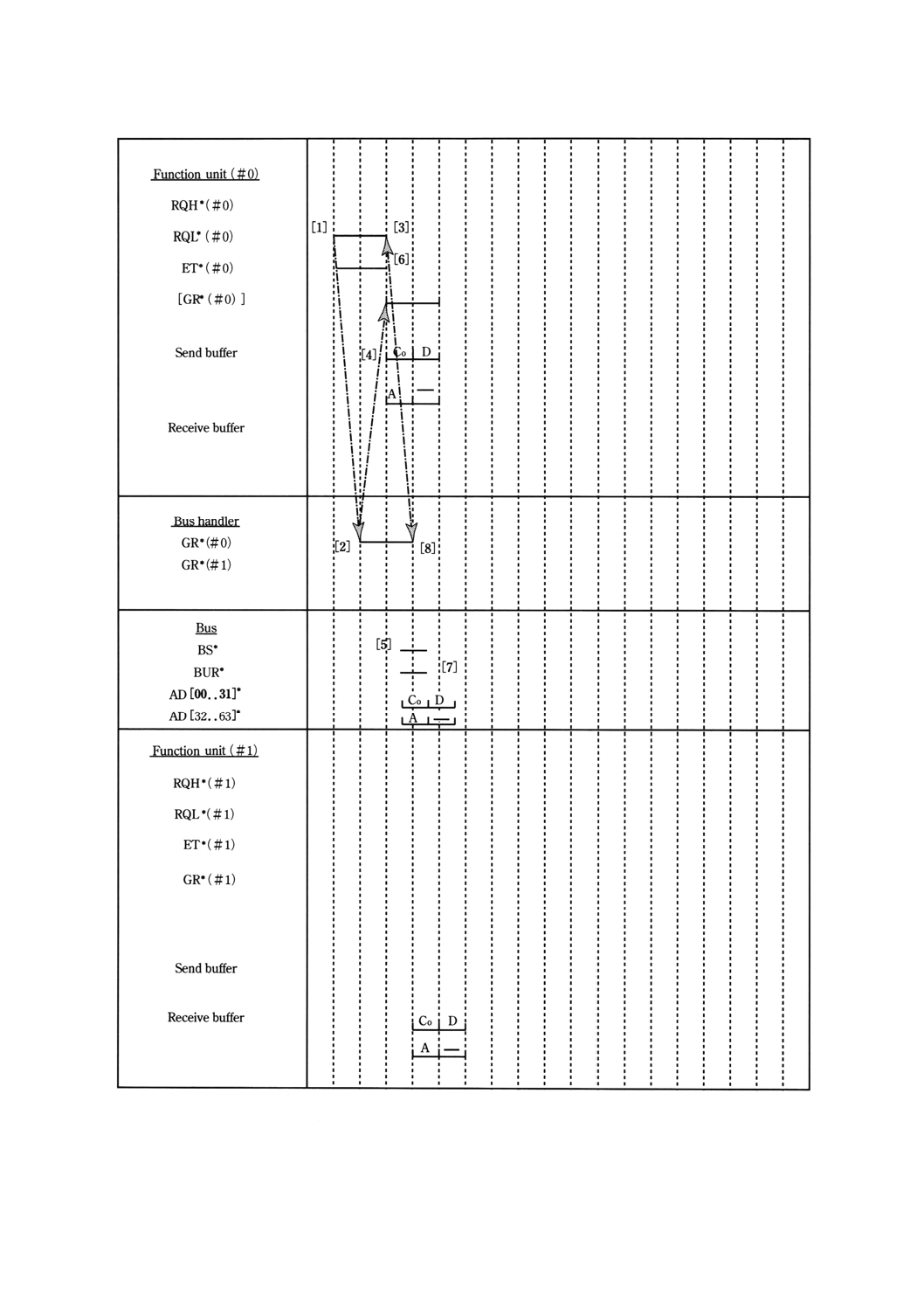

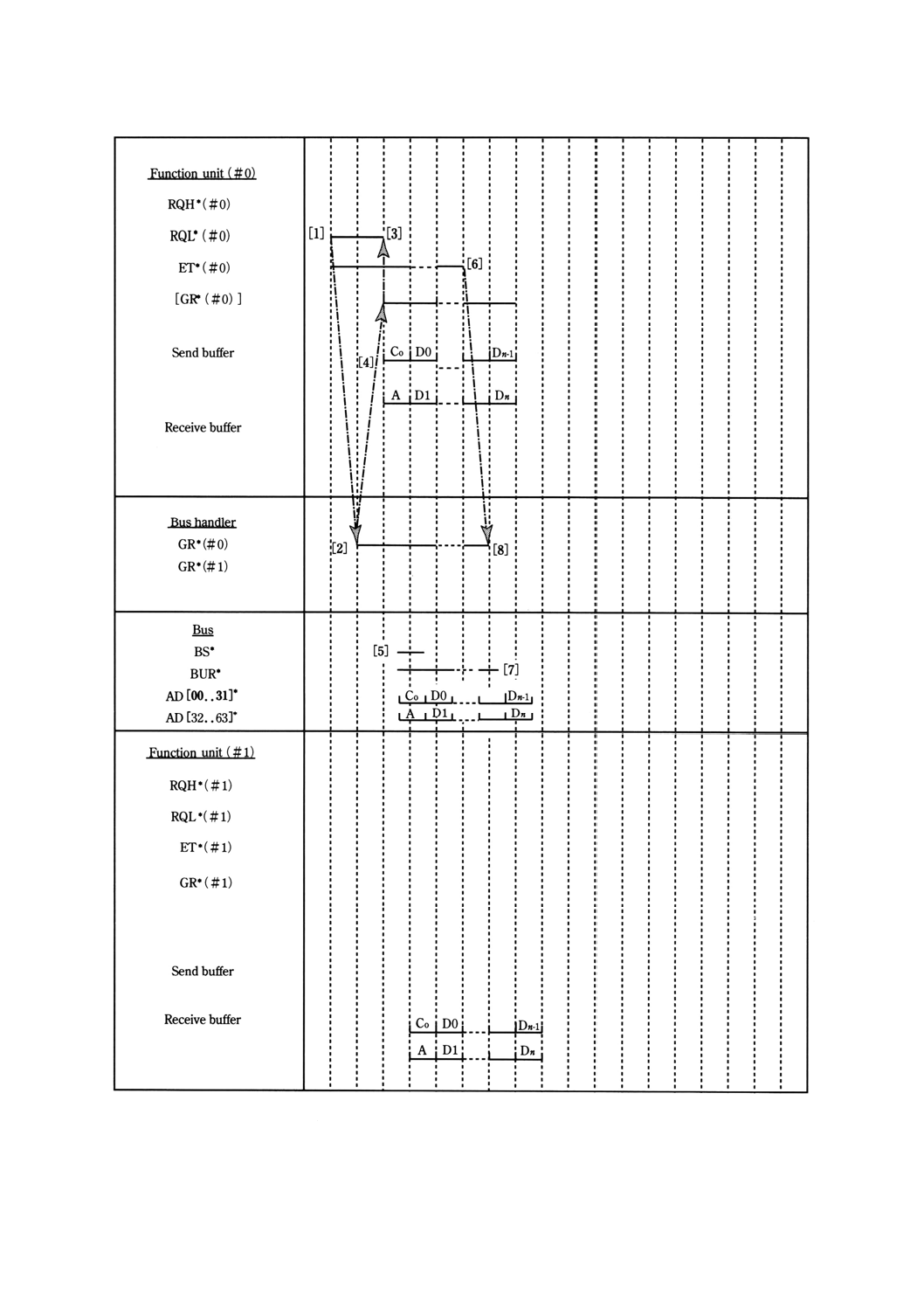

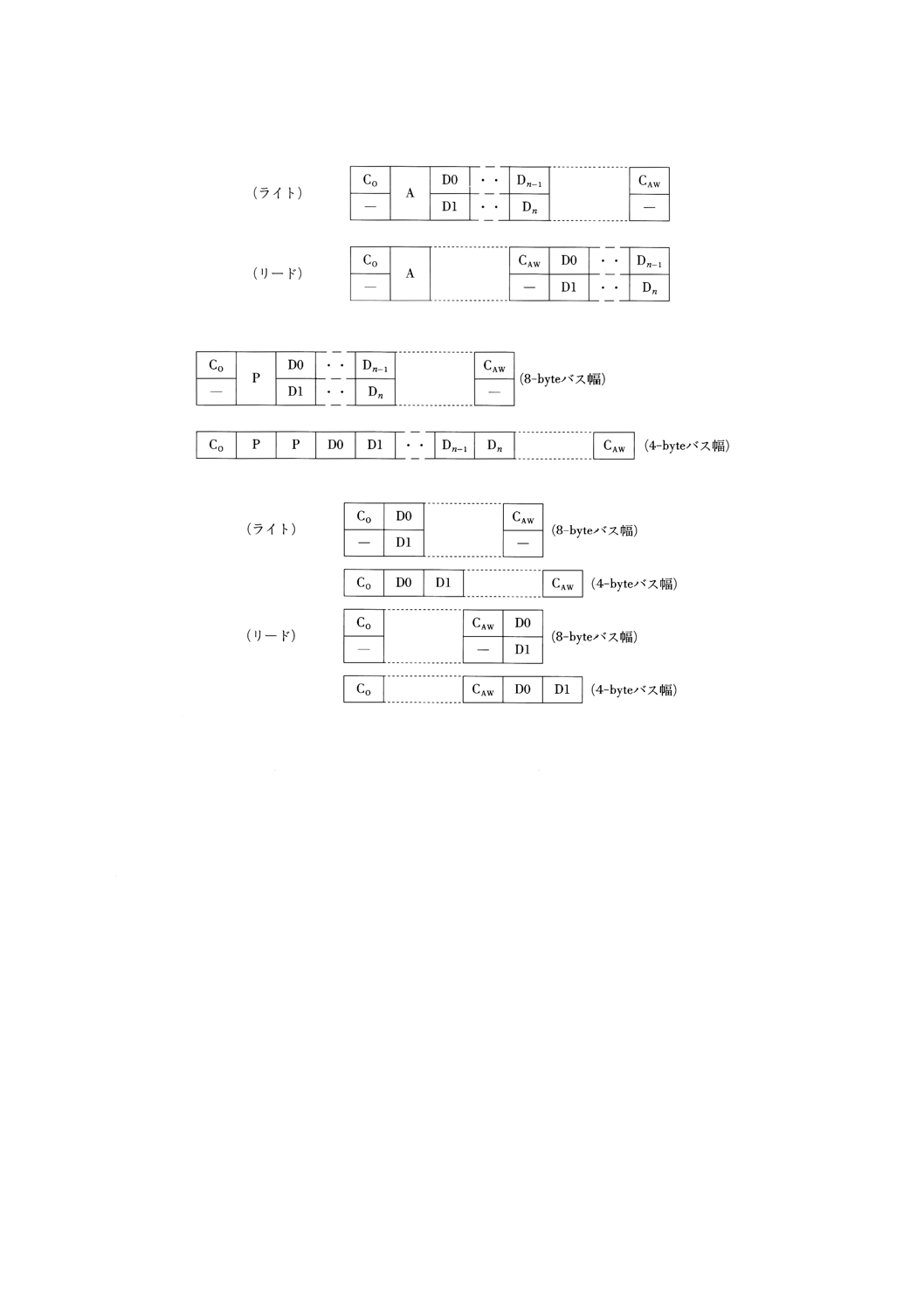

4.5.1

メモリアクセス(ライト) 図9にメモリアクセスのライト動作のバスシーケンスを示す。同図の

a),c)はそれぞれ1語メモリライト及びn語メモリライトの突き放しライト形を,b),d)はそれぞれ1語メ

モリライト及びn語メモリライトの基本形動作を示している。

システムバスの動作はすべてバスクロックの立ち下がり(図におけるたて点線)に同期して行われる。

図においてはゲート遅延を考慮しているため,バスクロックからずれて示される信号もある。

なお,バスの欄は機能ユニット間のバスにおいて現れる情報のタイミングを示している。

以下では,図9 d)n語メモリライト(基本動作形)の場合を中心に説明する。

[1] : 機能ユニット (#0) はメモリアクセス要求が新たに発生すると,RQL* (#0) をアサートしてバス要求

信号を発行する。

20

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

[2] : バスハンドラはRQL* (#0) が受付け可能になると,機能ユニット (#0) に対しGR* (#0) をアサート

しバス使用権を与える。

[3] : 機能ユニット (#0) はGR* (#0) のアサートによってRQL* (#0) をネゲートする。

[4]

: GR* (#0) によってバスの使用権を獲得した機能ユニット (#0) は,双方向の情報転送用ADバス,

BUR*及びCSP*信号を有効化して,情報をCO(コマンド)とA(アドレス),Di(データ)の順でバ

ス上へ送出する。

[5] : 最初の情報の転送と同時にBS*(バストランザクションスタート)信号をアサートして必要なバス

オペレーションの開始を他の機能ユニットに対して宣言する。

[6] : 機能ユニット (#0) は転送すべきデータの2サイクル前に転送終了予告信号をネゲートして転送の

終結をバスハンドラに宣言する。

[7] : 機能ユニット (#0) は転送すべきデータの1サイクル前にBUR*信号をネゲートして転送の終結を相

手の機能ユニットに宣言する。

[8] : ET*信号のネゲートを検出したバスハンドラは,GR* (#0) をネゲートして機能ユニット (#0) に対す

るバス使用権を取り上げる。

[9] : 機能ユニット (#1) は正常なライト完了で機能ユニット (#0) への完了通知のため正常のCAW(アン

サ)を準備し,バス使用権獲得のためのRQH* (#1) をアサートする。異常が検出された場合は異常

アンサを準備し,RQH* (#1) をアサートする。

[10] : バスハンドラはRQH* (#1) が受付け可能になると機能ユニット (#1) に対するバス使用許可信号

GR* (#1) をアサートして機能ユニット (#1) に対してバス使用権を与える。

[11] : 機能ユニット (#1) はGR* (#1) によって,RQH* (#1) をネゲートする。

[12] : GR* (#1) によってバス使用権を得た機能ユニット (#1) は,情報転送用ADバスを有効化し,CAW

をバス上へ送出する。

[13] : 機能ユニット (#1) はCAWの送出と同時にBUR*をネゲートしたままBS*をアサートして転送の開始

と終了を宣言する。

[14] : 上記の転送の開始・終了を検出したバスハンドラは,GR* (#1) をネゲートして機能ユニット (#1) に

対するバス使用権を取り上げる。

21

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図9 a) 1語メモリライト(アンサを伴わない転送)

22

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図9 b) 1語メモリライト

23

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図9 c) n語メモリライト(アンサを伴わない転送)

24

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図9 d) n語メモリライト

25

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

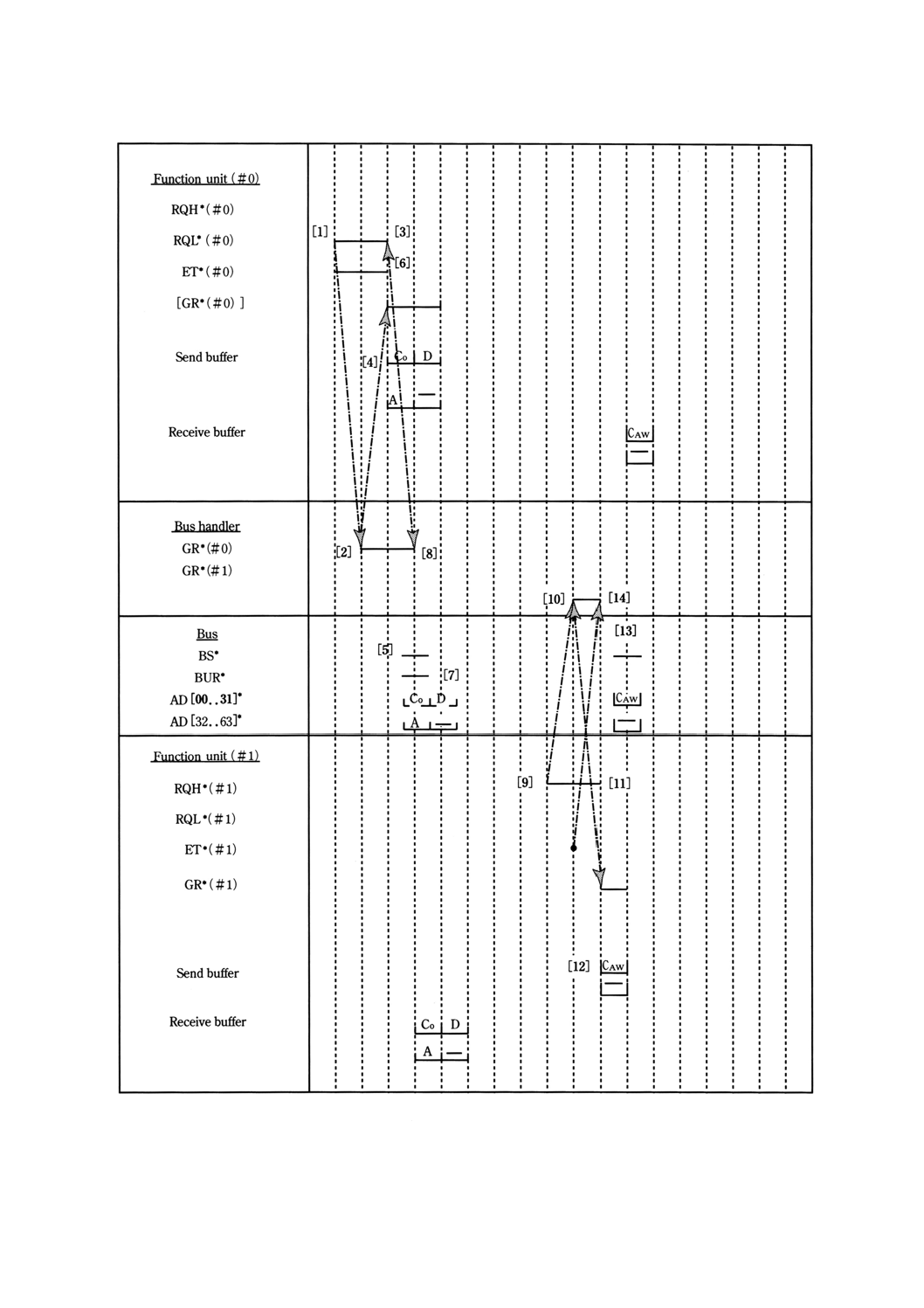

4.5.2

メモリアクセス(リード) 図10にメモリアクセスのリード動作のシーケンスを示す。

DUTに当たる機能ユニットは,自分の個別メモリ内のアドレスのさすメモリ空間からデータをリードす

る動作に入る。

リード動作終了後,DUTはCAW(アンサ)に引き続いてD(リードデータ)をSUTへ送出する。

SUTはCAWの内容及びデータをチェックして正常ならばそのリードデータを自分の個別メモリにライト

する動作に入る。ライト完了でメモリアクセスのリード動作は終了する。

CAWの内容が異常を示している場合,及びSUTの個別メモリのライト動作に異常が検出された場合には,

バスエラーとしてプログラムへ通知する。

26

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図10 a) 1語メモリリード

27

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図10 b) n語メモリリード

28

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.5.3

制御空間アクセス(ライト) 図11に,制御空間アクセスのライト動作のシーケンスを示す。

DUTに当たる機能ユニットは,自分の個別メモリ内のアドレスのさす制御空間へデータをライトする。

オペレーション終了後,DUTはオペレーションに対するCAW(アンサ)をSUTへ返送する。SUTは,

CAWの内容をチェックして,正常ならば制御空間アドレスのライト動作を終結する。

もし,異常ならばバスエラーとしてプログラムへ通知する。

29

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図11 n語ライト:制御空間アクセス

30

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.5.4

制御空間アクセス(リード) 図12に制御空間アクセスのリード動作のシーケンスを示す。

DUTに当たる機能ユニットは,自分の個別メモリ内のアドレスのさす制御空間からデータをリードする

動作に入る。

リード動作完了後,DUTはオペレーションに対するCAW(アンサ)に引き続いて,D(データ)をSUT

へ送出する。

SUTは,CAWの内容をチェックして,正常ならリードデータを自分の個別メモリにライトする動作に入

る。

CAWの内容が異常に示している場合,及びSUTの個別メモリのライト動作に異常が検出された場合には,

バスエラーとしてプログラムへ通知する。

31

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図12 n語リード:制御空間アクセス

32

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.5.5

メッセージ転送 図13にメッセージ転送の動作シーケンスを示す。

Co(コマンド)内のBSIDで指定されるDUTは,MDで示される動作に従ってデータをライトする動作

に入る。

ライト動作終了後,DUTはオペレーションに対するCAW(アンサ)を返送する。

SUTはCAWの内容をチェックして,正常ならばメッセージ転送動作を終結する。

もし,異常ならばバスエラーとしてプログラムへ通知する。

33

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図13 n語メッセージ転送

34

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

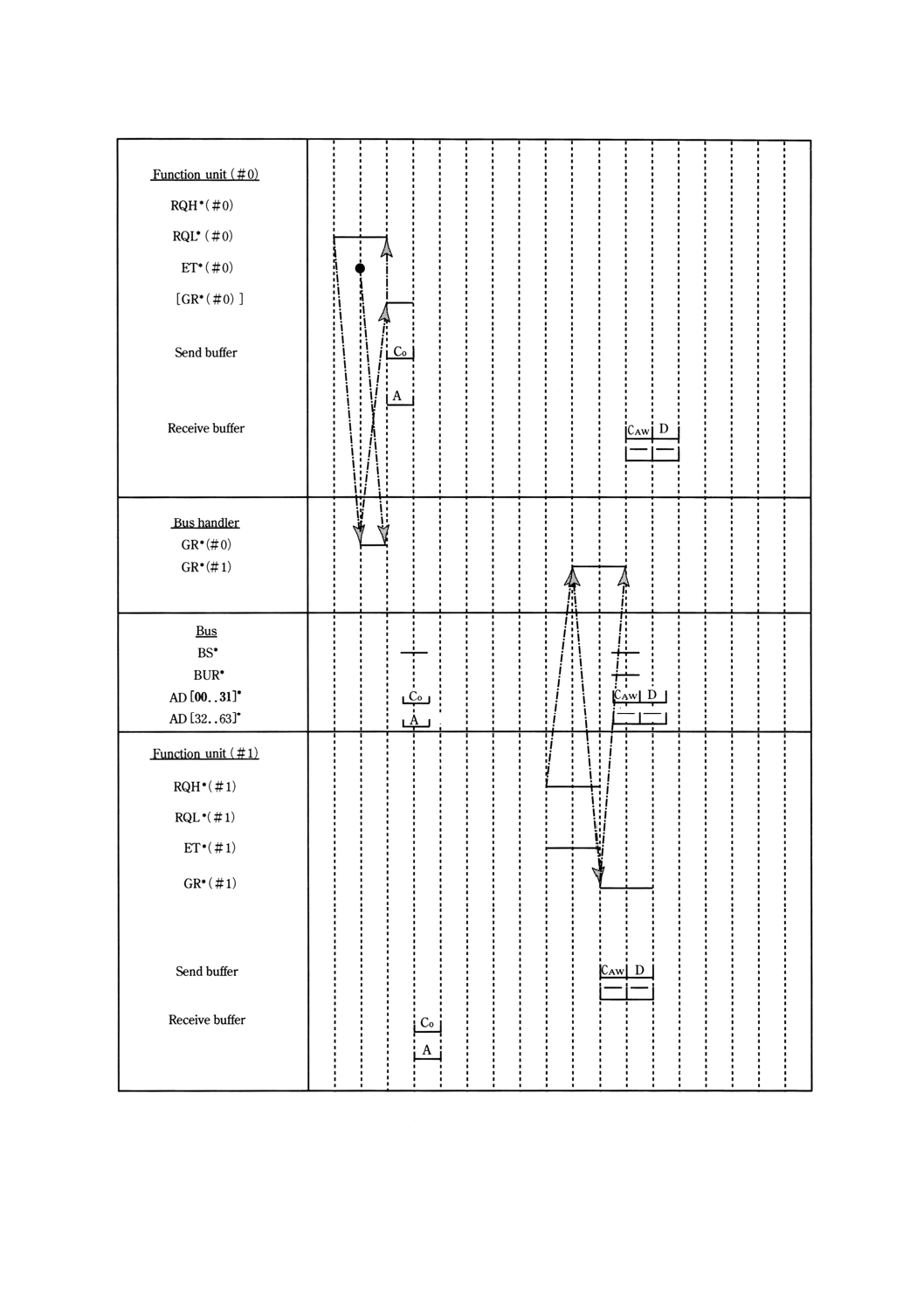

4.5.6

制御レジスタアクセス(ライト) 図14に,制御レジスタアクセスのライト動作のシーケンスを

示す。

DUTに当たる機能ユニットはCo(コマンド)中のRAで示される制御レジスタに,データの内容をライ

トする。

オペレーション終了後,オペレーションに対するCAW(アンサ)を返送する。

SUTはCAWの内容をチェックして,正常なら制御レジスタアクセスのライト動作を終結する。

もし,CAWの内容が異常を示していた場合,及びSUTのライトの動作に異常が検出された場合には,バ

スエラーとしてプログラムへ通知する。

35

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図14 1語ライト:制御レジスタアクセス

36

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.5.7

制御レジスタアクセス(リード) 図15に,制御レジスタアクセスのリード動作のシーケンスを

示す。

DUTに当たる機能ユニットはCo(コマンド)中のRAで示される制御レジスタの内容をリードする。

リード動作終了後,オペレーションに対するCAW(アンサ)を返送する。

SUTはCAWの内容をチェックして,正常ならリードデータを取り込んで制御レジスタアクセスのリード

動作を終結する。

もし,CAWの内容が異常を示していた場合には,バスエラーとしてプログラムへ通知する。

37

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図15 1語リード:制御レジスタアクセス

38

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

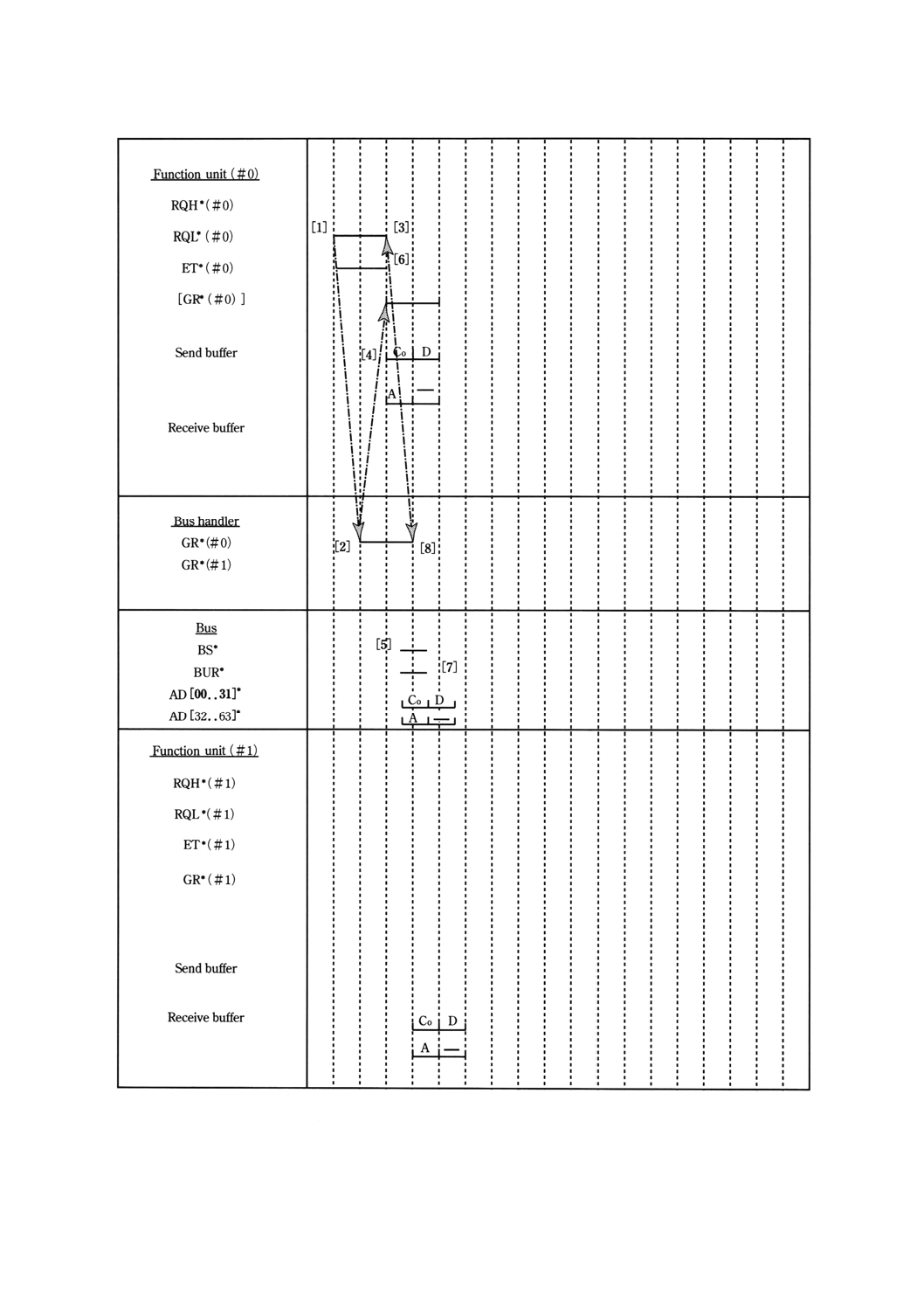

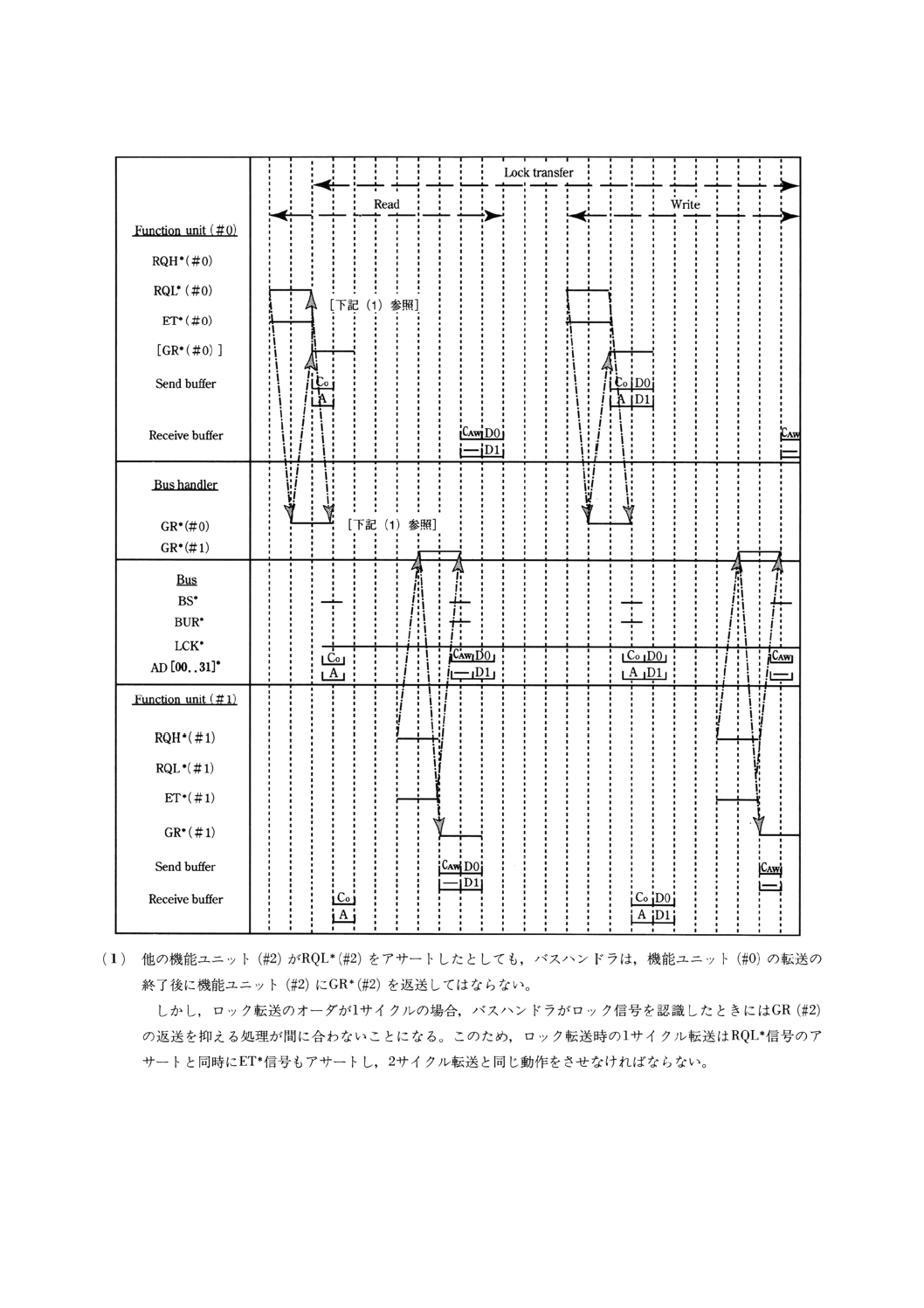

4.6

ロック動作 STbusは,機能ユニットがバスを排他的かつ連続的に使用するためのロック転送をサ

ポートしている。例えば,ロック転送はテスト&セット動作などで使用される。

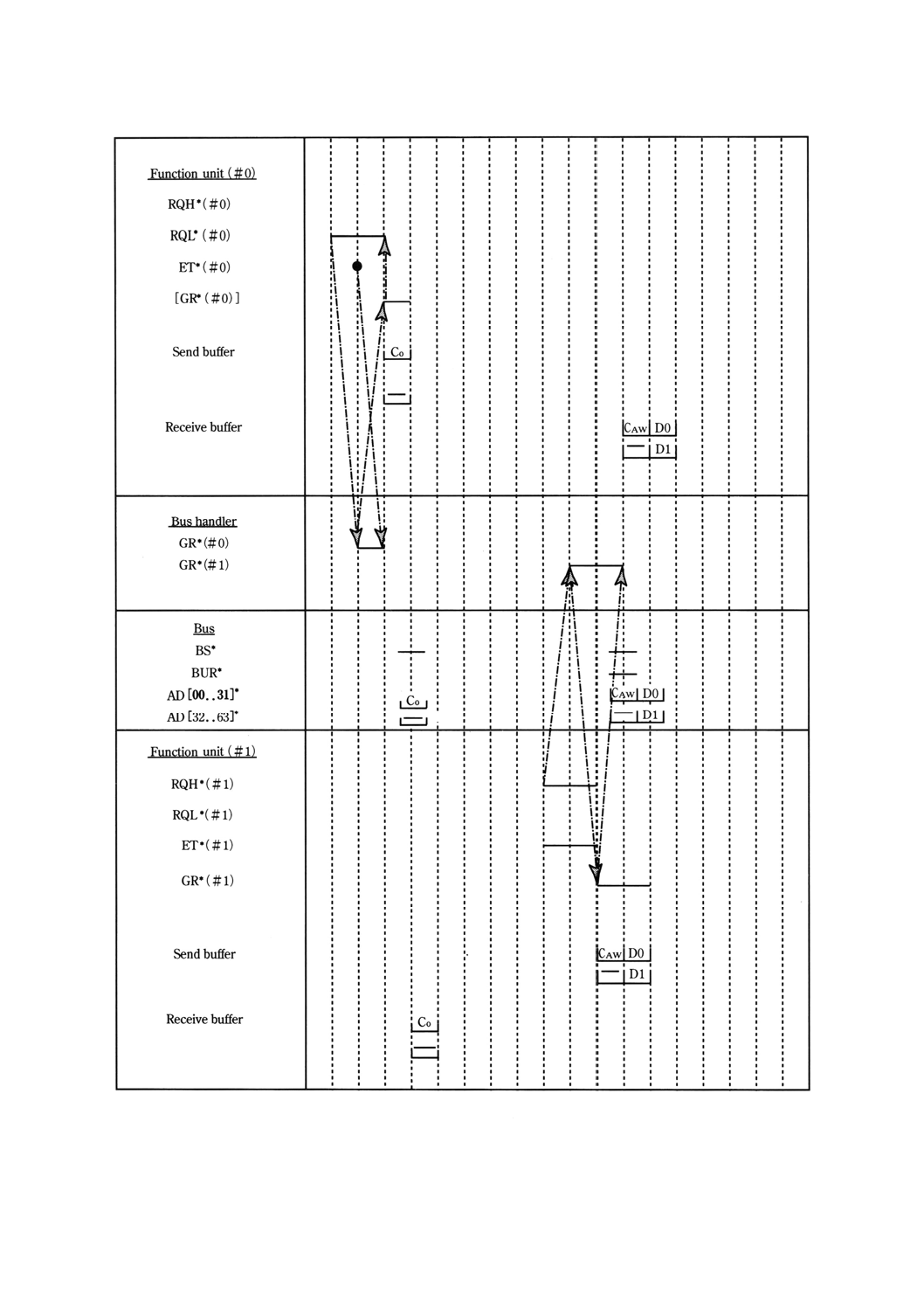

図16に,ロック転送の動作シーケンスを示す。

同図では,LCK*信号がアサート中に,リードバスオペレーションとライトバスオペレーションが引き続

いて行われている例を示している。

ロック転送を行うためにバス使用権を要求するときには,SUTはオーダが1サイクルで終了する場合で

もRQL*信号とET*信号を同時にアサートしなければならない(図16参照)。

LCK*信号はSUTがBS*のアサートと同時にアサートすること。LCK*のネゲートタイミングはプロセッ

サの排他制御命令の実行終了に依存するため,明らかには規定しない。ただし,SUTの最後のオーダ転送

が完了するまではアサート状態に保たなければならない。これによって,LCK*アーサト期間だけバスの排

他性を保証する。

バスハンドラはLCK*信号がアサート中は他の機能ユニットによるRQL*に対するGR*はアサートしない。

ただし,RQH*に対するGR*はアサートするので,どの機能ユニットもアンサ転送は実行可能である。

受信側機能ユニットがロック転送を認識したことを送信側に知らせるために,ロック転送用アンサコー

ドを設けている(表7のアンサコード=00000001)。

なお,EM状態(非共有変更状態)のキャッシュデータに対するロック転送の方法については,附属書

Cに示す。

39

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図16 バスロック転送

4.7

キャッシュ関連動作 この節ではコピーバックキャッシュサポートのためのシステムバス上の動作

について規定する。

40

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

この節でシステムバス上の動作シーケンスだけ説明する。動作後のキャッシュの状態遷移については,

5. キャッシュのコヒーレンシ制御を併せて参照のこと。

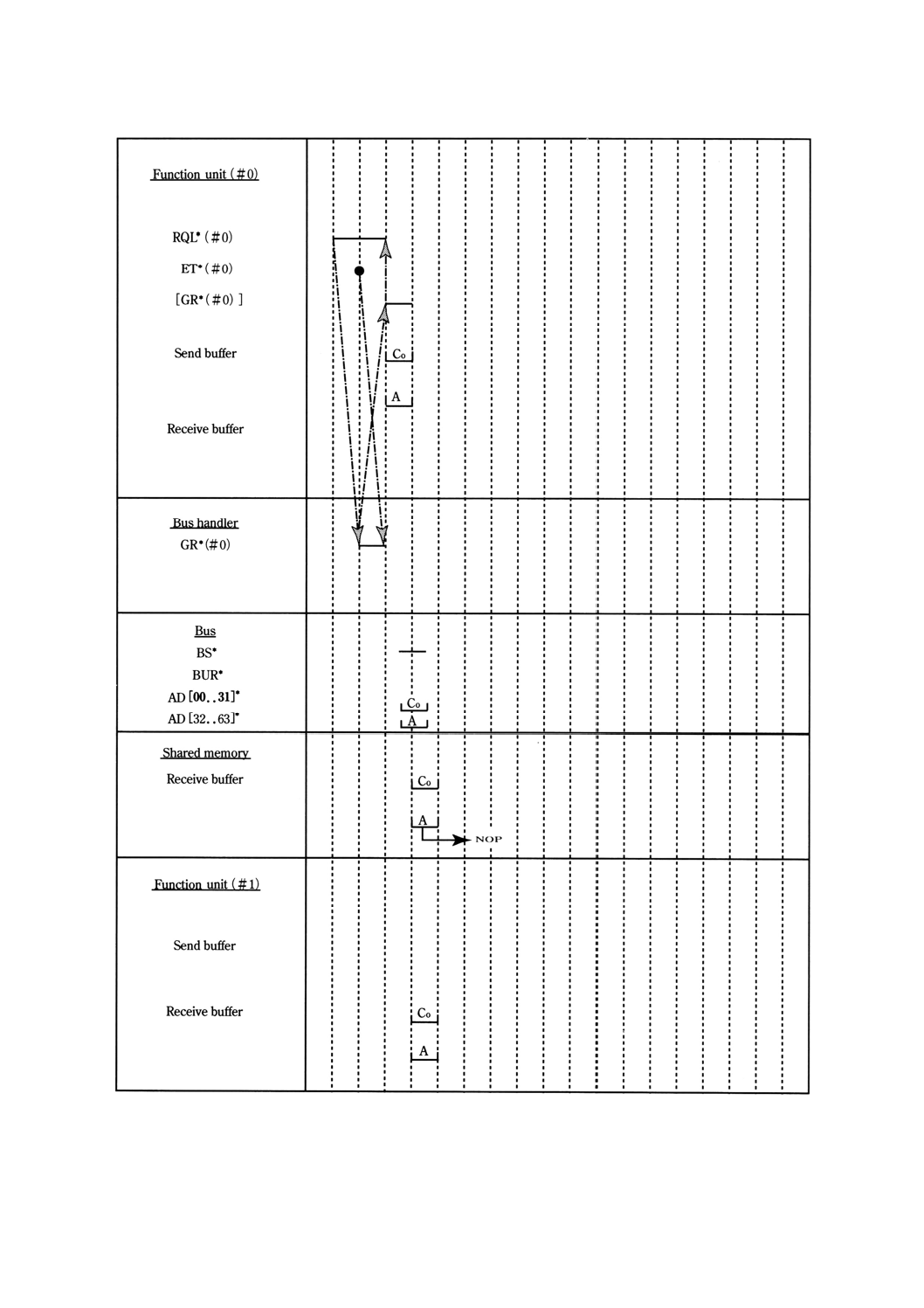

4.7.1

キャッシュ無効化指示動作 プロセッサのバスインタフェース制御は,常にメモリへの書き込みコ

マンドをスヌープして書き込みアドレスがキャッシュにヒットした場合,キャッシュの無効化を行う必要

がある。

このため以下の機能が設けられている。

a) モデファイ付きリード動作 プロセッサが書き込みを行おうとしたメモリのアドレスがプロセッサの

キャッシュに存在しない場合,プロセッサはメモリ読み出しコマンドを発行してデータを読み出した

後,自キャッシュへの書き込みを行う。この場合プロセッサのキャッシュの状態はモデファイ状態と

なるので,他プロセッサのキャッシュを無効化する必要がある。プロセッサがメモリの読み出しコマ

ンドを実行後,b)で説明するキャッシュ無効化のためのメモリへの書き込みコマンドを実行すること

でもこの機能は実現できるが,不要なメモリ書き込みコマンドをシステムバスに送出しなくてよいよ

うに,メモリアクセスコマンドにMビットが設けられている。

プロセッサは,キャッシュライトミスによってメモリアクセスを行う場合,Mビットを “1” として

メモリ読み出しを行う。

他プロセッサはバスをスヌープし,メモリ読み出しのバスオペレーション時に,Mビットが “1” の

場合アドレスモニタする。このときキャッシュにヒットした場合,キャッシュの該当エントリを無効

化する。

b) 共有未変更状態のキャッシュ無効化指示 機能ユニット内のコピーバックキャッシュに登録されたあ

るブロックが共有未変更 (SU) 状態であるとき,そのブロックの書き換えに伴い,他プロセッサのキ

ャッシュを無効化するため次のコマンドが設けられている。

SU状態にあるブロックに書き込みを行いたいプロセッサは,メモリ書き込みコマンドにおいて,M

ビットを “1” とし,バス上にコマンド,アドレスだけを送出する。

他プロセッサは,メモリ書き込みコマンドを認識してキャッシュの無効化を行う。

このバスオペレーションは,キャッシュのキャッシュ無効化だけが目的であるので,メモリの書き

込みは行わない。

図17にキャッシュ無効化動作のシーケンスを示す。キャッシュ無効化コマンドの場合,特定のバス

スレーブは存在しない。ただし,オーダコマンド,アドレスを転送中にパリティエラーが発生した場

合,バスハンドラが異常を検出する。また,キャッシュ無効化指示コマンドに対して,4.7.2のリトラ

イ動作が生じた場合は,このキャッシュ無効化動作を中止する。そして再度バスを獲得した後,プロ

セッサで更新された部分を共有メモリに書き込む。

41

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図17 キャッシュ無効化指示動作

42

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

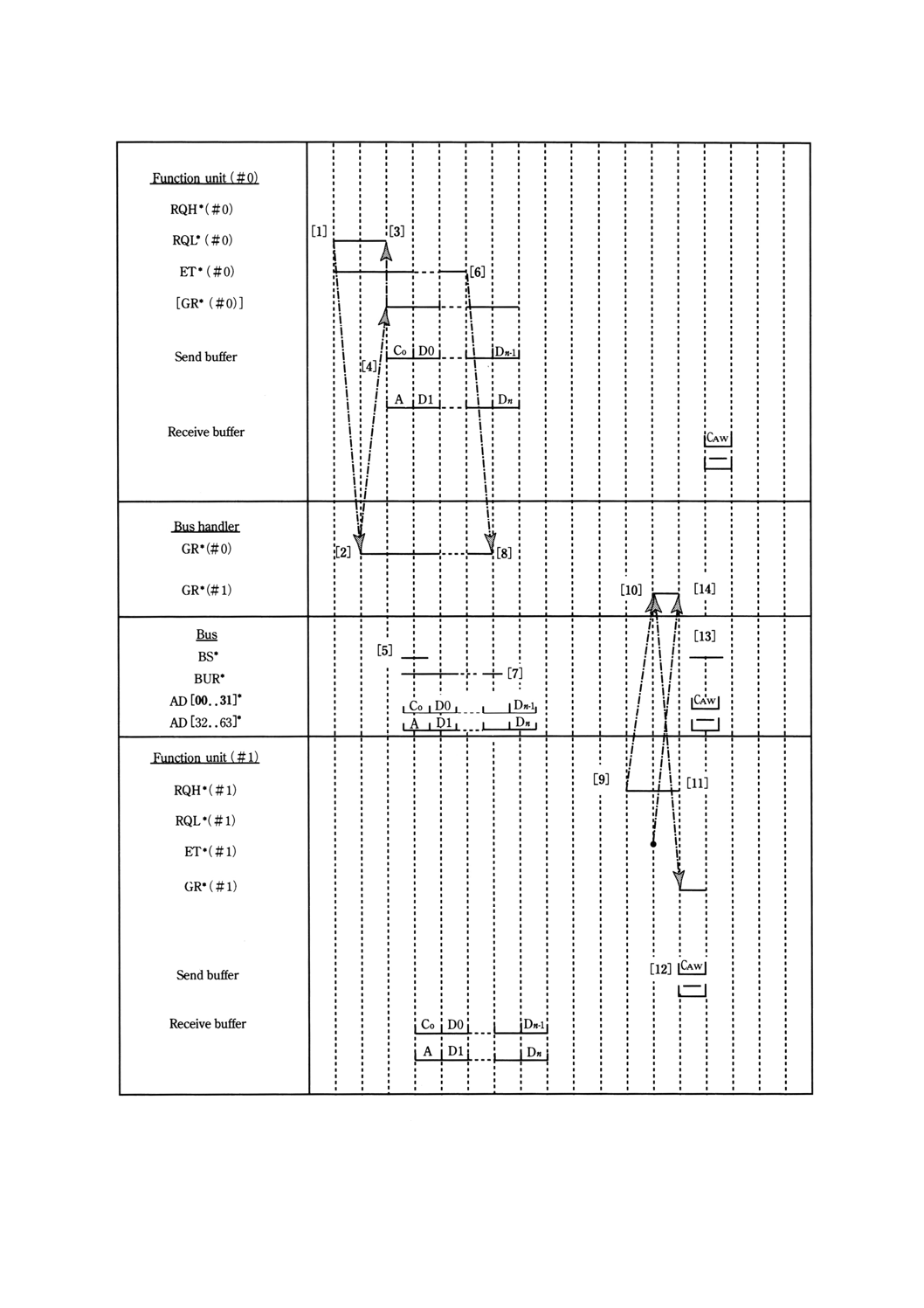

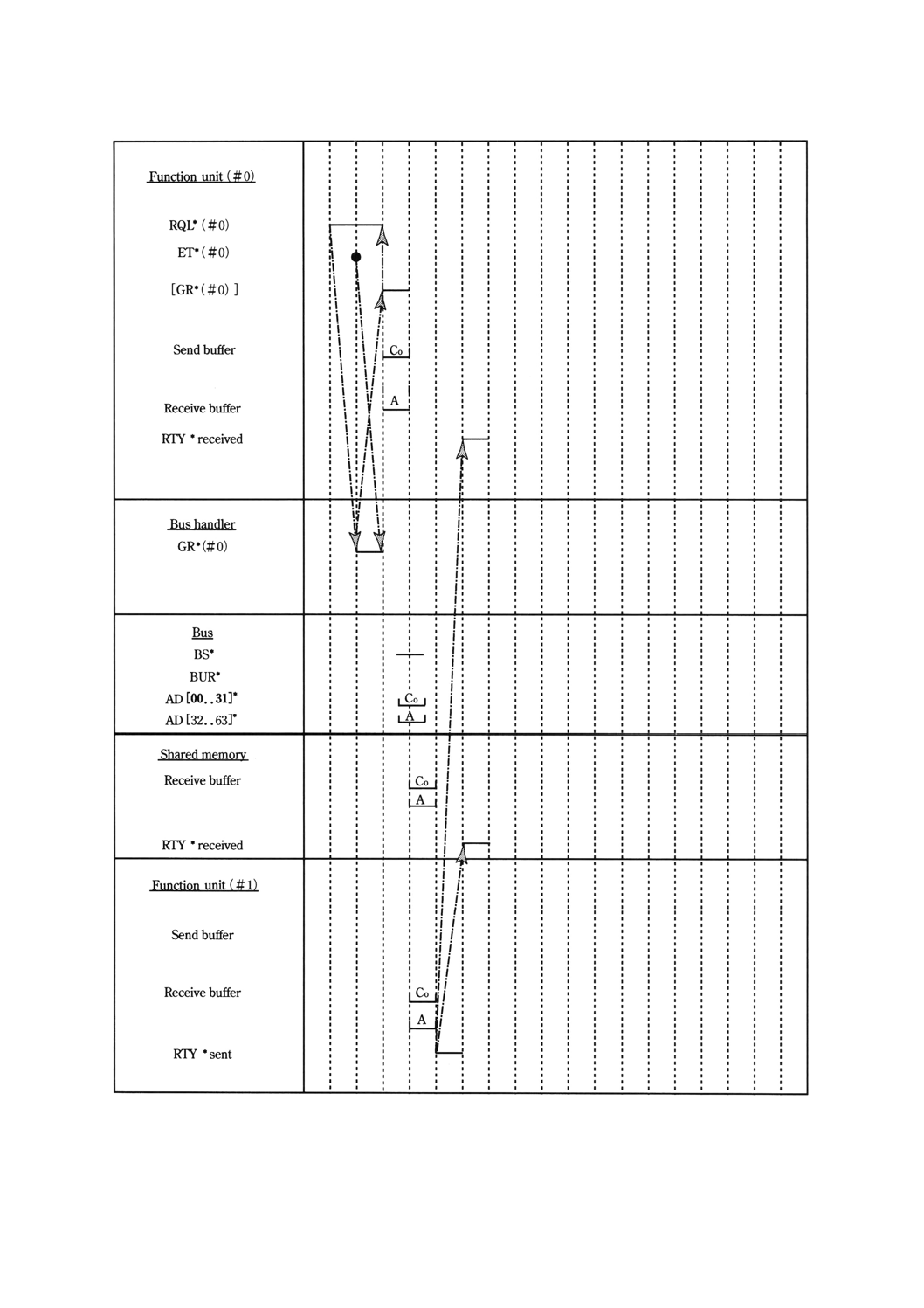

4.7.2

リトライ指示動作 システムバスの負荷を軽減するために,自プロセッサに存在するキャッシュ上

のブロックだけを更新して共有メモリを更新しない場合,当該ブロックに対する他プロセッサやI/Oアダ

プタからの読み出しに対して,自プロセッサのキャッシュにヒットすると,読み出しデータを自プロセッ

サから送出する必要がある。

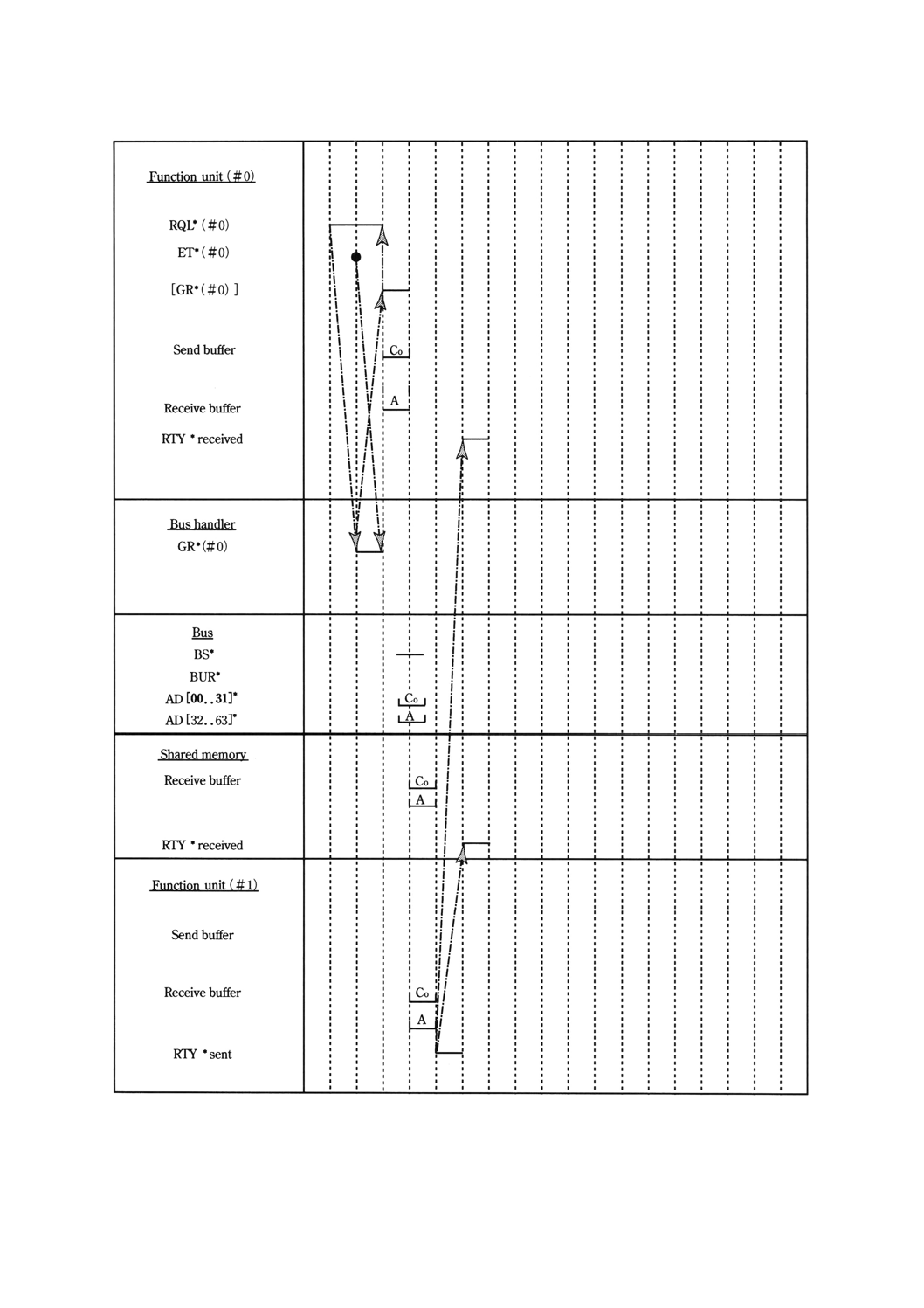

図18にリトライ指示動作のシーケンスを示す。

機能ユニット (#0) はキャッシュミスを検出して,メモリに対してブロック読み出しコマンドを発行し

たが,アクセスアドレスが機能ユニット (#1) のキャッシュにヒットし,かつ当該キャッシュ状態が変更

状態 (EM) ,つまり最新のブロックが機能ユニット (#1) のキャッシュにだけ登録されている場合,機能

ユニット (#1) はRTY*信号をアサートする。

リトライ信号RTY*はオーダ転送の最初のサイクル(コマンド転送サイクル)から2サイクル後のタイ

ミングでアサートされる。図18ではリードオーダに対するリトライ指示動作の例を示した。

ライトスルー動作に対しても,同様の制御を行う。このとき,共有メモリはリード,ライト動作とも行

わない。

43

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図18 リトライ指示動作

44

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.7.3

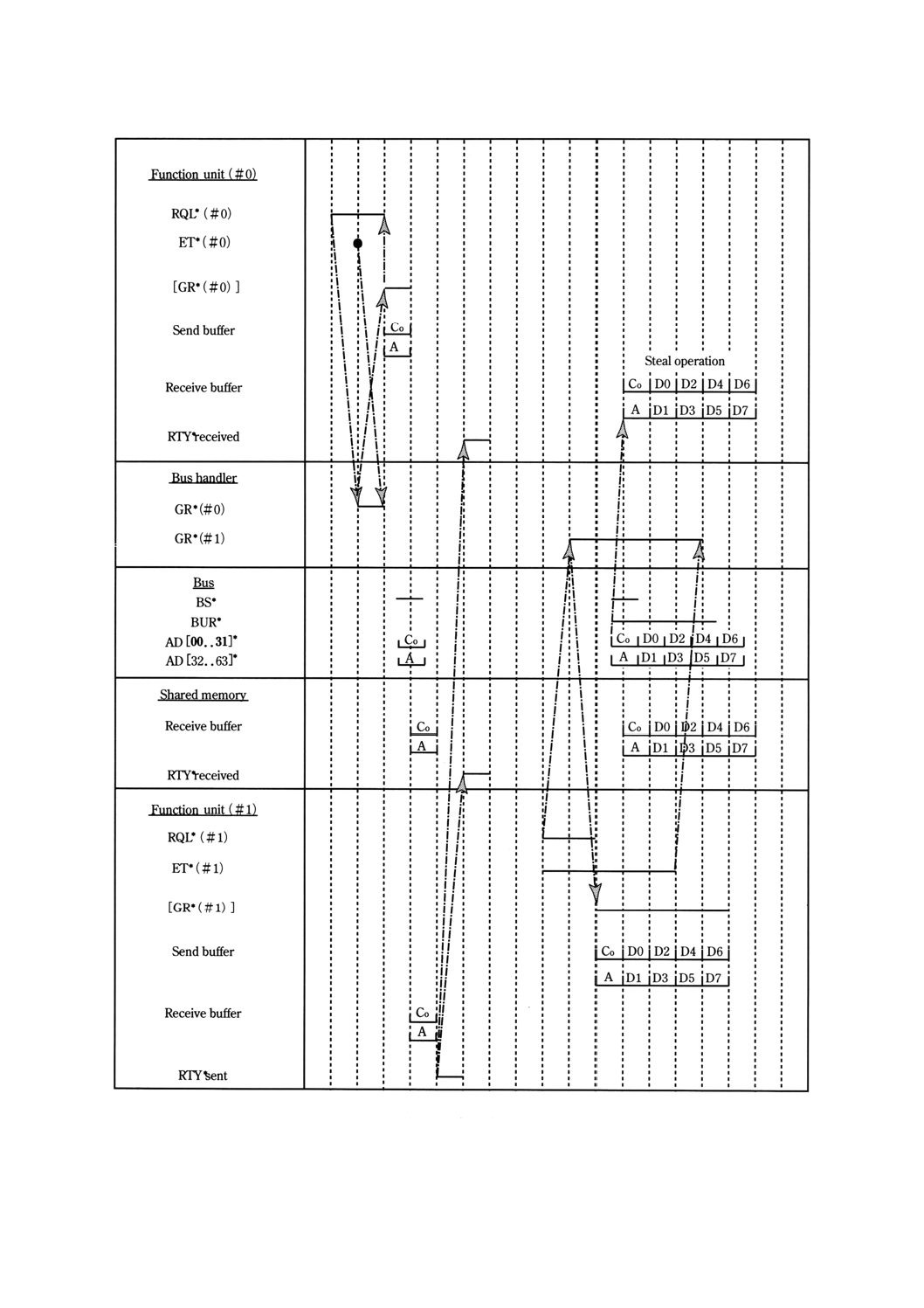

リトライ指示後のコピーバック動作とスチール動作 リトライ信号を受信した送信元の機能ユニ

ットSUTは一定期間コピーバックのための保留期間を経過した後,リトライ動作を行う。このリトライ動

作に先立ち,リトライ信号をアサートした機能ユニットによるコピーバック動作が行われる。

図19にリトライ指示後のコピーバック動作のシーケンスを示す。この図ではリトライ信号をアサートし

た機能ユニット (#1) が,1ブロック(32バイト)の非共有変更状態 (EM) のキャッシュデータを共有メ

モリへコピーバックする動作が示されている。

また,この図には,機能ユニット (#0) によるスチール動作のタイミングも示されている。スチール動

作に関してはオプションであり,スチール禁止信号STI*を備えたシステムだけ行うことができる。

スチール禁止信号を備えていないシステムの場合,コピーバック後に機能ユニット (#0) が共有メモリ

へ再アクセスを行う。

45

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図19 リトライ指示後のコピーバック動作とスチール動作

46

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

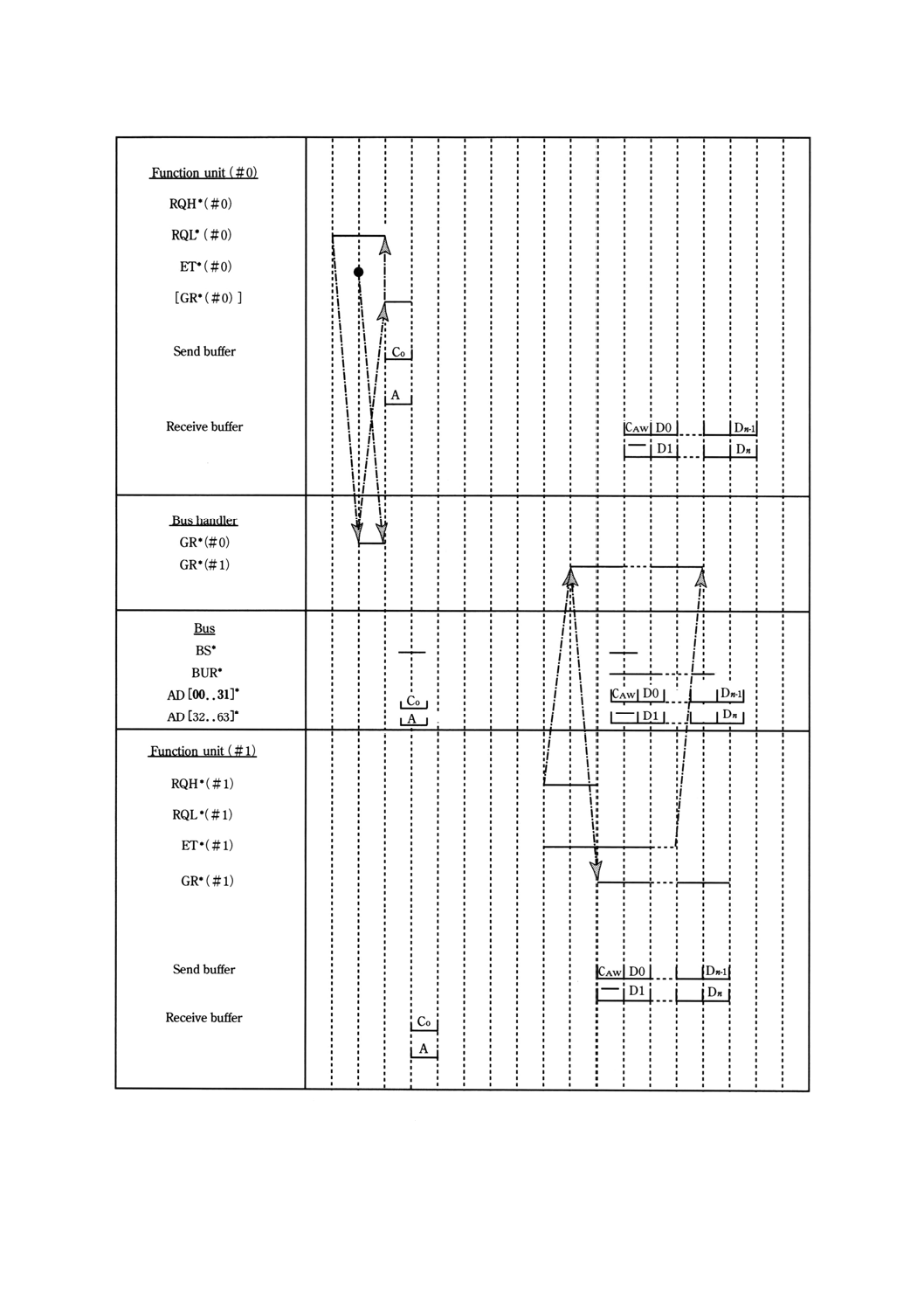

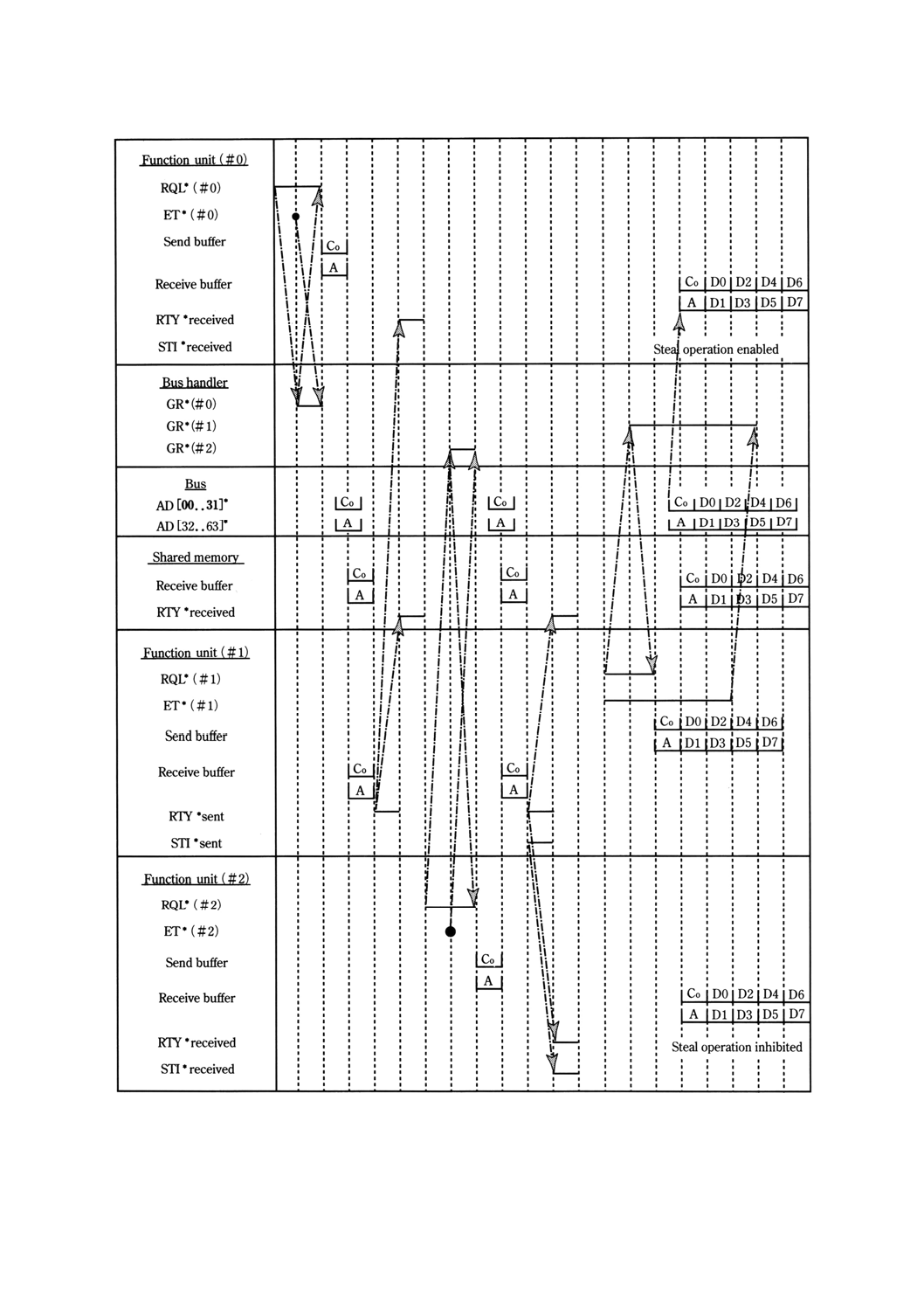

4.7.4

スチール禁止指示動作 スチール動作については,5.で示すように,キャッシュコヒーレンシを維

持するために一定期間禁止される場合がある。スチール禁止指示の行われる動作シーケンスを図20に示す。

機能ユニット (#0) がリードアクセスを行う。次にアクセス対象アドレスのEM状態のキャッシュデー

タを保持する機能ユニット (#1) が,リトライ信号RTY*をアサートする。このときスチール禁止信号STI*

はアサートされない。

機能ユニット (#1) によるコピーバックが行われる前に,機能ユニット (#2) は同一ブロックのモディフ

ァイ付きリードを行うものと仮定する。

機能ユニット (#1) はリトライ信号をアサートし,同じタイミングでスチール禁止信号STI*をアサート

する。その後,機能ユニット (#1) がコピーバック動作を行う場合は,機能ユニット (#0) はスチール可能

で機能ユニット (#2) はスチール禁止となる。

もし両者のスチールを同時に認めると,同一ブロックに対するキャッシュデータの矛盾が生じることに

なるため,上記シーケンスでは機能ユニット (#2) のアクセスの際,STI*信号によってスチール動作の禁止

を通知している。

47

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図20 スチール禁止指示動作

48

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

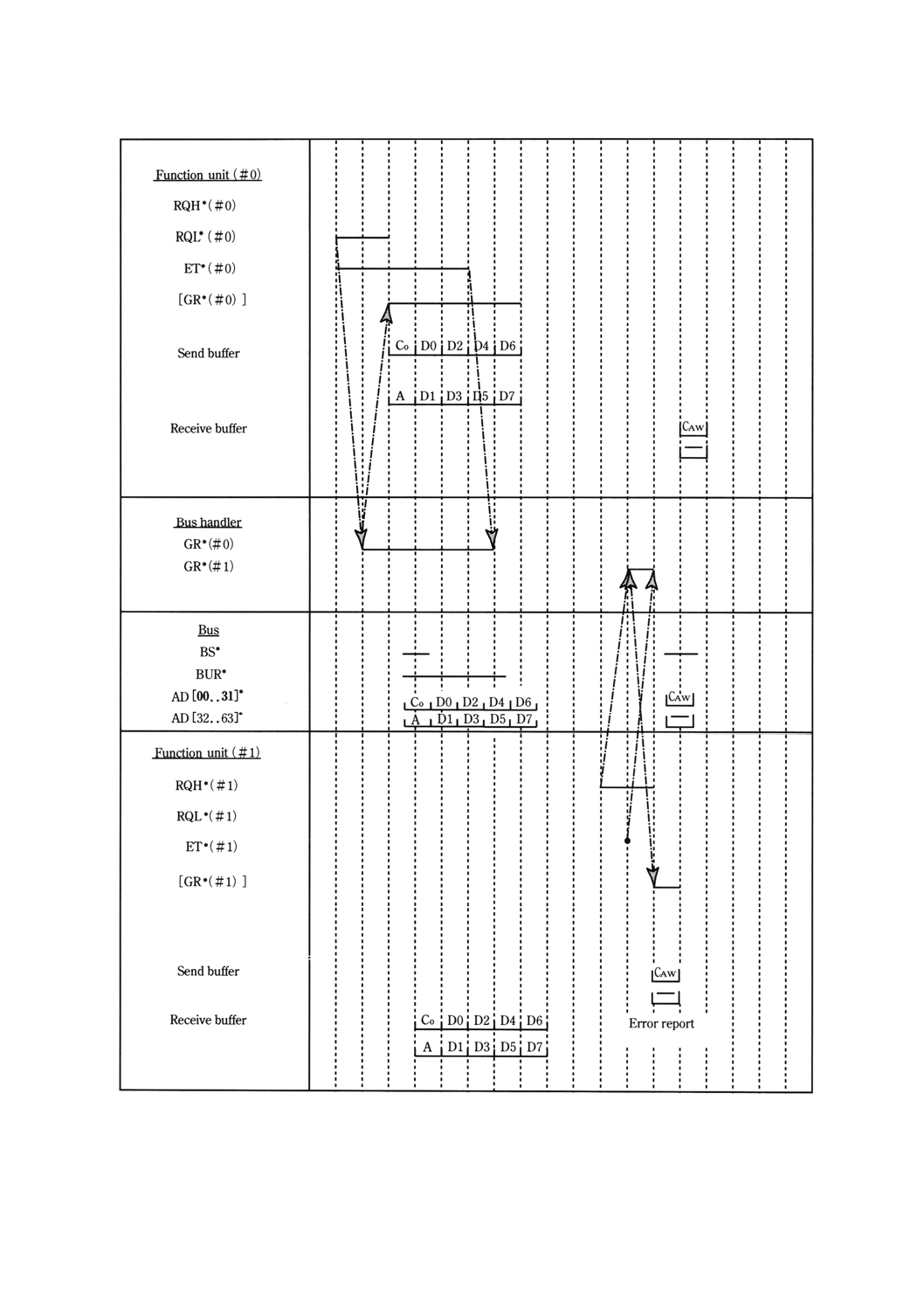

4.8

異常処理 この項では,アンサによって報告される異常発生時の動作について規定する。

4.8.1

アンサによって報告される異常処理 アンサによる異常報告は,DUTが行う。

バスオペレーションにおいて転送データに異常が検出された場合,DUTはアンサによって異常が発生し

たことをSUTに通知する。

SUTはそれを受け取り,異常処理を行う。SUTは必要に応じて再送処理をしてもよい。

DUTが検出する異常は,以下のとおりである(表7参照)。

・Hardware error

・Illegal command

・Bus sequence error

図21に,DUTが異常を検出した場合の動作シーケンスを示す。

49

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図21 DUTで異常を検出しアンサで応答する場合

50

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

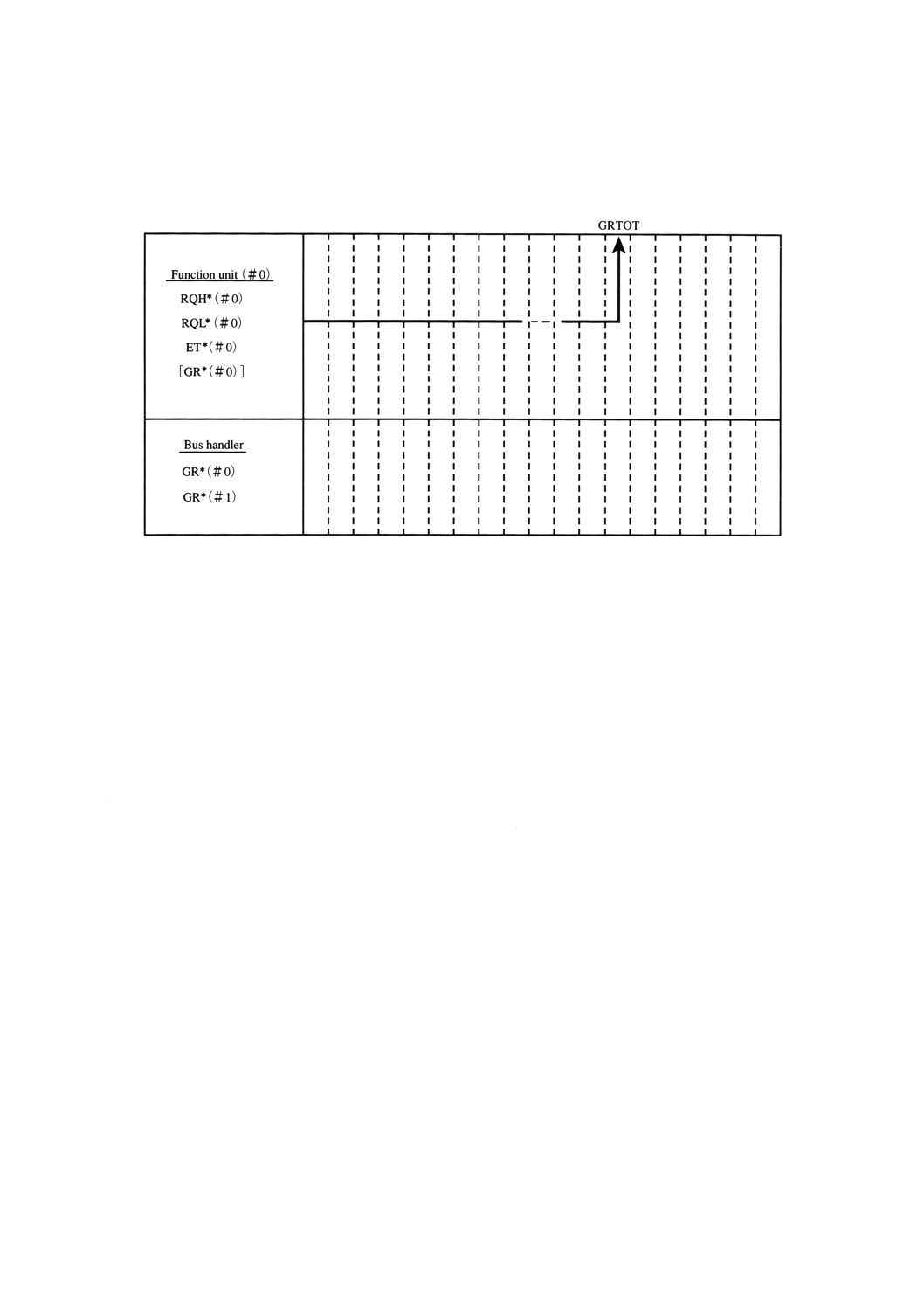

4.8.2

その他の異常処理

1) GRTOT (Grant Time Out) SUTが所定の待ち時間を経過してもバスを獲得できないことを検出した。

図22にその動作シーケンスを示す。

図22 機能ユニット (#0) がタイムアウトを検出したケース

2) ASTOT (Answer Time Out) SUTが所定の待ち時間を経過してもアンサ情報を受信できないことを検

出した。

上記の1),2)の異常は機能ユニットごとに存在するバスインタフェース制御部 (BIC) によって検出され

る。BICはそれぞれの異常を何であるか (GRTOT/ASTOT) を登録し,バス動作を異常終結させる。

なお,待ち時間についてはユーザ規定とする。

5. キャッシュのコヒーレンシ制御 この章ではSTbusをTCMP(密結合型マルチプロセッサ)のメモリ

バスとして使用する場合の機能ユニット内のキャッシュと共有メモリ間のコヒーレンシ維持動作について

述べる。

キャッシュのコヒーレンシの維持は,32バイトからなるブロックを単位として行われる。

キャッシュコヒーレンシ制御はオプションであり,ユーザは必ずしもインプリメントしなくてよい。

5.1

キャッシュ制御方式の種類 STbusがサポートするキャッシュの制御方式は,以下の2種類である。

1) ライトスルー[無効 (I) ,共有未変更 (SU) の2状態からなる。]

プロセッサ又は命令実行部からの書き込みデータを,直接メモリに反映する方式。

2) コピーバック[無効 (I) ,共有未変更 (SU) ,非共有変更 (EM) の3状態からなる。]

プロセッサ又は命令実行部からの書き込みデータを,直接共有メモリに反映せず,キャッシュ内だ

けを更新しておく方式。内部状態3のキャッシュをサポートする。

STbusでは,上記の2種類のキャッシュの混在もサポートする。そのため,ライトスルーキャッシュの

動作の規定にも,コピーバックキャッシュとの混在時のための最小限の規定が追加されている。

5.2

キャッシュデータの属性 各機能ユニットはキャッシュをもつことができる。それぞれのキャッシ

ュは,複数のブロックから構成されている。各ブロックは,以下の属性によって管理されている。

I

:ブロックに登録されたデータが無効であるときの状態。

51

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

SU

:ブロックに登録されたデータが共有メモリと一致している状態。複数のキャッシュで同一

のブロックを共有している可能性がある。

EM

:ブロックに登録されたデータが最新のデータであり,共有メモリと内容が一致していない

状態。この状態のブロックはただ一つだけ存在し,他のキャッシュには共有されない。

スプリット転送のシステムバスを用いてコピーバックキャッシュを構築するため,上記のキャッシュブ

ロックの属性に加えて,以下のアクセス途上の過渡状態が定義されている。

ISU

:リードオーダ発行からアンサを受け取るまでのI⇒SU遷移途中の過渡状態。

IEM

:モディファイ付きリードのオーダ発行からアンサを受け取るまでのI⇒EM遷移途中の過渡

状態。

EMSU

:他のプロセッサによるリードアクセスに対して,EM状態の最新データをプロセッサ内の

キャッシュに保持している場合,他のプロセッサに対するリトライ動作指示後,当該デー

タをコピーバックするまでのEM⇒SU遷移途中の過渡状態。

EMI

:他のプロセッサによるライトアクセスに対して,EM状態の最新データをプロセッサ内の

キャッシュに保持している場合,他のプロセッサに対するリトライ動作指示後当該データ

をコピーバックするまでのEM⇒I遷移途中の過渡状態。

5.3

システムバス上の動作 この節ではキャッシュの動作とシステムバス上のコマンドの関係について

述べる。

以下にメモリアクセスコマンド中のR/WとMフィールドの組合せによって実現されるシステムバスコ

マンドの種類を示す。

表8 システムバスコマンドタイプ

R/W

M

バスの動作

0

0

ライトコマンド

1

キャッシュの無効化指示コマンド (CI)

1

0

リードコマンド

1

モディファイ付きリードコマンド

備考 キャッシュの無効化指示の動作シーケンスについて

は,図17を参照のこと。

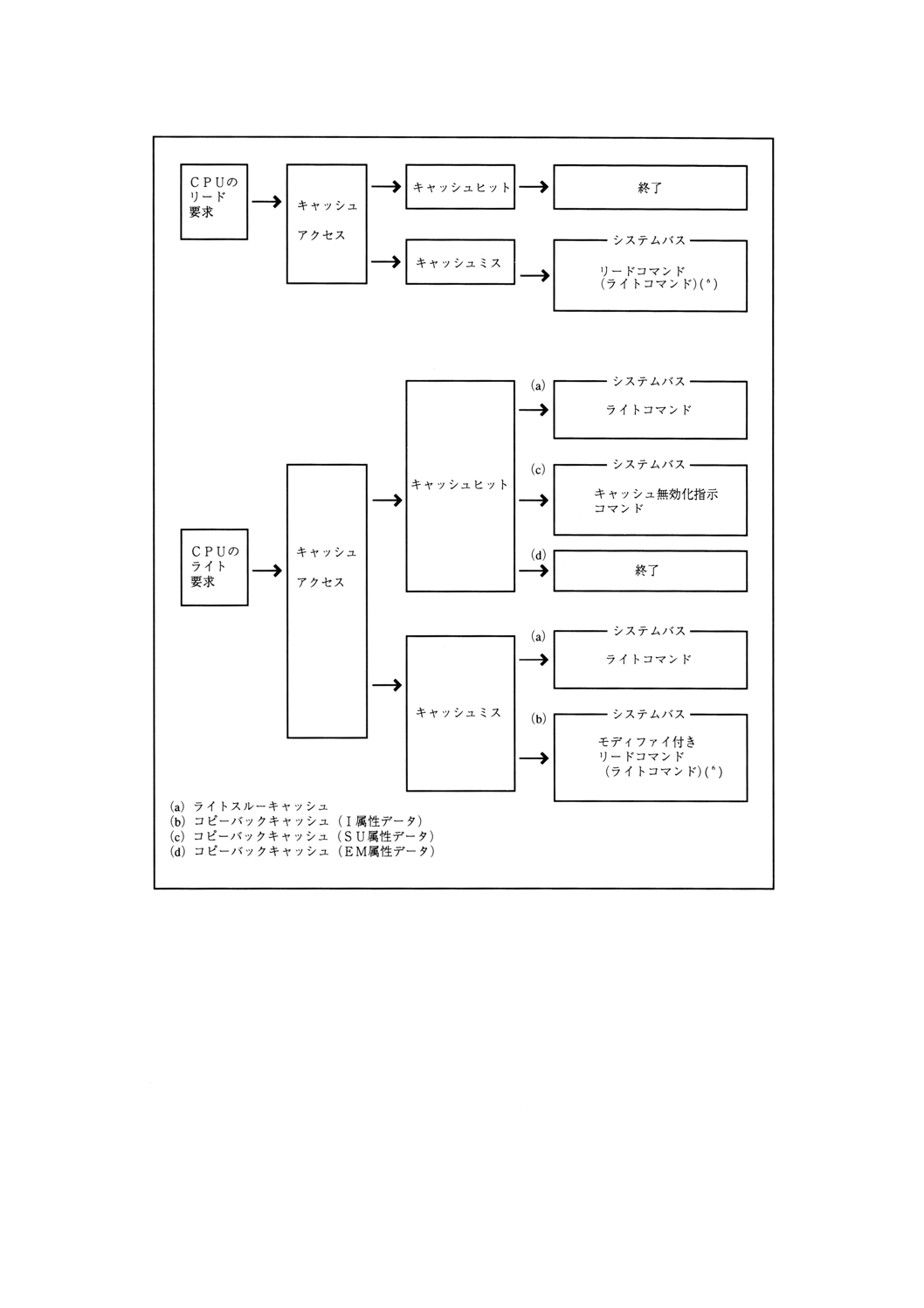

1) システムバスコマンド送出 システムバス上のコマンドの送出は,CPUの動作に起因する。CPUの動

作とそれぞれのシステムバスコマンドの関係については,図23に示す。

システムバスコマンドは,キャッシュの制御方式又はアクセス領域のキャッシュデータのブロック

の属性の影響を受ける。

52

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

注(6) リプレース動作:

キャッシュへ新規データを登録するための動作。コピーバックキャッシュでは

EM属性のデータに対し,新規登録に先立ってコピーバックを行う必要があ

る。

図23 CPUの動作とシステムバス上のコマンドの関係

2) システムバスコマンドの受信 キャッシュコヒーレンシを維持するために,他のユニットが送出する

システムバスコマンドを各ユニットは監視する。このような動作をバス・スヌープ動作と呼ぶ。

ライトスルーキャッシュの場合には,以下のような動作を行う。

・ 他のユニットのライトコマンド

⇒ 当該ブロック無効化

・ 他のユニットのキャッシュ無効化指示コマンド

⇒ 当該ブロック無効化

・ 他のユニットのリードコマンド

⇒ 動作なし

・ 他のユニットのモディファイ付きリードコマンド ⇒ 当該ブロック無効化

53

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

コピーバックキャッシュでは,アクセスされたキャッシュ領域について,自機能ユニット内にEM

属性データをもつ場合や,ちょうど当該領域に対してオーダを送出してアンサ待ちの場合は,リトラ

イ指示やスチール禁止指示(オプション)を行う必要がある。

これらの詳細については,以下の5.4リトライ指示動作,5.5スチール動作で述べる。

5.4

リトライ指示動作 EM状態のブロックに対して,外部のデバイスがアクセスした場合にそのアクセ

スを一時中断させる動作である。リトライ指示のために専用の信号線RETRY*が用意されている。

RTY*信号をアサートする条件は,以下の四つである。

1) EM状態のキャッシュデータに対して,他の機能ユニットがアクセスした場合。

2) 過渡状態にあるキャッシュデータに対して,他の機能ユニットがアクセスした場合(ただし,ISU状態

で他の機能ユニットが同一データをリードするときは除く。)。

3) キャッシュ無効化コマンドを受信した他の機能ユニットがバッファフルやパリティエラーを検出した

場合。

4) バススヌープ動作を実行した他の機能ユニットがバッファフルやパリティエラーを検出した場合。

リトライ指示動作のシーケンスについては図18に示されている。

リトライ指示を受け取ったユニットは,コピーバックの終了後にアクセスを行うために,一定の待ち時

間経過後にリトライ動作を行う。この待ち時間及びリトライ回数の規定はユーザ依存とする。

5.5

スチール動作 スチール動作はスチール禁止信号STI*をサポートするシステムにだけ可能な動作で

ある。スチール機能をサポートしないシステムの場合には,以下の記述は不要とする。

スチール動作を行うことができる機能ユニットは,以下の条件を満たす必要がある。

1) スチールする以前に当該領域のアクセスにおいて,オーダ送出の2サイクル後にリトライ指示を受け

たユニットであること。

2) リトライ指示を受けたサイクルでスチール禁止信号STI*がアサートされなかったこと。

スチール動作は上記の条件を満たす機能ユニットが,EM属性のブロックをもつ機能ユニットから共有

メモリに対してコピーバックするとき,システムバス上のコピーバックデータを共有メモリと同時に受信

する動作である。これによって不要なバスアクセスを削減することができる。

リトライ指示後のコピーバック動作とスチール動作のシーケンスについて図19に示されている。

スチール禁止信号がアサートされる条件を,以下に示す。

1) 第1の機能ユニットのメモリリードコマンドに対して,第2の機能ユニットのリトライ指示動作が行

われて,まだ第2の機能ユニットのコピーバックが終了していない状態のブロックに対して,第3の

機能ユニットからモディファイ付きリードコマンドが送出されたとき。

2) メモリライトコマンドに対してリトライ指示動作が行われた場合,まだコピーバック動作が終了して

いない状態のブロックに対して第3の機能ユニットからのアクセスが行われたとき。

3) モディファイ付きリードコマンドのアンサ待ちブロックに対して,他の機能ユニットがアクセスを行

った場合。

4) メモリリードコマンドのアンサ待ちブロックに対して,他の機能ユニットからモディファイ付きリー

ドコマンドが送出されたとき。

備考 リトライ指示動作はRTY*信号のアサートする条件1)だけの要因でアサートされるわけではな

いので,リトライ指示されたとき必ずしもスチール動作できるわけではない。スチールできな

いときは,一定の待ち時間経過後は自らリトライ動作を行う必要がある。

5.6

キャッシュデータ管理と状態遷移

54

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.6.1

ライトスルーのキャッシュ 機能ユニット内のキャッシュは共有メモリとのコヒーレンシを保つ

ためにバス,スヌープ機能を備える必要がある。すなわち,メモリを共有するすべての機能ユニットはシ

ステムバス上のコマンドとアドレスのデータを監視して,共有メモリでのデータの更新が行われ,当該ブ

ロックがキャッシュ内に存在していた場合,このエントリを無効化する。

キャッシュ無効化コマンド,モディファイ付きリードコマンドの場合も同様である。

コピーバックキャッシュとの混在時には,最新のデータブロックに対してリード/ライトするために,

リトライ動作をサポートする必要がある。すなわち,アクセス時にRTY*信号がアサートされた場合ライ

トスルーキャッシュをもつ機能ユニットはバス上に送出したリード/ライト処理のリトライを行う必要が

ある。

ライトスルーのキャッシュデータは,以下に示す2種類のキャッシュ内部状態及び1種類の過渡状態で

管理される。

1) I(無効)状態 キャッシュ上に最新のデータが登録されていない状態である。この状態のときは,シ

ステムバス上のコマンド/アドレスに対して何ら反応しない。

また,CPUからの書き込み要求に対しては,当該ブロックを読み込むことはない。書き込みデータ

を外部共有メモリにライトするだけである。

システムリセット時には,すべてのブロックはこの状態でなければならない。

2) SU(共有未変更)状態 エントリに有効な情報が登録されている状態である。ライトスルーであるの

で,外部の共有メモリと内容は常に一致している。

CPUからの書き込み要求に対してはキャッシュを書き換えるとともにシステムバスを介して共有

メモリも書き換える。

3) ISU (I⇒SU) の状態 リードミスヒット時のブロック受信待ち状態である。ブロックの属性としてはま

だI状態である。システムバス上で同一ブロックに対してアクセスが行われないかどうか監視する必

要がある。他の機能ユニットのリードアクセス以外のすべてのアクセスに対して,リトライ指示を行

う。他の機能ユニットのライトミスヒット時のブロックリードに対してはスチール禁止指示(オプシ

ョン)を行う。

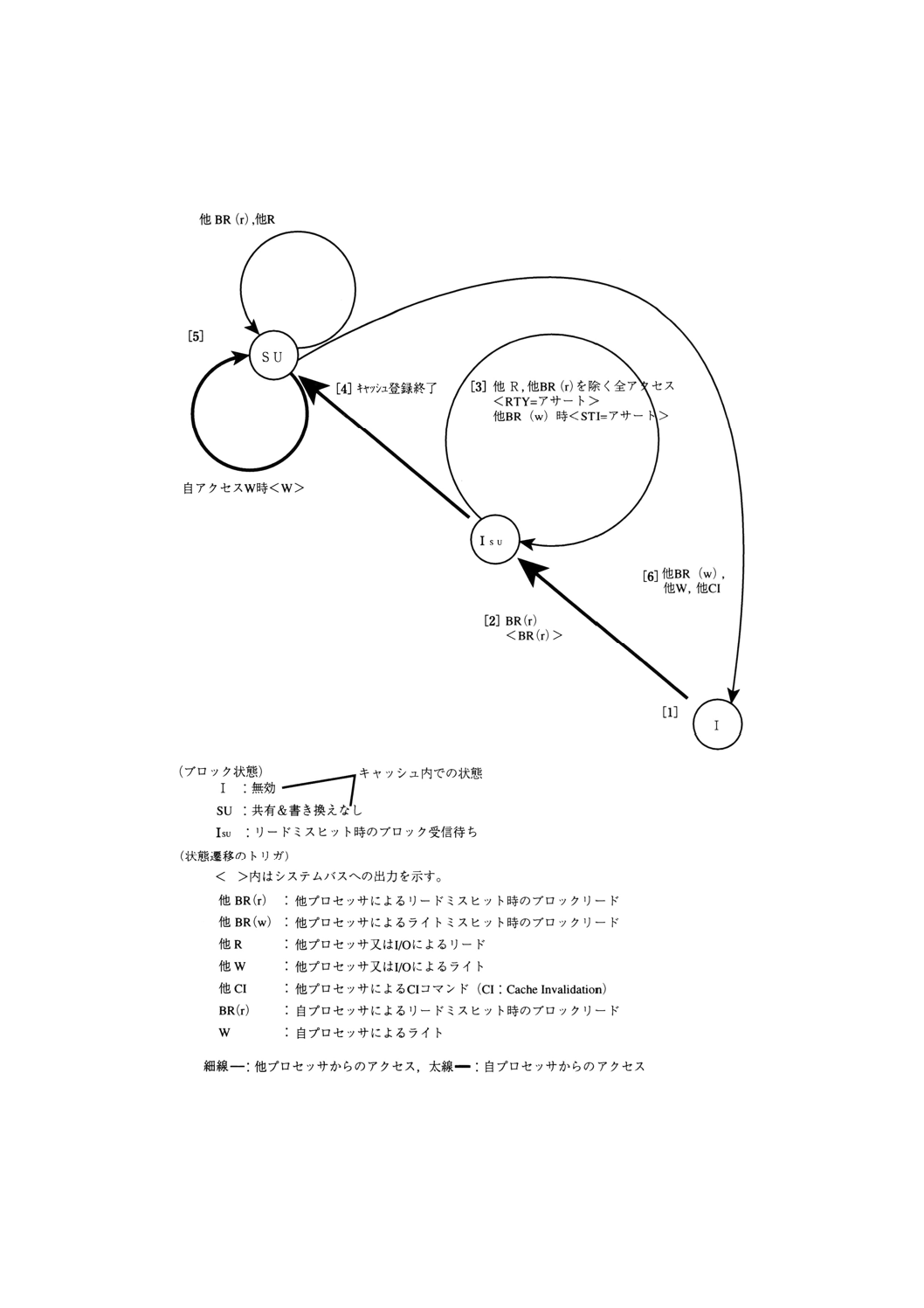

図24にSTbusのライトスルーキャッシュ一致制御プロトコルを示す。

[1] : I状態である。システムバスの任意のコマンドに対して何ら反応しなくてよい。

[2] : CPUからのリード要求に対して必要な情報がキャッシュに登録されていない場合,リードミスによ

るブロックリードオーダコマンドを発行する。

これによってISUの過渡状態になる。

[3] : ISU状態である。他の機能ユニットがシステムバス上で同じブロックアドレスに対してアクセスしな

いように監視する。もし,リード以外のアクセスが行われた場合はリトライ指示信号をアサートし

て他の機能ユニットのアクセスを一時保留する。

他の機能ユニットのライトミスヒット時のブロックリードに対してはスチール禁止指示(オプシ

ョン)を行う。

[4] : 共有メモリからのアンサをキャッシュに登録してSU状態になる。

[5] : SU状態である。他の機能ユニットのシステムバスコマンドを監視する必要がある。

他の機能ユニットのリードコマンドやブロックリードコマンドを認めた場合にもSU状態から遷

移する必要はない。また,自らのライトについてはライトコマンドをシステムバス上に送出する。

送出後の状態もSUのままである。

55

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

[6] : SU状態のブロックの領域へのライトコマンド,キャッシュ無効化コマンド,モディファイ付きリー

ドコマンドを検出した場合と,CPUからのリード要求によって別のブロックに置き換わった場合,I

状態に遷移する。

図24 STbusのライトスルーキャッシュ一致制御プロトコル

56

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.6.2

コピーバックキャッシュ コピーバックキャッシュでは,共有メモリのデータが機能ユニットで更

新されても,キャッシュだけでデータを更新し,直ちには共有メモリには反映しない。したがってキャッ

シュのコヒーレンシを維持するために,5.4リトライ指示動作や5.5スチール動作(オプション)のキャッ

シュ一致制御プロトコルをサポートする。

コピーバックのキャッシュデータは,以下に示す3種類のキャッシュ内部状態及び4種類の過渡状態で

管理される。

1) I(無効)状態 エントリとして有効な情報が登録されていない状態である。この状態のときは,シス

テムバス上のコマンド/アドレスに対して何ら反応はしない。システムリセット時には,すべてのブ

ロックはこの状態でなければならない。

2) SU(共有未変更)状態 エントリに有効な情報が登録されており,外部の共有メモリと内容が一致し

ている状態である。CPUからの読み込み要求の対象領域がこの状態であった場合,システムバスへの

アクセスは行わない。

3) EM(非共有変更)状態 エントリとして有効な情報が登録され,外部共有メモリと内容が一致して

いない状態である。この状態では,システムバス上のコマンドを監視しEM状態のブロックへのライ

トコマンド,リードコマンド,モディファイ付きリードコマンドを検出した場合は,RTY*信号をアサ

ートしアクセスを一時中断させ,書き戻しを行わなければならない。

CPUからの読み込み要求,書き込み要求の対象がこの状態であった場合,システムバスへのアクセ

スは行わない。

CPUからのアクセスによって,リプレースされる領域がこの状態であった場合は,共有メモリに対

して対象ブロックを書き戻さなければならない。

4) ISU (I⇒SU) の状態 リードミスヒット時のアンサ受信待ち状態である。システムバス上で同一ブロッ

クに対してアクセスが行われていないかどうか監視する。この状態のブロックに対する他の機能ユニ

ットの通常のリードアクセス以外のすべてのアクセスに対して,リトライ指示を行う。

他の機能ユニットのライトミスヒット時のブロックリードに対してはスチール禁止指示(オプショ

ン)を行う。

5) IEM (I⇒EM) の状態 ライトミスヒット時のアンサ受信待ち状態である。システムバス上で同一ブロ

ックに対してアクセスが行われていないかどうか監視する。

この状態のブロックに対する他の機能ユニットのすべてのアクセスに対して,リトライ指示,キャ

ッシュデータのスチール禁止指示(オプション)を行う。

6) EMSU (EM⇒SU) の状態 他の機能ユニットによるリードアクセスに対して,EM状態の最新データを

機能ユニット内のキャッシュに保持している場合,他の機能ユニットに対するリトライ動作指示をし

てから当該データをコピーバックするまでの過渡状態である。

システムバス上で同一ブロックに対してアクセスが行われていないかどうか監視する必要がある。

他の機能ユニットのすべてのアクセスに対して,リトライ指示を行う。

また,他の機能ユニットのライトミスヒットに対してはコピーバック時のスチール禁止指示(オプ

ション)を行う。

7) EMI (EM⇒I) の状態 他のプロセッサによるライトアクセスに対して,EM状態の最新データを機能

ユニット内のキャッシュに保持している場合,他の機能ユニットに対するリトライ動作指示をしてか

ら当該データをコピーバックするまでの過渡状態である。

システムバス上で同一ブロックに対してアクセスが行われないかどうか監視する必要がある。

57

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

他の機能ユニットのすべてのアクセスに対して,リトライ指示,キャッシュデータのスチール禁止

指示(オプション)を行う。

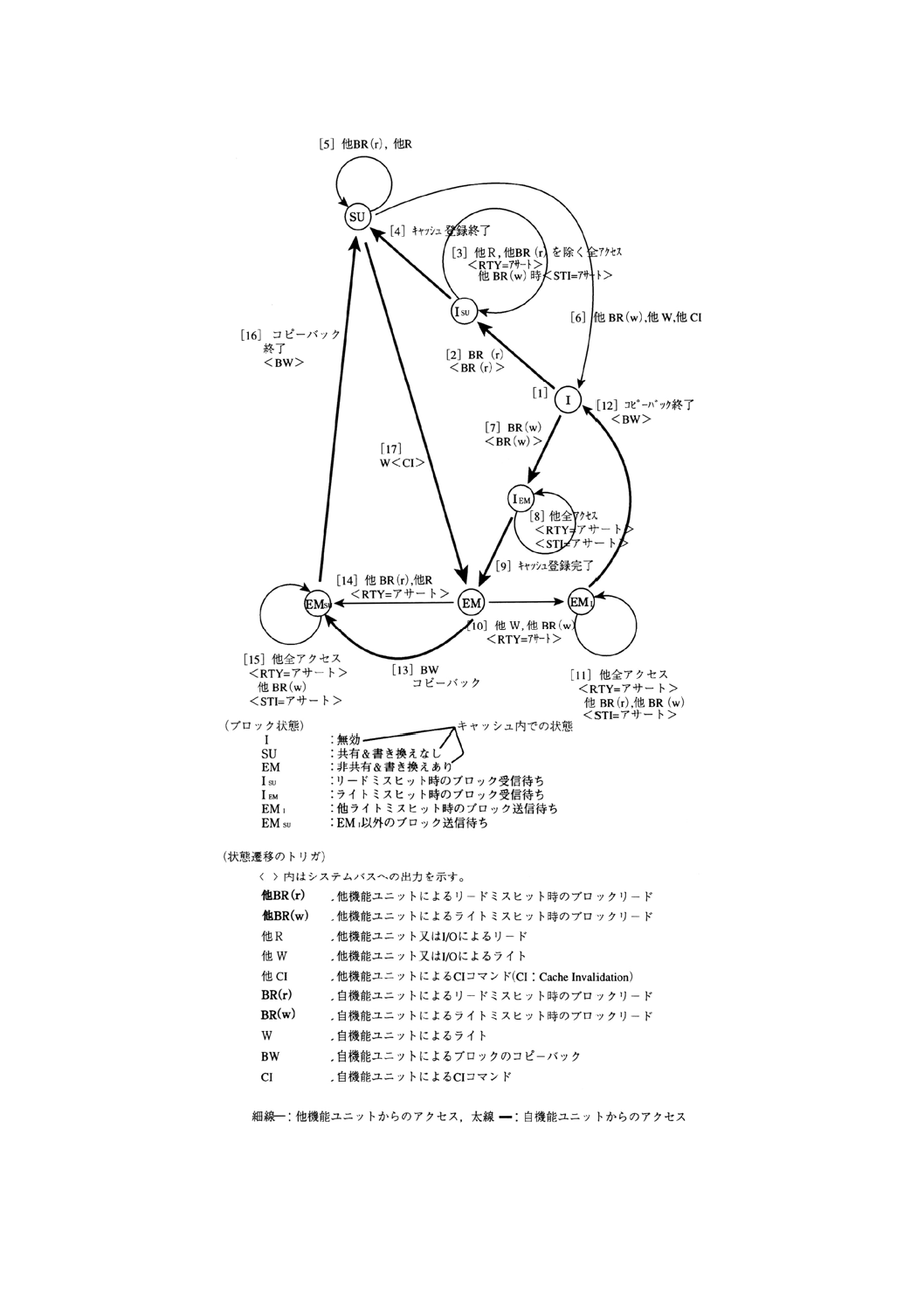

図25にSTbusのコピーバックキャッシュ一致制御プロトコルを示す。

[1] : I状態である。システムバスの任意のコマンドに対して何ら反応しなくてよい。

[2] : CPUからのリード要求に対して必要な情報がキャッシュに登録されていない場合,リードミスによ

るブロックリードオーダを発行する。これによってISUの過渡状態となる。

[3] : ISU状態である。他の機能ユニットの同一ブロックのアクセスを監視して,もし通常のリード以外の

アクセスが行われた場合は,リトライ指示信号をアサートして他の機能ユニットのアクセスを一時

保留する。他の機能ユニットのライトミスヒット時のブロックリードに対してはスチール禁止指示

(オプション)を行う。

[4] : 共有メモリからのアンサデータをキャッシュに登録してSU状態になる。

[5] : SU状態である。他の機能ユニットのシステムバスコマンドを監視する。

他の機能ユニットのリードコマンドやブロックリードコマンドを認めた場合にもSU状態から遷

移しない。

[6] : システムバス上に,登録されたブロックの領域へのライトコマンド,キャッシュ無効化コマンド,

又はモディファイ付きリードコマンドを検出した場合とCPUからのリード要求によって,別のブ

ロックに置き換わった場合,I状態に遷移する。

[7] : CPUからのライト要求に対して必要な情報がキャッシュに登録されていない場合,共有メモリへは

モディファイ付きのリードオーダを発行する。これによってIEM状態の過渡状態になる。

[8] : IEM状態である。他の機能ユニットがシステムバス上で同じブロックアドレスに対して,アクセス

しないように監視する。もしアクセスが行われた場合はリトライ指示信号,スチール禁止指示信号

(オプション)をアサートして他の機能ユニットのアクセスを一時保留にする。

[9] : 共有メモリからのアンサブロックを登録する。読み込んだブロックに対して,CPUからのライトを

反映し,ブロックの状態はEM状態となる。

[10] : CPUからのアクセスによって別の領域に置き換えられた場合,他のキャッシュ/入出力装置の共有

メモリへのライトコマンド,モディファイ付きリードコマンドに対して,リトライ指示信号をアサ

ートして中断する。これによってEMIの過渡状態になる。

[11] : EMI状態である。他の機能ユニットの同一ブロックのアクセスを監視して,もしアクセスが行われ

た場合はリトライ指示信号をアサートして他の機能ユニットのアクセスを一時保留にする。同時に

スチール禁止指示(オプション)をアサートしてコピーバック動作の際,スチール動作も行われな

いようにする。

[12] : 共有メモリへのブロックのコピーバックのためのブロックライトコマンドを送出する。キャッシュ

のデータは無効となり,I状態に遷移する。

[13] : CPUからのアクセスによって,リプレースされる領域がEM状態であった場合,共有メモリに対し

て対象ブロックを書き戻さなければならない。これによってEMSUの過渡状態になる。

[14] : 他の機能ユニットからの共有メモリへのリードコマンドに対して,リトライ指示信号をアサートし

て中断する。これによってEMSUの過渡状態になる。

[15] : EMSU状態である。他の機能ユニットの同一ブロックのアクセスを監視して,もしアクセスが行わ

れた場合はリトライ指示信号をアサートして他の機能ユニットのアクセスを一時保留する。同時に

他の機能ユニットのモディファイ付きリードコマンドに対してはコピーバック時のスチール禁止

58

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

指示(オプション)を行う。

[16] : 共有メモリへのブロックのコピーバックのためのブロックライトコマンドを送出する。キャッシュ

のブロックは登録されたままであり,SU状態に遷移する。

[17] : CPUからの書き込み要求の対象領域がSUであった場合,システムバスにキャッシュ無効化コマン

ド (CI) を発行しなければならない。この場合,ブロックはEM状態に遷移する。

59

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図25 STbusのコピーバックキャッシュ一致制御プロトコル

60

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.7

メモリアクセス時の注意事項 STbus仕様では,1バスオペレーションの転送バイト数は256バイト

まで可能である。

しかし,システムがキャッシュをサポートする場合は,キャッシュコヒーレンシを維持するため,1バ

スオペレーションの転送バイト数はキャッシュのブロック長(32バイト)の影響を受ける。

メモリアクセスを行う場合には,次の制限事項を厳守しなければならない。

1) 1バスオペレーションにおけるデータ転送長の最大値は,システムのキャッシュのブロックサイズ以

下でなければならない。

2) メモリアクセスにおいて,メモリアドレスがキャッシュブロックサイズの境界になく,かつメモリア

ドレスと転送長の関係がキャッシュブロックサイズの境界をまたぐ場合には,キャッシュブロックサ

イズ内でラップアラウンドしてデータを転送すること。このとき,4.2.2で示したバイトアラインメン

トは成立しない(Wの値は無効)。

3) I/Oアダプタがメモリアクセスを行う場合は,メモリアドレスと転送長の関係がキャッシュブロック

サイズをまたぐことを禁止する。

備考 3)の制限はI/Oアダプタの流通性を考慮してSTbusの共通仕様として位置付ける。

6. 高信頼化機能 フォールト・トレラントなシステムを構築するために,以下の機能がシステムバスに

必要とされる。

1) 冗長構成

2) 障害検出

3) 障害波及の防止

4) 障害処理・診断のサポート

6.1

冗長構成

1) パリティの付与 STbusは信号の1ビット・エラーを検出するためにパリティをもっている。

コマンド/アドレス/データのマルチプレクスされた情報転送バスAD [00..63] *に対してバイト単

位にパリティ信号線AD [0..7] *を付与している。また,制御信号線BS*,BUR*に対してもCSP*のパリ

ティ信号を付与している。

2) 信号の2重化構成 キャッシュ関連の制御信号RTY*,STI*,LCK*について,個々の信号に対して1

ビット・エラーを訂正できる2重化構成をとっている。

すなわち,RTY*,STI*,LCK*のベース信号に対して,それぞれのスペア信号線としてRTYS*,STIS*,

LCKS*を備えている。

さらにそれぞれのベース信号とスペア信号で不一致が生じた場合の各信号の意味付けは,表9に示

すように定義されている。

意味付けは不一致が起きた場合の安全優位性から決定されている。

表9 ベース信号とスペア信号が不一致した場合の意味付け

(a) RTY* and STI*の場合

ベース信号

スペア信号

状態

意味付け

RTY*

STI*

0

0

一致

0:ネゲート

0

1

不一致

1:アサート

1

0

不一致

1:アサート

1

1

一致

1:アサート

61

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表9 (続き)

(b) LCK*の場合

ベース信号

スペア信号

状態

意味付け

LCK*

0

0

一致

0:ネゲート

0

1

不一致

0:ネゲート

1

0

不一致

0:ネゲート

1

1

一致

1:アサート

6.2

障害検出

1) アンサによるエラー検出 システムバス上の転送中に検出される異常については,表7に示されてい

るように,以下のものがある。

・ Hardware error

・ Illegal command

・ Bus sequence error

これらの異常はDUTによって検出される。

また,異常の際の動作シーケンスについては,4.8.1アンサによって報告される異常処理を参照のこ

と。

2) タイムアウトによるエラー検出 タイムアウトによって検出可能なエラーとして,以下のものがある。

・ SUTが一定時間内にバスを獲得できない。

・ SUTが一定時間内に送出済のオーダに対するアンサを獲得できない。

これらの異常の検出は各機能ユニット内のバスインタフェース制御部 (BIC) によって検出される。

また,異常の際の動作シーケンスについては,4.8.2その他の異常処理を参照のこと。

6.3

障害波及の防止 機能ユニットで発生した障害は,システムバスを経由して他の機能ユニットに波

及するおそれがある。これを防止するためにSTbusは障害を起こした機能ユニットからのバスアクセスを

禁止する機能(アイソレーション機能)をもつ。アイソレーション機能は,以下のとおりである。

STbusは,これらの目的のためにシリアルバスを設けてもよい。

・ 機能ユニットの障害が検出され,上記シリアルバスにてバスハンドラに通知された場合,バスハン

ドラはその機能ユニットに対して,バス使用許可信号 (GR*) を返送しない。

・ 上記シリアルバスにて機能ユニットに対しアイソレーション指示を与えることでバス使用要求を出

力しない。

以上の機能によって,障害機能ユニットのどの信号もバスから電気的に遮断することができる。こうし

て,障害がバスを通して波及するのを防止することができる。

6.4

障害処理・診断のサポート

1) 障害処理 タイムアウト機能で検出されたエラーについては,検出の時点で要因別に細分化されてい

る。ハードウェア又はソフトウェアは,これらの要因に従ってエラーの要因を解析し,障害処理を行

える。

2) ログアウト情報の収集・故障箇所の診断 エラーが軽度の場合,ハードウェアのリトライ動作で解消

できる場合もある。しかし,軽度のエラーに見えてもシステムに重大な影響を与える場合がある。シ

ステムバス全般の障害を総合的に把握するためには,定期的にログアウト情報の収集を行ったり,ソ

フトウェアによる障害の解析を行うことが必要である。また,重大なエラー発生時には,故障被疑箇

所の診断を行う必要がある。

62

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

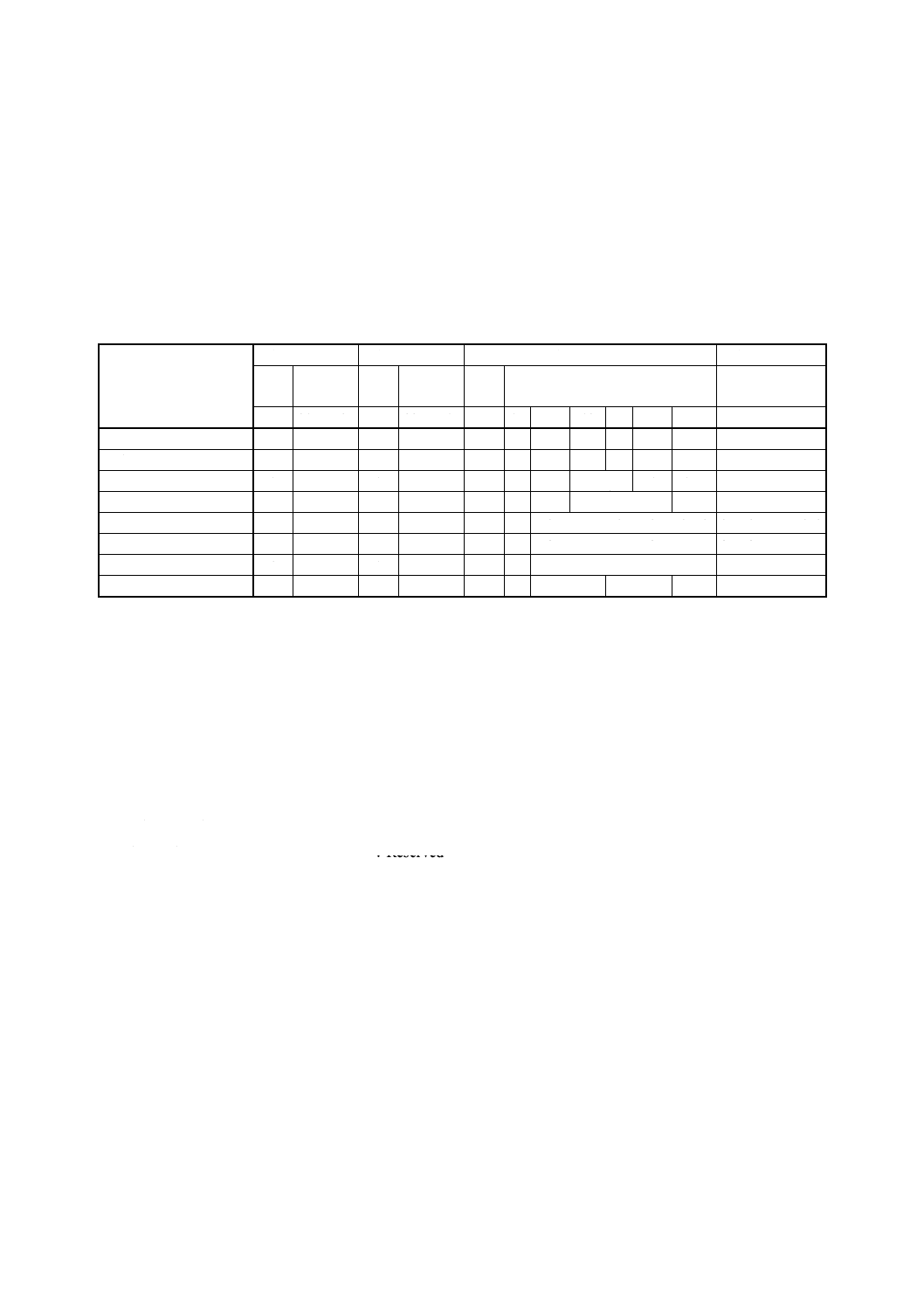

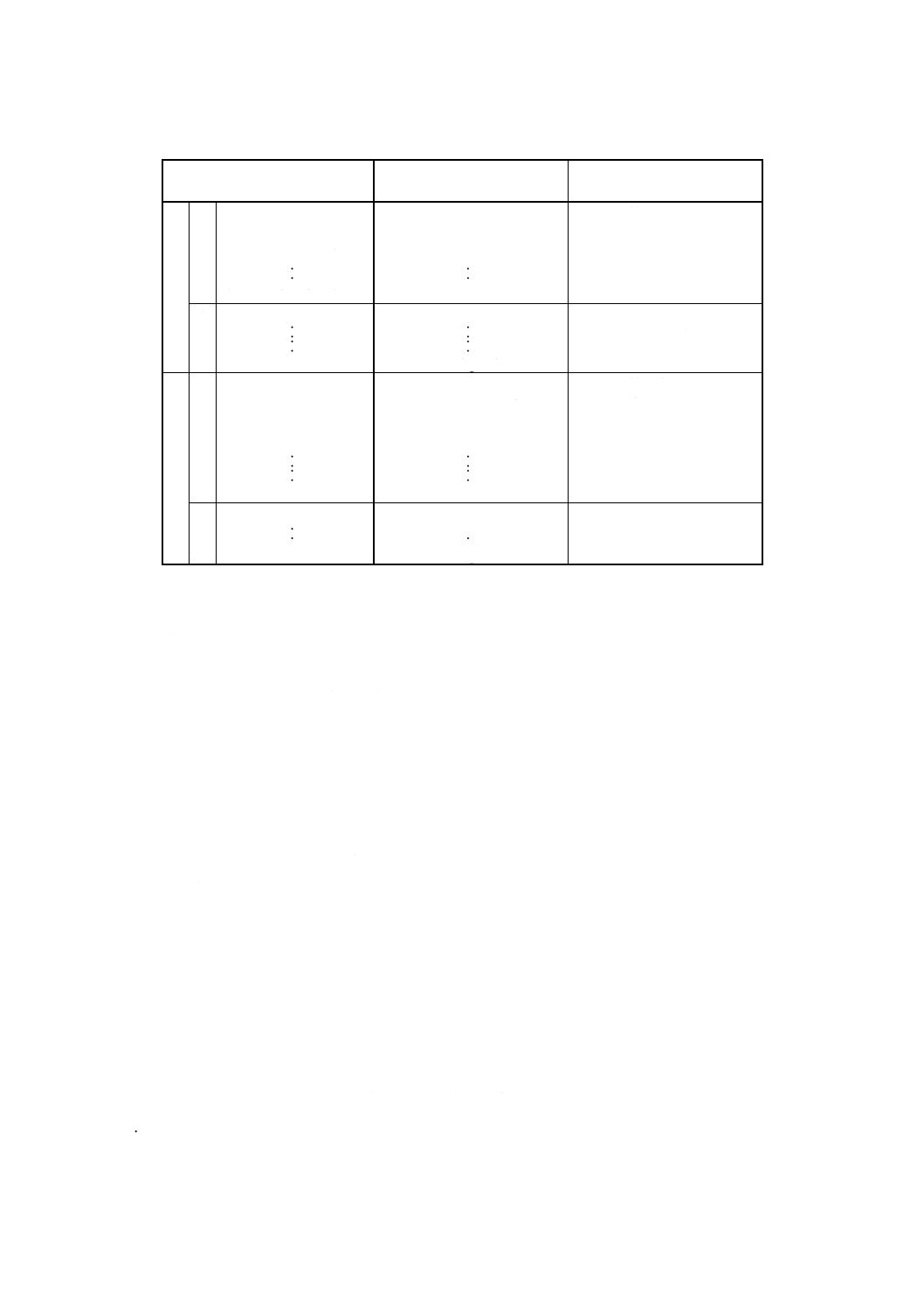

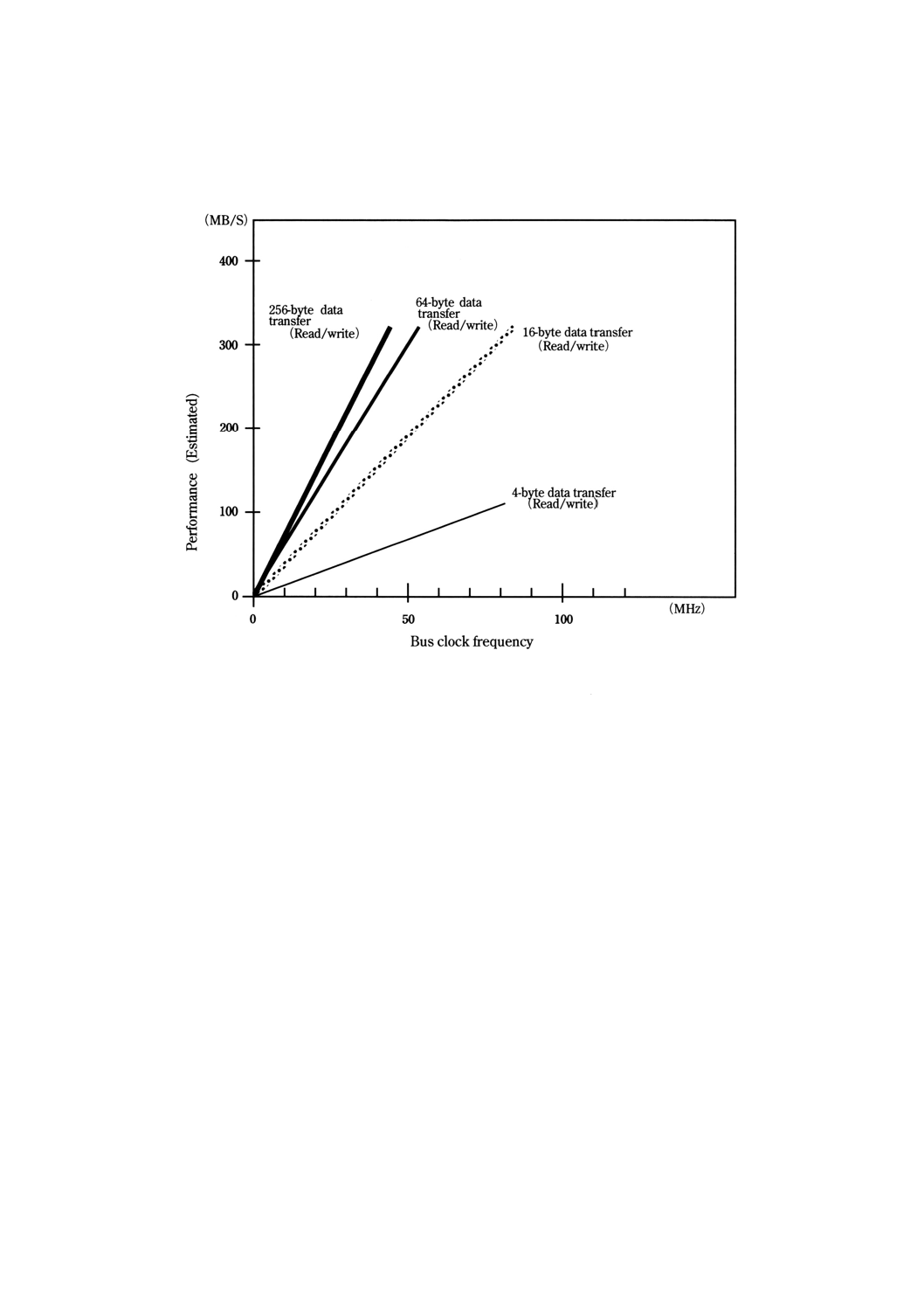

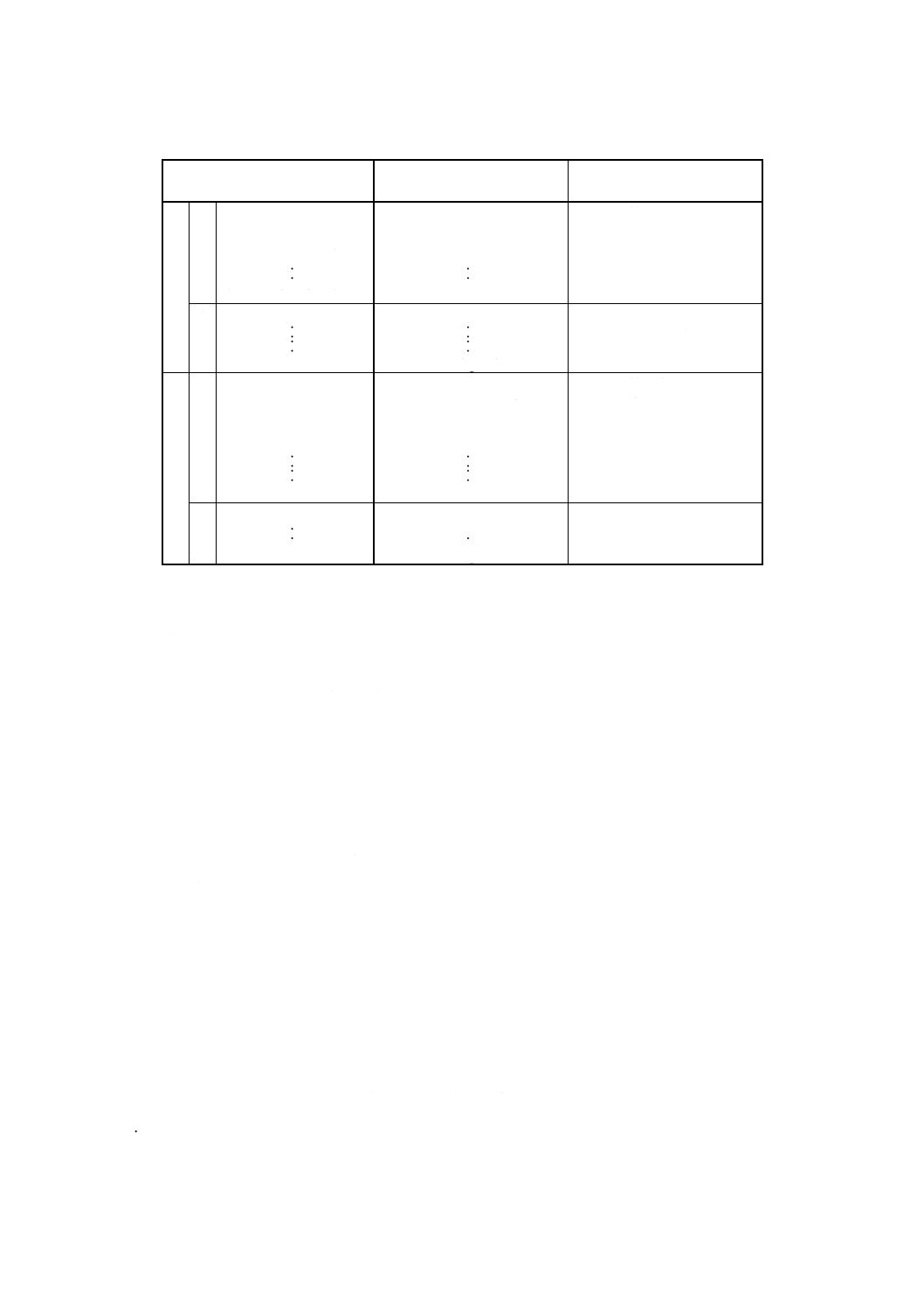

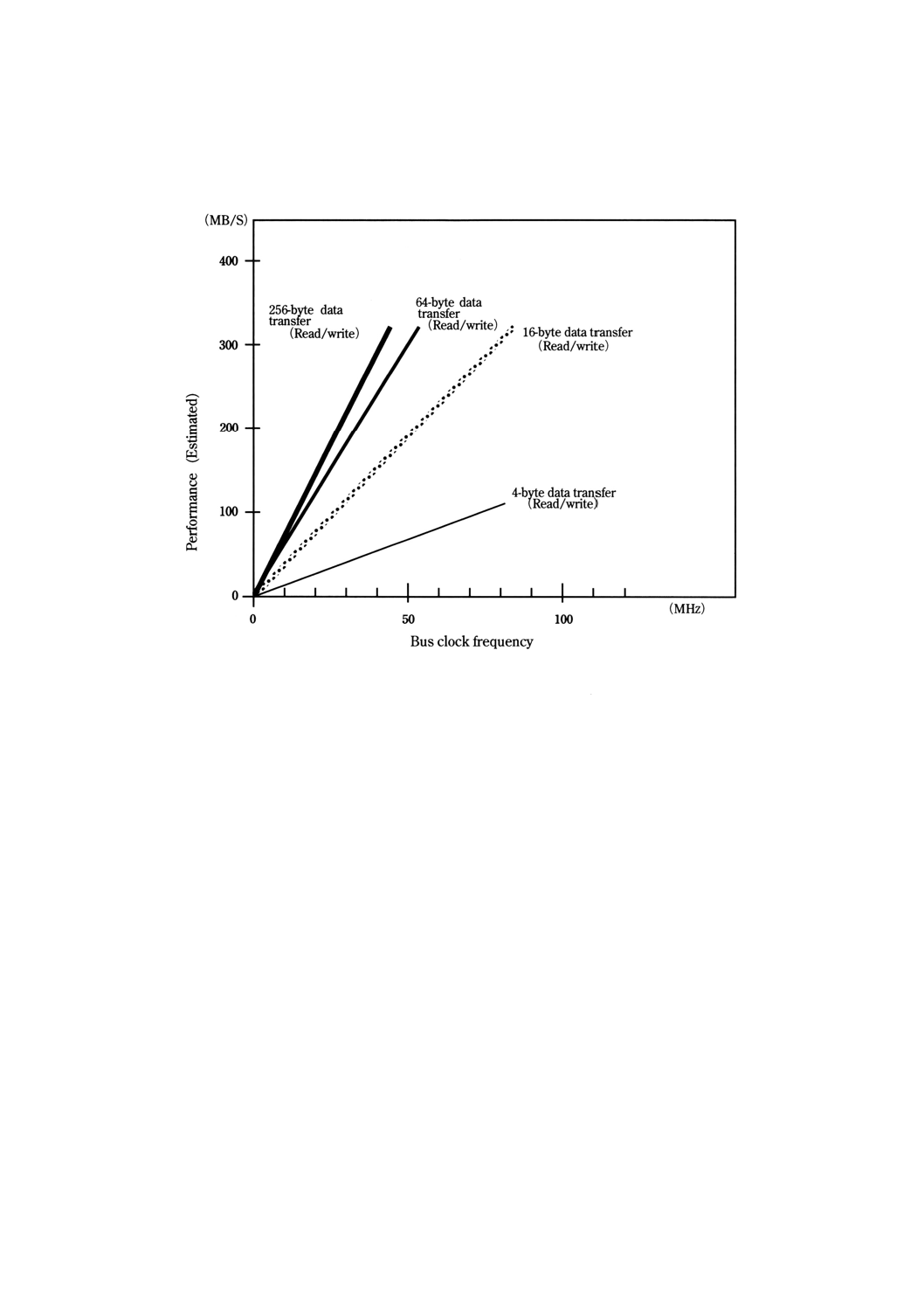

附属書A(参考) 性能(推定)

図A.1 STbus performance

(8-byteバス幅で,かつ32-bitアドレッシングの場合)

63

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

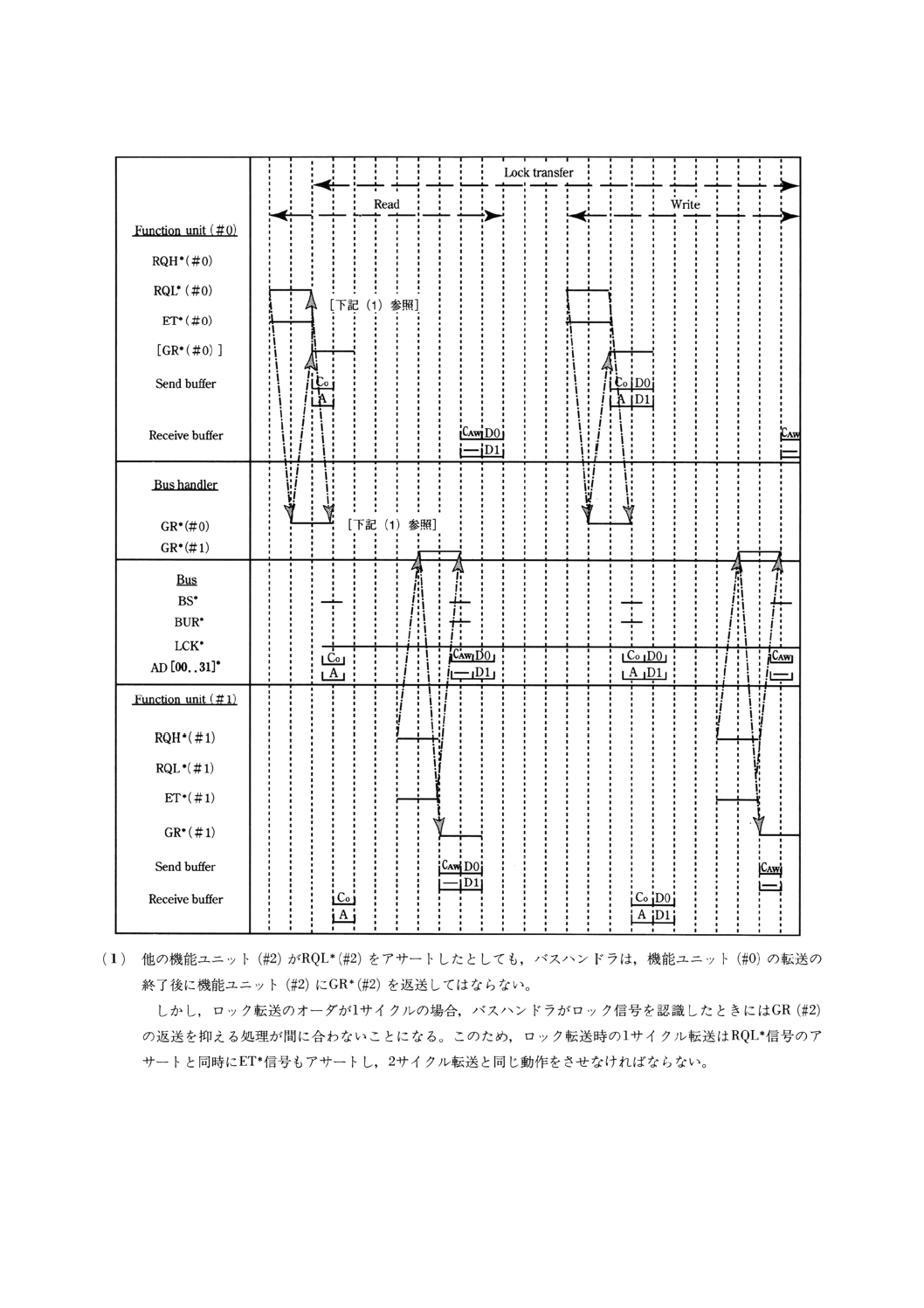

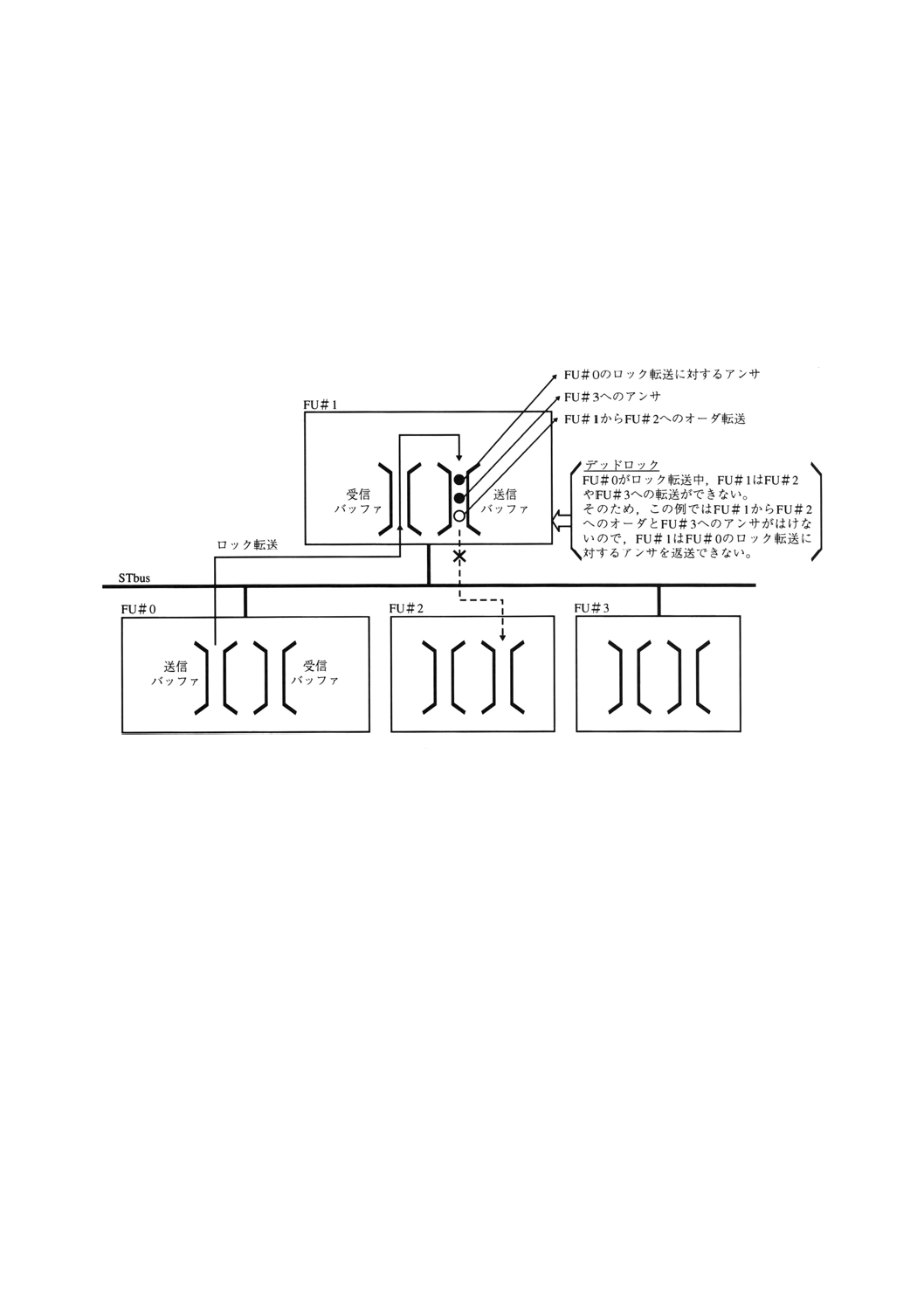

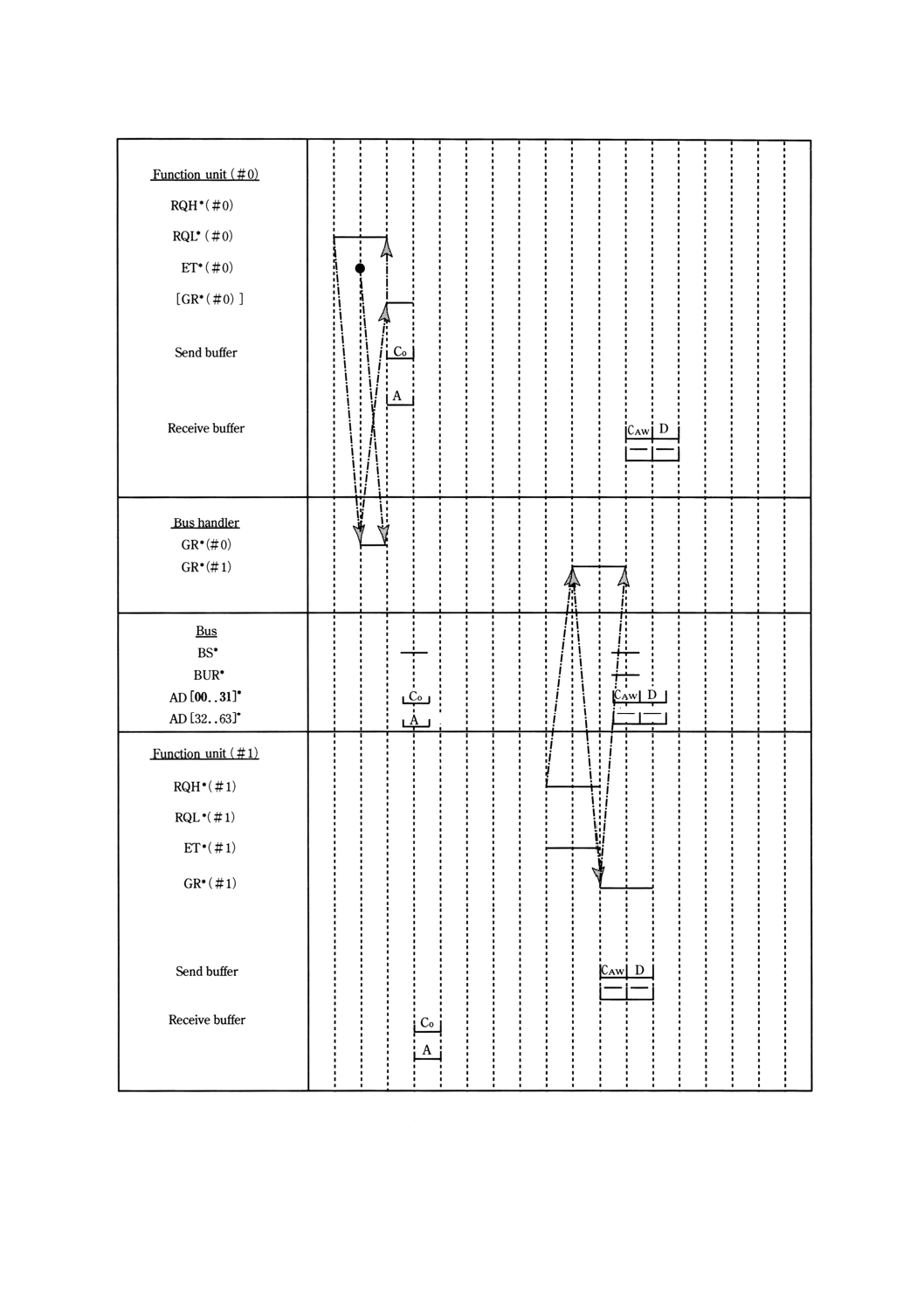

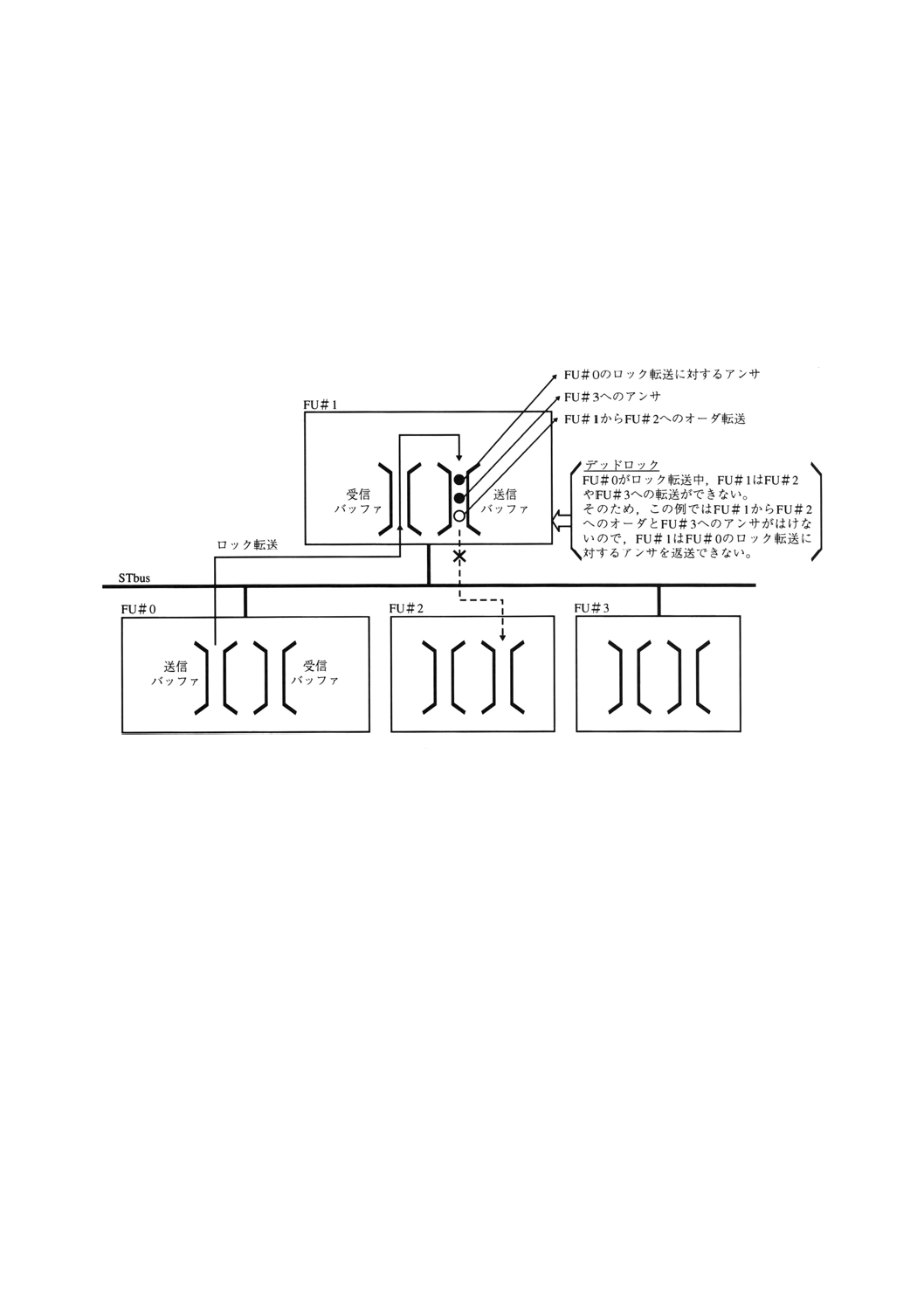

附属書B(参考) ロック転送時のアンサ返送

機能ユニット#0 (FU#0) が,FU#1との間でロック転送を実行するとする。

ロック転送中は,当該のロック転送にかかわる転送以外は実行できないため,FU#1はFU#0以外への転

送は実行しない。

しかし,図B.1の例では,FU#0のロック転送に対するアンサを返送できず,デッドロックが生じる。こ

の問題を解決するためにロック中でもアンサに対してバス権を与え,さらにアンサはオーダを追い越せる

よう,送信バッファ制御部を設計する必要がある。

図B.1 デッドロック問題の例

64

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

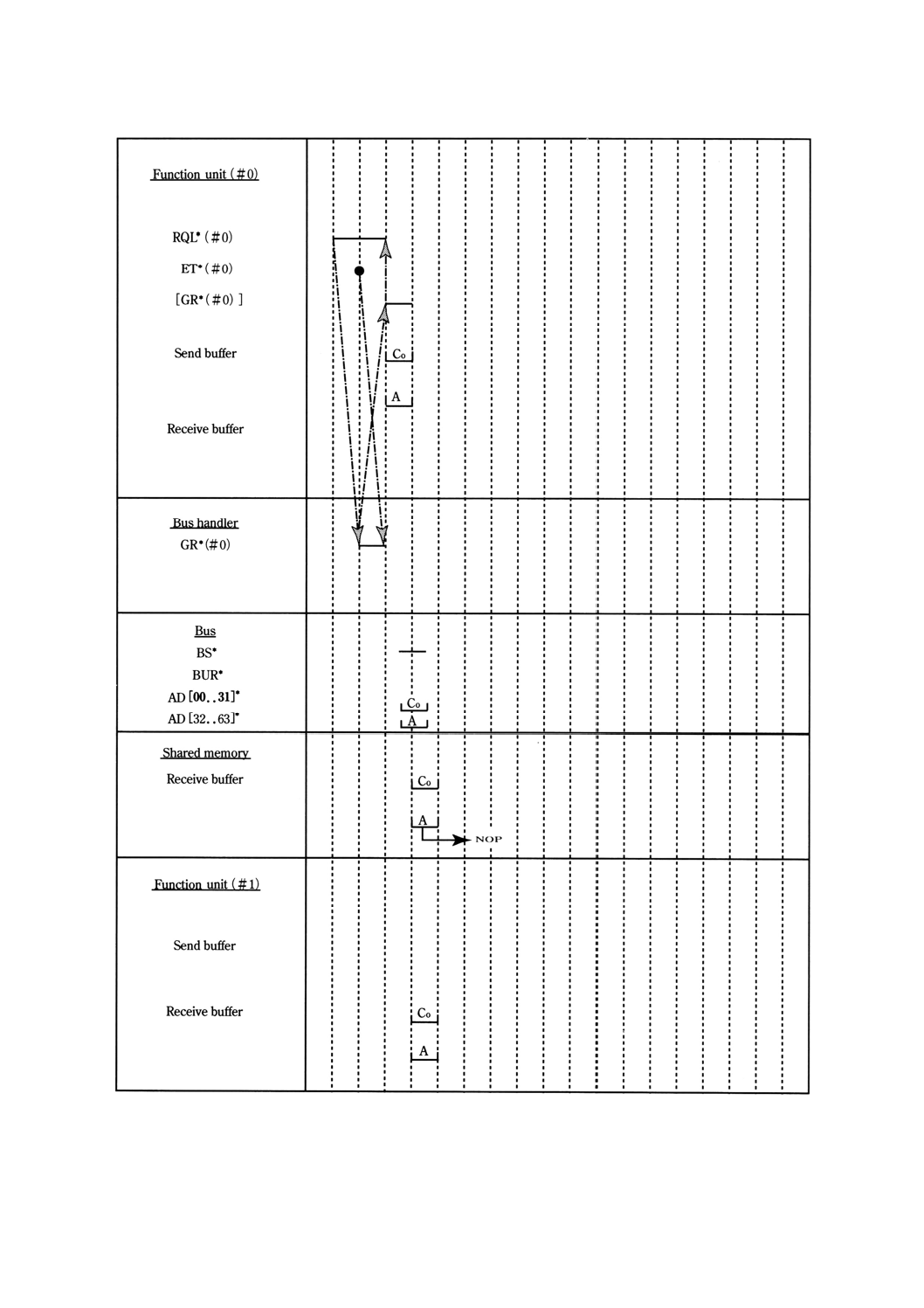

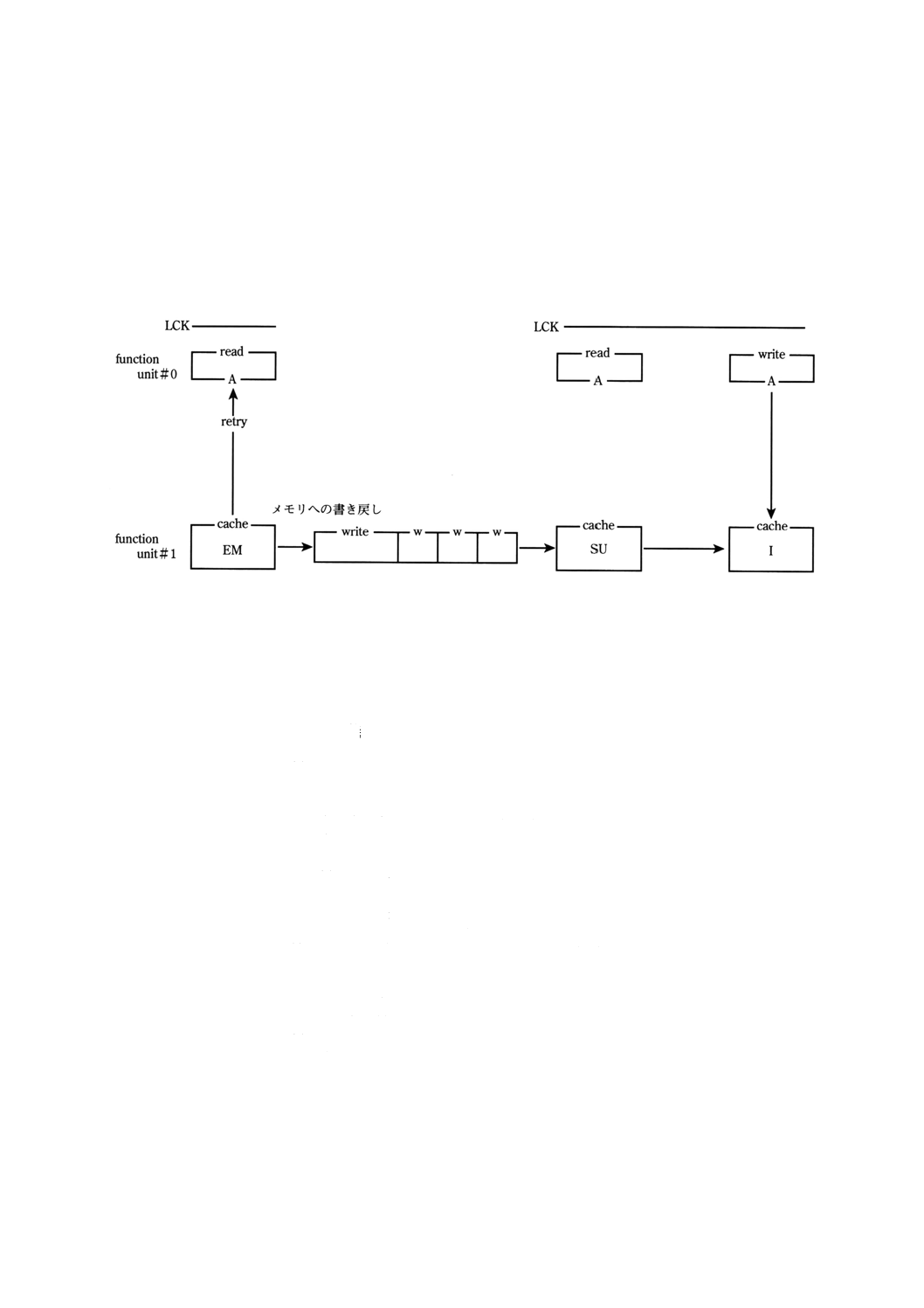

附属書C(参考) ロック転送とコピーバックキャッシュの書き戻し

他ボード内のEM(非共有変更)状態のキャッシュデータに対しロック転送を実行する場合,EM状態の

キャッシュデータをメモリに書き戻す必要がある。

解決策として,リトライ機能によってロック転送をいったん中断して(ロック信号をいったんネゲート

して),その間に書き戻しサイクルを実行し,その後,ロック転送を再開する方法がある。

図C.1 EM状態のキャッシュデータへのロック転送方法

JIS原案作成委員会 構成表

JTC1/SC26国内対策専門委員会

氏名

所属

(委員長)

脇 村 慶 明

日本電信電話株式会社NTTネットワークサービスシステム研究所

(委員)

岡 田 勝 行

日本電信電話株式会社NTTネットワークサービスシステム研究所

森 義 一

沖電気工業株式会社電子デバイス事業本部

浪 本 敬 二

株式会社東芝半導体事業本部

川 村 善 久

日本ディジタルイクイップメント株式会社標準化推進室

藤 崎 正 人

日本電気株式会社技術企画部

永 尾 春 樹

日本電気株式会社半導体ソリューション技術本部

中 島 真 人

日本電気株式会社技術企画部

茶 木 英 明

株式会社日立製作所半導体事業部

内 山 邦 男

株式会社日立製作所中央研究所

藤 川 悟

松下電器産業株式会社マルチメディア開発センター

松 井 秀 夫

三菱電機株式会社マイコンASIC事業統括部

漆 山 隆

富士通株式会社LSI商品事業本部

田 島 守 彦

電子技術総合研究所知能情報部

渡 部 庄 吾

社団法人日本電気計測器工業会技術部

桐 谷 俊 雄

社団法人日本事務機械工業会標準部

永 松 荘 一

通商産業省機械情報産業局電子機器課

安 延 申

通商産業省機械情報産業局情報処理振興課

加 山 英 男

財団法人日本規格協会技術部

橋 爪 邦 隆

工業技術院標準部

(事務局)

東 條 喜 義

社団法人日本電子工業振興協会技術部

安 藤 茂 樹

社団法人日本電子工業振興協会技術部

65

X 6801 : 1998

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

JTC1/SC26/WG12 (STbus) 国内対策委員会

氏名

所属

(主査)

岡 田 勝 行 日本電信電話株式会社NTTネットワークサービスシステム研究所

(委員)

脇 村 慶 明 日本電信電話株式会社NTTネットワークサービスシステム研究所

田 原 保 沖電気工業株式会社第一基幹ネットワーク事業部

浪 本 敬 二 株式会社東芝半導体事業本部

加 藤 明 日本電気株式会社交換事業部プロセッサ技術部

中 島 真 人 日本電気株式会社技術企画部標準化推進部

岡 澤 宏 一 株式会社日立製作所オフィスシステム事業部

森 昭 助 富士通株式会社LSI商品事業本部第一システムLSI事業部

藤 川 悟 松下電器産業株式会社マルチメディア開発センター

小 倉 匡 勝 社団法人日本事務機械工業会標準部

漆 山 隆 富士通株式会社LSI商品事業本部第一システムLSIソフトウェア部

杉 森 正 章 工業技術院標準部

(事務局)

東 條 喜 義 社団法人日本電子工業振興協会技術部

安 藤 茂 樹 社団法人日本電子工業振興協会技術部