C 5381-341:2005 (IEC 61643-341:2001)

(1)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

まえがき

この規格は,工業標準化法第12条第1項の規定に基づき,社団法人日本電子材料工業会(EMAJ)/財団

法人日本規格協会(JSA)から,工業標準原案を具して日本工業規格を制定すべきとの申出があり,日本工業

標準調査会の審議を経て,経済産業大臣が制定した日本工業規格である。

制定に当たっては,日本工業規格と国際規格との対比,国際規格に一致した日本工業規格の作成及び日

本工業規格を基礎にした国際規格原案の提案を容易にするために,IEC 61643-341:2001,Components for

low-voltage surge protective devices−Part 341:Specification for thyristor surge suppressors (TSS)を基礎として用

いた。

この規格の一部が,技術的性質をもつ特許権,出願公開後の特許出願,実用新案権,又は出願公開後の

実用新案登録出願に抵触する可能性があることに注意を喚起する。経済産業大臣及び日本工業標準調査会

は,このような技術的性質をもつ特許権,出願公開後の特許出願,実用新案権,又は出願公開後の実用新

案登録出願にかかわる確認について,責任はもたない。

JIS C 5381-341には,次に示す附属書がある。

附属書A(規定)特殊な使用条件

附属書B(参考)基準インパルス波形による米国審査基準

C 5381-341:2005 (IEC 61643-341:2001)

(2)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

目 次

ページ

序文 ··································································································································· 1

1. 適用範囲 ························································································································ 1

2. 引用規格 ························································································································ 1

3. 用語,文字記号及び定義 ··································································································· 2

3.1 パラメータの用語,文字記号及び定義················································································ 2

3.2 TSS,端子及び特性の用語並びに定義 ················································································ 6

4. 基本機能及び部品説明 ······································································································ 9

4.1 TSSの種類 ··················································································································· 9

4.2 基本デバイス構造 ········································································································· 11

4.3 デバイス等価回路 ········································································································· 12

4.4 スイッチング象限特性 ··································································································· 13

4.5 TSSの性能基準 ············································································································ 14

4.6 追加のTSS構造············································································································ 16

5. 標準試験方法 ················································································································· 18

5.1 試験条件 ····················································································································· 18

5.2 使用条件 ····················································································································· 19

5.3 故障及び不良モード ······································································································ 20

5.4 定格試験手順 ··············································································································· 21

5.5 特性試験手順 ··············································································································· 27

附属書A(規定)特殊な使用条件 ··························································································· 49

附属書B(参考)基準インパルス波形による米国審査基準 ··························································· 50

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

日本工業規格 JIS

C 5381-341:2005

(IEC 61643-341:2001)

低圧サージ防護デバイス用

サージ防護サイリスタ(TSS)の試験方法

Components for low-voltage surge protective devices−

Part 341:Specification for thyristor surge suppressors (TSS)

序文 この規格は,2001年に第1版として発行されたIEC 61643-341,Components for low-voltage surge

protective devices−Part 341:Specification for thyristor surge suppressors (TSS)を翻訳し,技術的内容及び規格票

の様式を変更することなく作成した日本工業規格である。

1. 適用範囲 この規格は,クリッピング及びクローバ動作によって過電圧を抑制し,サージ電流を分流

するように設計した低圧サージ防護デバイス用サージ防護サイリスタ(以下,TSSという。)の試験方法

について規定する。これらの部品は,サージ防護デバイスの構成部品として使用し,特に電気通信分野に

適用する。

この規格は,次の事項からなる。

− 用語,記号及び定義

− 基本機能,外形及び部品構造

− 使用条件及び故障モード

− 定格及び特性試験

備考 この規格の対応国際規格を,次に示す。

なお,対応の程度を表す記号は,ISO/IEC Guide21に基づき,IDT(一致している),MOD(修

正している),NEQ(同等でない)とする。

IEC 61643-341:2001,Components for low-voltage surge protective devices−Part 341:Specification for

thyristor surge suppressors (TSS) (IDT)

2. 引用規格 次に掲げる規格は,この規格に引用されることによって,この規格の規定の一部を構成す

る。これらの引用規格は,その最新版(追補を含む。)を適用する。

JIS C 60721-3-3 環境条件の分類 環境パラメータとその厳しさのグループ別分類 屋内固定使用の

条件

備考 IEC 60721-3-3:1994,Classification of environmental conditions−Part 3: Classification of groups of

environmental parameters and their severities−Section 3: Stationary use at weatherprotected

locationsが,この規格と一致している。

JIS C 60721-3-9 環境条件の分類 環境パラメータとその厳しさのグループ別分類 製品内部の環境

条件

備考 IEC 60721-3-9:1993,Classification of environmental conditions−Part 3: Classification of groups of

2

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

environmental parameters and their severities−Section 9: Microclimates inside productsが,この規

格と一致している。

JIS C 61000-4-5 電磁両立性−第4部:試験及び測定技術−第5節:サージイミュニティ試験

備考 IEC 61000-4-5:1995,Electromagnetic compatibility (EMC)−Part 4: Testing and measurement

techniques−Section 5: Surge immunity testが,この規格と一致している。

IEC 60050(191) International Electrotechnical Vocabulary−Chapter 191: Dependability and quality of

service

IEC 60050(702) International Electrotechnical Vocabulary−Chapter 702: Oscillations, signals and related

devices

IEC 60099-4 Surge arresters−Part 4: Metal-oxide surge arresters without gaps for a.c. systems

IEC 60747-1 Semiconductor devices−Discrete devices and integrated circuits−Part 1: General

IEC 60747-2 Semiconductor devices−Discrete devices and integrated circuits−Part 2: Rectifier diodes

IEC 60747-6 Semiconductor devices−Discrete devices and integrated circuits−Part 6: Thyristors

備考 TSSは,IEC 60747-6が規定しているタイプのサイリスタとは異なった特性をもち,異なっ

た方法で使用される。これらの相違があることから,新たにこの規格を制定した。

IEC 60749 Semiconductor devices−Mechanical and climatic test methods

IEC 61083-1 Digital recorder for measurements in high-voltage impulse tests−Part 1: Requirements for

digital recorders

ITU-T Recomendation K.20 Resistibility of telecommunication switching equipment to over voltages and

overcurrents

ITU-T Recomendation K.21 Resistibility of subscribers' terminals to over voltages and overcurrents

ITU-T Recomendation K.28 Characteristics of semi-conductor arrester assemblies for the protection of

telecommunications installations

3. 用語,文字記号及び定義 この規格で用いる主な用語,記号及び定義は,次による。

3.1

パラメータの用語,文字記号及び定義 適用可能な場合,用語,文字記号及び定義については,既

存のサイリスタ規格(IEC 60747-6)及び整流ダイオード規格(IEC 60747-2)を用いる。

備考1. IEC 60747-1の5章2.1.1に,“記号V及びvは電圧を表す予備的な記号としてだけに用いる

ことをIEC 60027-1では推奨しているが,半導体デバイスの分野においては,記号V及びv

を電圧を表す記号として広く用いているため,IEC 60747-1では,これらを記号U及びuと

同レベルで扱う。”とある。この規格では,U及びuの代わりV及びvを電圧を表す記号とし

て使用する。

2. 文字記号に数種類の表現形態がある場合,最も一般的に用いている形態を第一に適用する。

3.1.1

主端子に関連する定格(Main terminal ratings) 阻止,導通及びスイッチング領域の所要性能は,

次による。

3.1.1.1

繰返しピークオフ電圧,VDRM(repetitive peak off-state voltage,VDRM) すべての直流及び繰返

し電圧要素の中で,オフ状態で印加できる最大(ピーク)定格遮断電圧。

3.1.1.2

繰返しピークオン電流,ITRM(repetitive peak on-state current,ITRM) 波形及び周波数を規定し

た交流で,連続的にオン状態で流すことができるサージ電流の最大(ピーク)定格値。

3

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.1.1.3

非繰返しピークオン電流,ITSM(non-repetitive peak on-state current,ITSM) 波形及び周波数を

規定した交流で,規定した時間又はサイクル数をオン状態で流すことができるサージ電流の最大(ピーク)

定格値。

3.1.1.4

非繰返しピークインパルス電流,IPPSM,ITSM(non-repetitive peak impulse current,IPPSM,ITSM)

規定した振幅及び波形で流すことができるピークインパルス電流の最大(ピーク)定格値。

備考 これまでこの定格に使用する記号は,複数個存在する。各記号の比較を次に示す。

IPPSM:IPPの最大又はピーク(=M)で非繰返し(=S)値を表記するので,記号表記的には適切

である。

ITSM:非繰返し(=S)電流の最大(=M)値はオン状態(=T)時に起きるとは限らないので,短

インパルスにおいては記号表記的に正確とはいえない。

IPPM:非繰返しとしてこの記号を使用することは不適切である。この記号はIPPの定格最大(=M)

繰返し値である。

IPP:定格値としてこの記号を使用することは不適切である。ピークインパルス電流の用語は,

回路パラメータであり連続する基本的に同一のパルスでのピーク電流と定義している。

3.1.1.5

繰返しピーク逆電圧,VRRM(repetitive peak reverse voltage,VRRM) すべての直流及び繰返し

電圧要素の中で,逆阻止方向へ印加できる最大(ピーク)定格遮断電圧。

3.1.1.6

非繰返しピーク順電流,IFSM(non-repetitive peak forward current,IFSM) 波形及び周波数を規

定した交流で,規定した時間又はサイクル数を流すことができる順方向サージ電流の最大(ピーク)定格

値。

3.1.1.7

繰返しピーク順電流,IFRM(repetitive peak forward current,IFRM) 波形及び周波数を規定した

交流で連続して流すことができる順電流の最大(ピーク)定格値。

3.1.1.8

臨界オン電流上昇率,di/dt,(diT/dt)cr[critical rate of rise of on-state current,di/dt,(diT/dt)cr]

デバイスが破損することなく耐えることのできる電流上昇率の定格値。

3.1.2

主端子に関連する特性(Main terminal characteristics)

3.1.2.1

オフ電圧,VD(off-state voltage,VD) デバイスがオフ状態を維持する直流電圧。

3.1.2.2

オフ電流,ID(off-state current,ID) オフ電圧VDを印加したときの直流電流値。

3.1.2.3

繰返しピークオフ電流,IDRM(repetitive peak off-state current,IDRM) 繰返しピークオフ電圧

VDRMを印加したときのオフ電流の最大(ピーク)値。

3.1.2.4

ブレークオーバ電圧,V(BO)[breakover voltage,V(BO)] 規定した電圧上昇率及び電流上昇率の

条件下で測定する,ブレークダウン領域での主端子間の最大電圧。

備考 ブレークダウン特性における幾つかのV(BO)値に対しては,接尾数字を付け,ブレークダウン電

流領域の関連する部分を規定する。

V(BO)1:0 < I(BR) < 10 mA

3.1.2.5

保持電流,IH(holding current,IH) サイリスタをオン状態に維持できる最小のアノード電流。

アノード電流は,主電流又はサイリスタ電流ともいう。

3.1.2.6

オフ状態静電容量,Co,Cj(off-state capacitance,Co,Cj) 規定した周波数f,振幅Vd,直流バ

イアスVDで測定する,オフ状態における規定した端子間の静電容量。

3.1.2.7

繰返しピーク逆電流,IRRM(repetitive peak reverse current,IRRM) 繰返しピーク逆電圧VRRM

を印加したときの逆方向電流の最大(ピーク)値。

4

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.1.2.8

ピーク順リカバリ電圧,VFRM(peak Forward Recovery Voltage,VFRM) ゼロ又は規定した逆電

圧状態で,規定した電圧上昇率及び電流上昇率を適用したときの主端子間の順電圧の最大値。

3.1.2.9

臨界オフ電圧上昇率,dv/dt,(dvD/dt)cr[critical rate of rise of off-state voltage,dv/dt,(dvD/dt)cr]

オフ状態からオン状態へのスイッチング動作を起こさない(VDRM以下の)最大電圧上昇率。

3.1.3

追加及び派生パラメータ(Additional and derived parameters) 次の派生及び測定パラメータは,

比較,特定用途又は統計的工程管理において使用する。

3.1.3.1

ブレークダウン電圧,V(BR)[breakdown voltage,V(BR)] 規定したブレークダウン電流I(BR)にお

けるブレークダウン領域(点弧ポイント以前)での主端子間の電圧。

備考 正性(正の傾きをもった)ブレークダウンスロープデバイスには,VDRMの代わりにV(BR)を用い

てもよい。

3.1.3.2

ブレークダウン電流,I(BR)[breakdown current,I(BR)] ブレークダウン領域でデバイスに流れ

る電流。

3.1.3.3

ブレークオーバ電流,I(BO)[breakover current,I(BO)] ブレークオーバ電圧V(BO)が発生したと

きに瞬時に流れる電流。

3.1.3.4

スイッチング電圧,VS(switching voltage,VS) ブレークダウン領域でオン状態へスイッチン

グする直前の,主端子間の瞬時の電圧。

3.1.3.5

スイッチング電流,IS(switching current,IS) スイッチング電圧VSで主端子間に流れる瞬時

の電流。

3.1.3.6

オン電圧,VT(on-state voltage,VT) 規定した電流ITでオン状態にあるときの主端子間の電圧。

3.1.3.7

オン電流,IT(on-state current,IT) オン状態条件で主端子間に流れる電流。

3.1.3.8

順電圧,VF(forward voltage,VF) 規定した電流IFで順導通状態にあるときの主端子間の電圧。

3.1.3.9

順電流,IF(forward current,IF) 順導通状態で主端子間に流れる電流。

3.1.3.10 スイッチング抵抗,RS(switching resistance,RS) 次の式で計算するブレークダウン領域での

抵抗RS。

(BO)

S

S

(BO)

I

I

V

V

−

−

3.1.3.11 絶縁抵抗(insulation resistance) 次の式で計算するデバイスの抵抗。

D

D

I

V

3.1.4

温度関連パラメータ(Temperatue related parameters) 半導体TSSのすべてのパラメータは,温

度に依存する。温度依存情報は,意図した動作温度範囲でのパラメータの最大値又は最小値を規定するこ

とによって削除することもできる。共通する幾つかの温度関連用語を次に示す。

3.1.4.1

ブレークダウン電圧の温度係数,αV(BR),dV(BR)/dTj[temperature coefficient of breakdown voltage,

αV(BR),dV(BR)/dTj] 温度変化に対するブレークダウン電圧V(BR)の変化の比。

備考 mV/K又は25 ℃でのブレークダウン電圧を基準とした%/Kで表す。mV/℃又は%/℃で代用で

きる。

3.1.4.2

温度による保持電流変化(variation of holding current with temperature) グラフで示した,温

度変化に伴う保持電流IHの変化。

3.1.4.3

温度軽減(temperature derating) 規定した基準温度を超える場合,ピークインパルス電流など

を軽減すること。百分率で表す。

5

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.1.4.4

熱抵抗,RthJL,RthJC,RthJA(RqJL,RqJC,RqJA)[thermal resistance,RthJL,RthJC,RthJA(RqJL,RqJC,

RqJA)] 熱平衡状態において単位電力を印加したときの,接合部を基準とした周囲,ケース,及びリード

端子部の温度上昇値。

備考 熱抵抗は,K/Wで表す。℃/Wで代用できる。

3.1.4.5

過渡熱インピーダンスZthJL(t),ZthJC(t),ZthJA(t)[ZθJL(t),ZθJC(t),ZθJA(t)]〔transient thermal impedance,

ZthJL(t),ZthJC(t),ZthJA(t)[ZθJL(t),ZθJC(t),ZθJA(t)]〕 熱平衡状態に入る前の熱抵抗に相当するパラメータ。

特定の時間間隔後の仮想接合温度と想定した基準点又は基準領域(周囲,ケース又はリード)との間の温

度差の変化量を,同じ時間間隔で関係する部分の温度差が起きる電力損失の変化量で除した値。

備考1. 温度熱インピーダンスは,K/Wで表す。℃/Wで代用できる。

2. 一般的に過渡熱インピーダンスは,消費電力パルスの継続時間の関数曲線で示す。

3.1.4.6

(仮想)接合温度,TJ,TVJ[(virtual)junction temperature,TJ,TVJ] デバイスの温度及び電

気的挙動の簡易モデルを基礎として計算する接合温度を表す理論上の温度。

備考 用語“仮想接合温度”は特に複数接合半導体に適用し,仕様及び試験方法で必要なときに,半

導体の動作温度を表すために用いる。この規格では,用語“接合温度”TJは,互換性があるよ

うに“仮想接合温度”TVJとして使用する。

3.1.4.7

最大接合温度,TJM(maximum junction temperature,TJM) TSSが自己発熱によって劣化せず

に耐えることのできる接合温度の許容最大値。

3.1.4.8

保存温度範囲,Tstg最小値〜Tstg最大値(storage temperature range,Tstgmin.〜Tstgmax.) 電圧を

印加せずに保存することのできる温度範囲。

備考 推奨温度範囲(IEC 60747-1の6章5.及びIEC 60749の3章1.2から選択)は,次のいずれかに

よる。

0〜125 ℃

−55〜125 ℃

−65〜150 ℃

3.1.5

ゲート端子パラメータ(Gate terminal parameters)

3.1.5.1

ゲート・トリガ電流,IGT(gate trigger current,IGT) デバイスがオフ状態からオン状態に移行

するために必要なゲート電流の最小値。

3.1.5.2

ゲート・トリガ電圧,VGT(gate trigger voltage,VGT) ゲート・トリガ電流IGTを流すために必

要なゲート電圧。

3.1.5.3

ゲート・隣接端子間ピークオフ電圧(gate-to-adjacent terminal peak off-state voltage) オフ電流

IDが既定値を超えない範囲で定格オフ電圧VDを印加できる,ゲート・カソード間最大電圧(Pゲートデバ

イス)又はゲート・アノード間最大電圧(Nゲートデバイス)。

3.1.5.4

ピークオフゲート電流,IGDM(peak off-state gate current,IGDM) ゲート隣接端子間ピークオフ

電圧VGDMを印加したときの最大ゲート電流。

3.1.5.5

隣接端子開放時のゲート逆電流,IGAO,IGKO(gate reverse current, adjacent terminal open,IGAO,

IGKO) 規定したゲートバイアス電圧VGを印加したときにゲート端子に流れる電流。

なお,Pゲートのカソード端子又はNゲートのアノード端子はオープン回路とする。

3.1.5.6

主端子短絡時のゲート逆電流,IGAS,IGKS(gate reverse current, main terminals short circuited,

IGAS,IGKS) 規定したゲートバイアス電圧VGを印加したときにゲート端子に流れる電流。

なお,Pゲートのカソード端子又はNゲートのアノード端子は短絡する。

6

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

備考 この定義は,直列ゲート阻止ダイオードを内蔵したデバイスだけに適用する。

3.1.5.7

オン状態のゲート逆電流,IGAT,IGKT(gate reverse current,on-state,IGAT,IGKT) 規定したゲ

ートバイアス電圧VGを印加し,規定したオン電流ITを流したときのゲート端子に流れる電流。

備考 この定義は,直列ゲート阻止ダイオードを内蔵したデバイスだけに適用する。

3.1.5.8

順導通状態のゲート逆電流,IGAF,IGKF(gate reverse current,forward conducting state,IGAF, IGKF)

規定したゲートバイアス電圧VGを印加し,規定した導通電流IFを流したときのゲート端子に流れる電流。

備考 この定義は,直列ゲート阻止ダイオードを内蔵したデバイスだけに適用する。

3.1.5.9

ゲートスイッチング電荷,QGS(gate switching charge,QGS) インパルス条件下で,規定した

ゲートバイアス電圧VGを印加したとき,オフ状態からスイッチングポイントに移行する間にゲート端子を

流れる電荷。

3.1.5.10 ピークゲートスイッチング電流,IGSM(peak gate switching current,IGSM) 規定したゲートバ

イアス電圧VGを印加したとき,オフ状態からスイッチングポイントに移行する間にゲート端子を流れる電

流の最大値。

3.1.5.11 ゲート・隣接端子間ブレークオーバ電圧,VGK(BO),VGA(BO)[gate-to-adjacent terminal breakover

voltage,VGK(BO),VGA(BO)] ブレークオーバポイントでのP形TSSのゲート・カソード間電圧又はN形

TSSのゲート・アノード間電圧。

備考 これはブレークオーバ電圧V(BO)と規定したゲート電圧VGの差に等しい。

3.2

TSS,端子及び特性の用語並びに定義

3.2.1

TSS

3.2.1.1

非対称双方向TSS(asymmetrical bidirectional TSS) 主端子間電圧電流特性の第一象限と第三

象限とで大きく異なるスイッチング動作を示すTSS。

3.2.1.2

双方向TSS(bidirectional TSS) 主端子間電圧電流特性の第一象限及び第三象限でスイッチン

グ動作を示すTSS。

3.2.1.3

順阻止TSS(forward-blocking TSS) 主端子2(カソード)へ負の電圧を印加したときだけスイ

ッチング動作し,主端子2へ正の電圧を印加したときは阻止状態のTSS。

3.2.1.4

順導通TSS(forward-conducting TSS) 主端子2(カソード)へ負の電圧を印加したときだけス

イッチング動作し,主端子2へ正の電圧を印加したときにはオン状態のように大電流を導通するTSS。

3.2.1.5

負性ブレークダウン抵抗TSS(negative-breakdown resistance TSS) 静的ブレークダウン特性に

おいてスイッチングに先立ち負性(負の傾きをもった)抵抗曲線をもつTSS。

3.2.1.6

N-ゲートサイリスタ(N-gate thyristor) ゲート端子をアノードP領域に隣接するN領域に接続

したゲート付サイリスタ。通常は,ゲート・アノード間に印加する負信号によって,オン状態にスイッチ

する。

3.2.1.7

P-ゲートサイリスタ(P-gate thyristor) ゲート端子をカソードN領域に隣接するP領域に接続

したゲート付サイリスタ。通常は,ゲート・カソード間に印加する正信号によって,通常はオン状態にス

イッチする。

3.2.1.8

正性ブレークダウン抵抗TSS(positive-breakdown N-resistance TSS) 静的ブレークダウン特性

においてスイッチングに先立ち正性(正の傾きをもった)抵抗スロープをもつTSS。

3.2.1.9

逆阻止TSS(reverse-blocking TSS) カソードへ正の電圧を印加したとき阻止状態のTSS。

3.2.1.10 逆導通TSS(reverse-conducting TSS) カソードへ正の電圧を印加したとき導通状態のTSS。

7

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.2.1.11 対称形双方向TSS(symmetrical bidirectional TSS) 主端子間電圧電流特性の第一象限と第三象

限とで,ほぼ同じスイッチング特性をもつTSS。

3.2.1.12 サイリスタ(thyristor) 主端子間電圧電流特性の少なくとも一つの象限で,オフ状態からオン

状態,又はオフ状態からオン状態へスイッチング動作できる三つ以上の接合からなる双安定半導体デバイ

ス。

3.2.1.13 片方向TSS(unidirectional TSS) 主端子間電圧電流特性の一つの象限だけで,スイッチング特

性をもつTSS。

3.2.2

端子(Terminals)

3.2.2.1

アノード(anode) サイリスタが,ゲート開放回路でオン状態にあるとき,電流がサイリスタ

に入る電極(IEC 60747-6参照)。

備考 この用語は,双方向サイリスタには適用しない。

3.2.2.2

カソード(cathode) サイリスタが,ゲート開放回路でオン状態にあるとき,電流がサイリスタ

から出る電極。

備考 この用語は,双方向サイリスタには適用しない。

3.2.2.3

ゲート(gate) 制御電流を流すために半導体領域の一部に接続する電極。

3.2.2.4

主端子(main terminals) 主電流が流れる二つの端子。

備考 主端子は,使用用途によって名前を付けてもよい。例えば,通信ではR(リング),T(チップ),

G(接地)又はA,B,C(コモン)。

3.2.2.5

主端子1(main terminal 1) 製造業者が1と命名した主端子。

3.2.2.6

主端子2(main terminal 2) 製造業者が2と命名した主端子。

3.2.2.7

電気的端子[(electrical)terminal] 外部から利用できる接続ポイント。

3.2.3

特性用語(Characteristic terminology)

3.2.3.1

阻止(blocking) 通過電流に対し高抵抗となる半導体デバイスの状態又は半導体接合の状態。

3.2.3.2

ブレークダウン(breakdown) 逆電流の増加によって動的高抵抗領域から動的低抵抗領域へ移

行する,逆バイアスした半導体接合で起こる初期の現象。

3.2.3.3

ブレークダウン領域(breakdown region) 動的高抵抗オフ状態から動的低抵抗に移行し始め,

スイッチングポイントに到達するまでの特性の範囲。

3.2.3.4

ブレークオーバポイント(breakover point) 電圧電流特性の微分抵抗がゼロで,主電圧が最大

値に到達するブレークダウン領域のポイント(IEC 60747-6の2.16を修正)。

備考 ブレークダウン領域にブレークオーバポイントが一つ以上あるときは,最高電圧値のポイント

で示す。

3.2.3.5

特性(characteristic) デバイス固有の測定できる性質。

備考 この性質は,電気的,機械的,熱的,水理的,電磁気的又は原子核的で,認識できるある状態

に対する数値として表記できる。特性は,一連の関係する値の組合せで表記してもよく,通常

グラフ形式で表す。

3.2.3.6

クリッピング(クランピング)[clipping(clamping)] 事前に設定したしきい値を超える信号

が,しきい値又は保持した信号の全瞬時値付近まで減少する制限形式(IEV 702-04-33)。

備考 用語クランピングは,しばしばクリッピングの代わりに用いられる。IEV 702-04-37ではクラン

ピングを“例えば,直流電流では,回帰信号の幾つかの特徴で基準値を作る過程”と定義して

いる。

8

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.2.3.7

クローバ(crowbarring) 信号の瞬時値が事前に設定したしきい値を超えるとき,低インピーダ

ンス短絡として動作する制限形式。動作時は,短絡によって信号源インピーダンスとともに信号振幅が減

少する。

3.2.3.8

順・逆阻止象限(forward/reverse blocking quadrant) デバイスが順・逆阻止状態を示す主端子

間電圧電流特性の象限(IEC 60747-6を修正)。

備考 順阻止TSSでは第一象限,逆阻止TSSでは第三象限である。

3.2.3.9

順・逆導通象限(forward/reverse conducting quadrant) デバイスが順・逆導通状態を示す主端

子間電圧電流特性の象限(IEC 60747-6を修正)。

備考 この状態は,順導通の第一象限及び逆導通の第三象限である。

3.2.3.10 順方向(forward direction)

1) P形半導体領域がN形半導体領域に対して正電位にある場合に,PN接合を流れる電流の方向。

2) ある端子に接続したP形半導体領域が他の端子に接続したN形領域に対して正電位にある場合に,

半導体デバイスを流れる電流の方向。

備考 この定義は,一つ以上の接合が直列に接続しており,そのうち少なくとも一つのPN領域が逆

になっている場合には適用しない。

3.2.3.11 最大定格(絶対最大定格)[maximum rating(absolute maximum rating)] デバイスに損傷を起

こす寸前の限界能力又は限界条件の定格。

備考 限界条件には,最大又は最小がある。

3.2.3.12 負性微分抵抗(領域)[negative differential-resistance(region)] 微分抵抗が負性で(負の傾き

をもち),サイリスタがブレークダウンとオン状態領域との間でスイッチする,スイッチング象限の主端子

間電圧電流特性の領域(IEC 60747-6を修正)。

3.2.3.13 非繰返し電流定格(non-repetitive current rating) デバイスに100回以上流しても故障しない非

繰返し電流の最大定格。

備考 この定格状態の間は,デバイスは短時間であれば最大定格接合温度を超えてもよい。定格状態

の間又はその直後から,デバイスが最初の熱平衡状態に復帰するまで阻止電圧又はいかなるゲ

ート制御に関する要求はない。この定格条件は,デバイスが最初の熱平衡状態に復帰した後に

繰り返してもよい。

3.2.3.14 オフ状態(領域)[off state(region)] スイッチング象限の初期からブレークダウン領域の始ま

りまでの特性で,動的高抵抗部に相当するTSSの状態(IEC 60747-6を修正)。

3.2.3.15 オン状態(領域)[on state(region)] スイッチング象限の主端子間電圧電流特性の低抵抗及び

低電圧部に相当するTSSの状態。

3.2.3.16 パラメータ(parameter) 特性,定格などのように,測定又は定量化できるデバイスについて

の記述。

3.2.3.17 主電流(principal current) ゲート電流以外のデバイスを流れる電流の一般的表現。

備考 両主端子間を流れる電流である。

3.2.3.18 主電圧(principal voltage) 主端子間の電圧。

備考1. 逆阻止及び逆導通サイリスタの場合,アノード電位がカソード電位よりも高いとき,主電圧

は正と呼び,アノード電位がカソード電位より低いときは負と呼ぶ。

2. 双方向サイリスタの場合,主端子2の電位が主端子1の電位より高いとき,主電圧は正と呼

ぶ。

9

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3. 順導通サイリスタの場合,カソード電位がアノード電位より高いとき,主電圧は正と呼び,

カソード電位がアノード電位より低いとき,主電圧は負と呼ぶ。

3.2.3.19 主端子間電圧電流特性(主特性)[principal voltage -current characteristics (principal

characteristic)] 通常,グラフで表す主電流と主電圧との関係。

3.2.3.20 象限(quadrant) 主端子間電圧電流特性をグラフに表すとき,電圧v軸及び電流i軸で形成さ

れる四領域。これらの領域は,反時計回りに第一,第二,第三及び第四象限という。特性は,第一象限で

+v及び+i並びに第三象限で−v及び−iとなる。

3.2.3.21 定格(rating) 部品,機械,装置,電子デバイスなどが満足なサービスを提供することができ

るように使用条件を規定するための,電気的,熱的,機械的又は環境的な値の公称値。

備考 定格は,一般用語である。3.2.3.11の最大定格を参照。

3.2.3.22 繰返し定格(repetitive rating) TSSに連続的に印加できる最大定格。

3.2.3.23 逆方向(reverse direction)

1) N形半導体領域がP形半導体領域に対して正電位にある場合に,PN接合を流れる電流の方向。

2) 端子に接続したN形半導体領域が他の端子に接続したP形半導体領域に対して正電位にある場合に,

半導体デバイスを流れる電流の方向。

備考 この定義は,一つ以上の接合が直列に接続しており,そのうち少なくとも一つのPN領域が逆

になっている場合は適用しなくてもよい。

3.2.3.24 スイッチングポイント(switching point) TSSの回生及びオン状態へスイッチング動作する主

端子間電圧電流特性上のポイント。

備考 このポイントは,ブレークダウン領域の終点及び負性微分抵抗領域の始点で起こる。

3.2.3.25 スイッチング象限(switching quadrant) デバイスがオフ状態とオン状態との間をスイッチング

動作するように意図した主端子間電圧電流特性の象限。

備考 双方向サイリスタの場合,スイッチング象限は第一象限及び第三象限である。逆阻止又は逆導

通サイリスタの場合,スイッチング象限は第一象限である。順導通又は順阻止サイリスタの場

合,スイッチング象限は第三象限である。

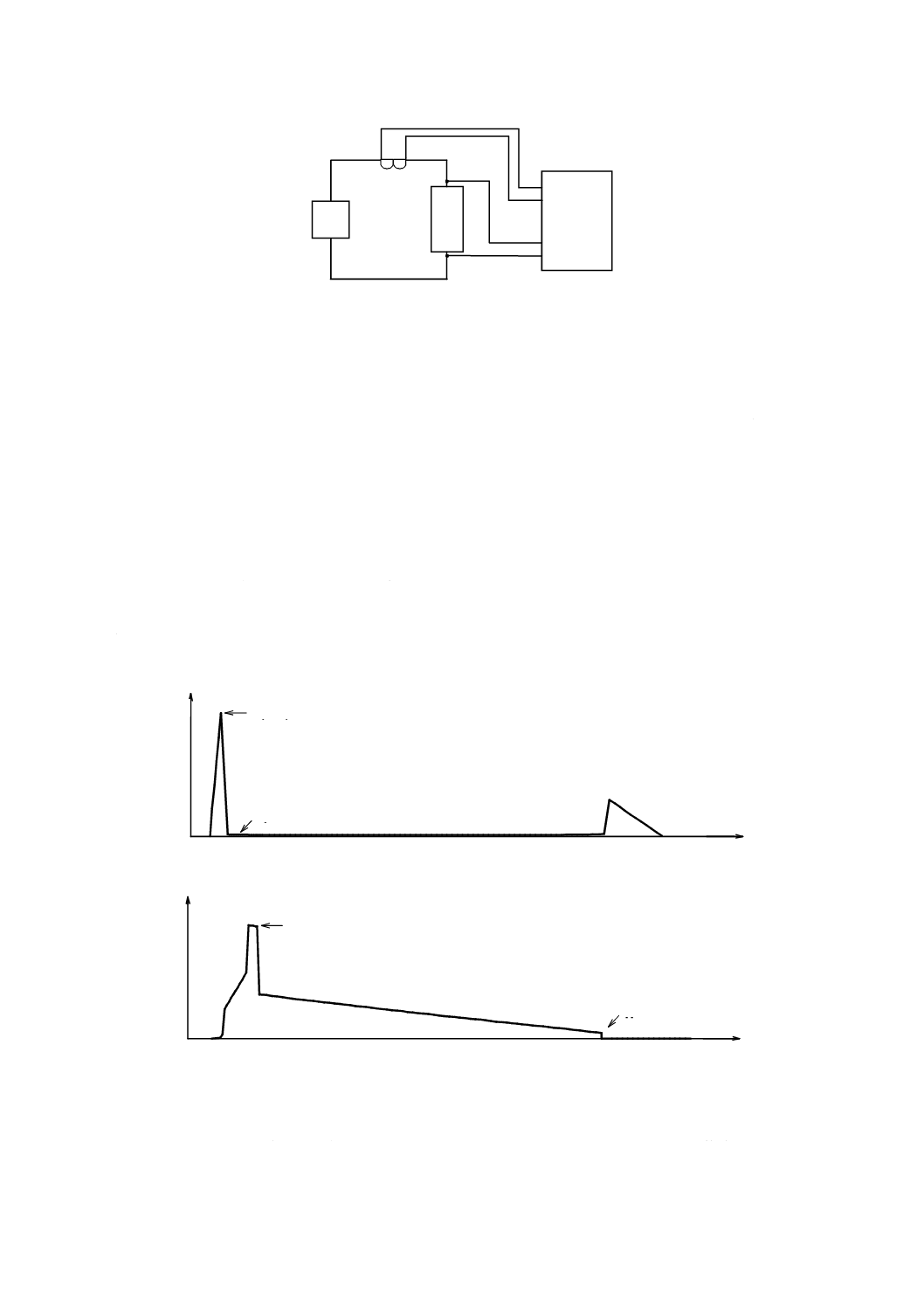

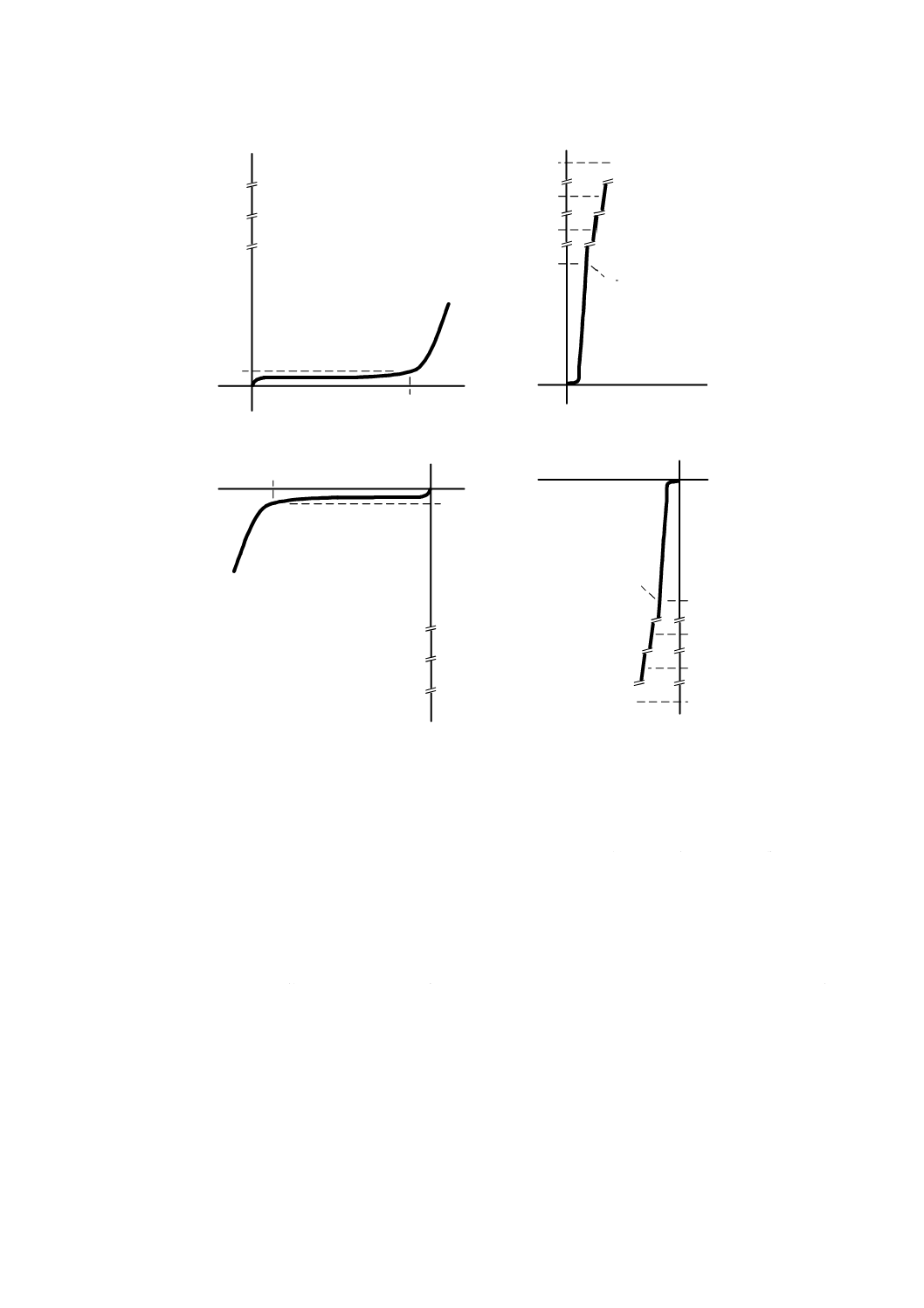

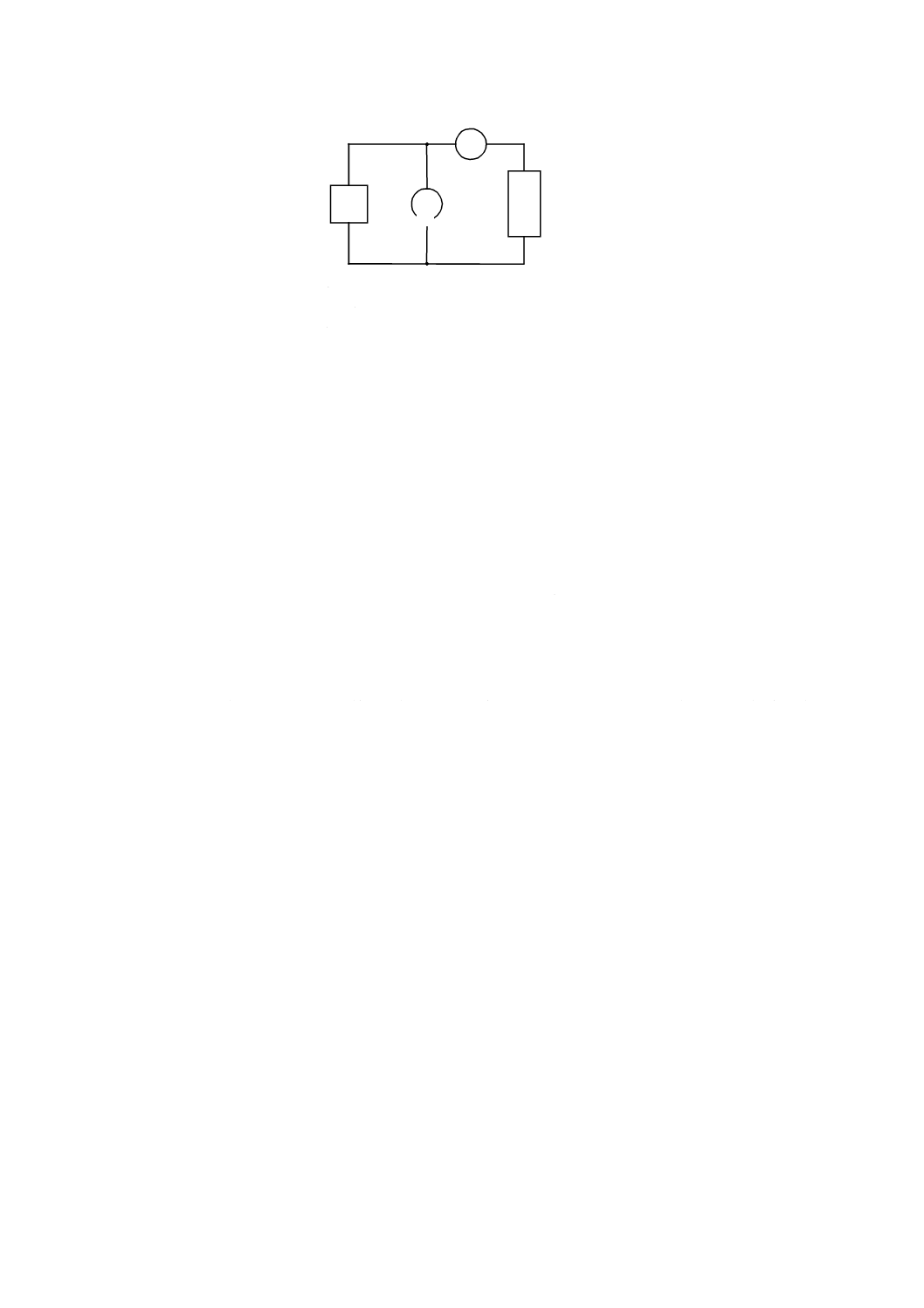

4. 基本機能及び部品説明 この項は,TSSの種類,基本デバイス構造,等価回路,特性値,使用パラメ

ータ及び付加機能の構造を扱う。

4.1

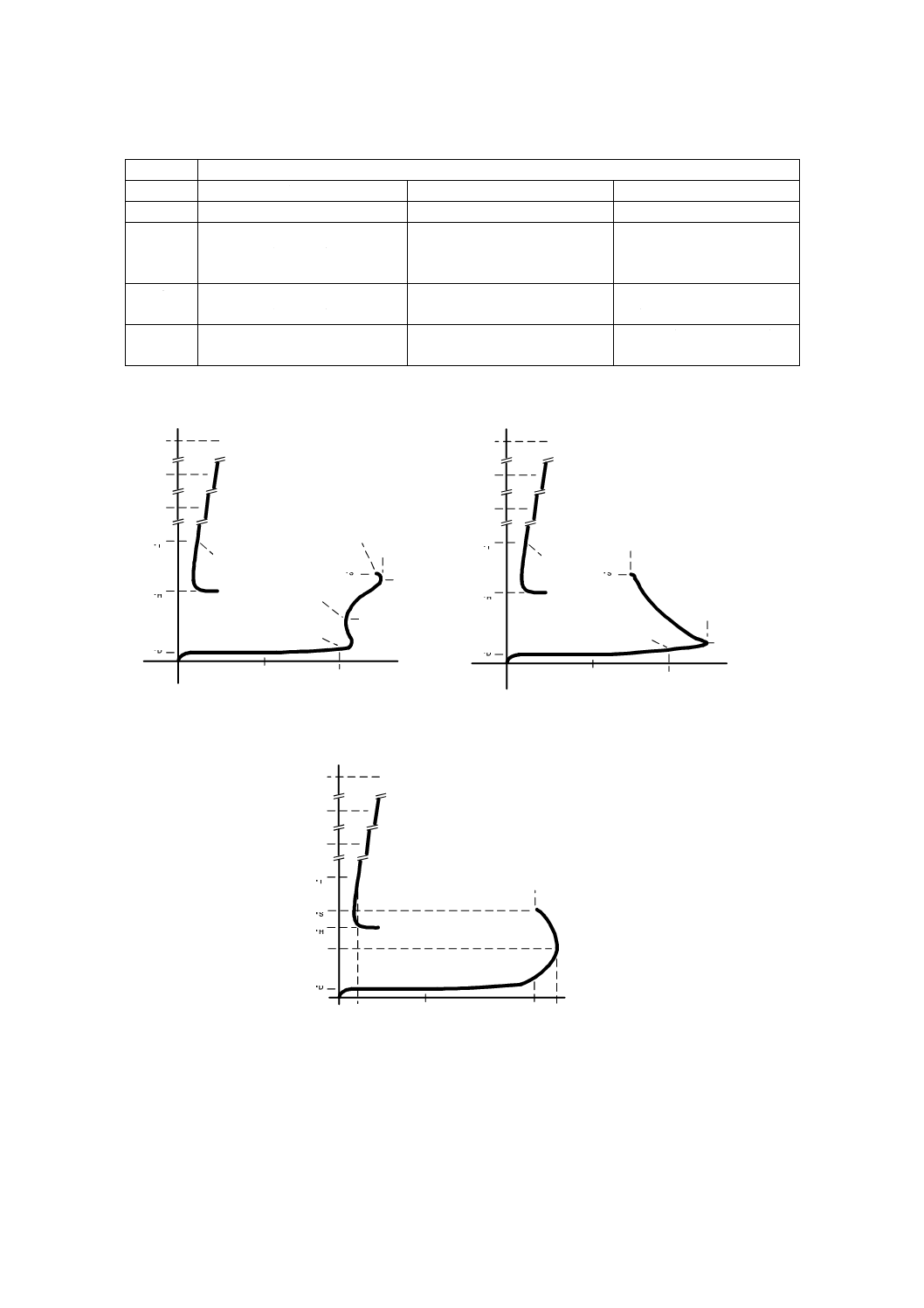

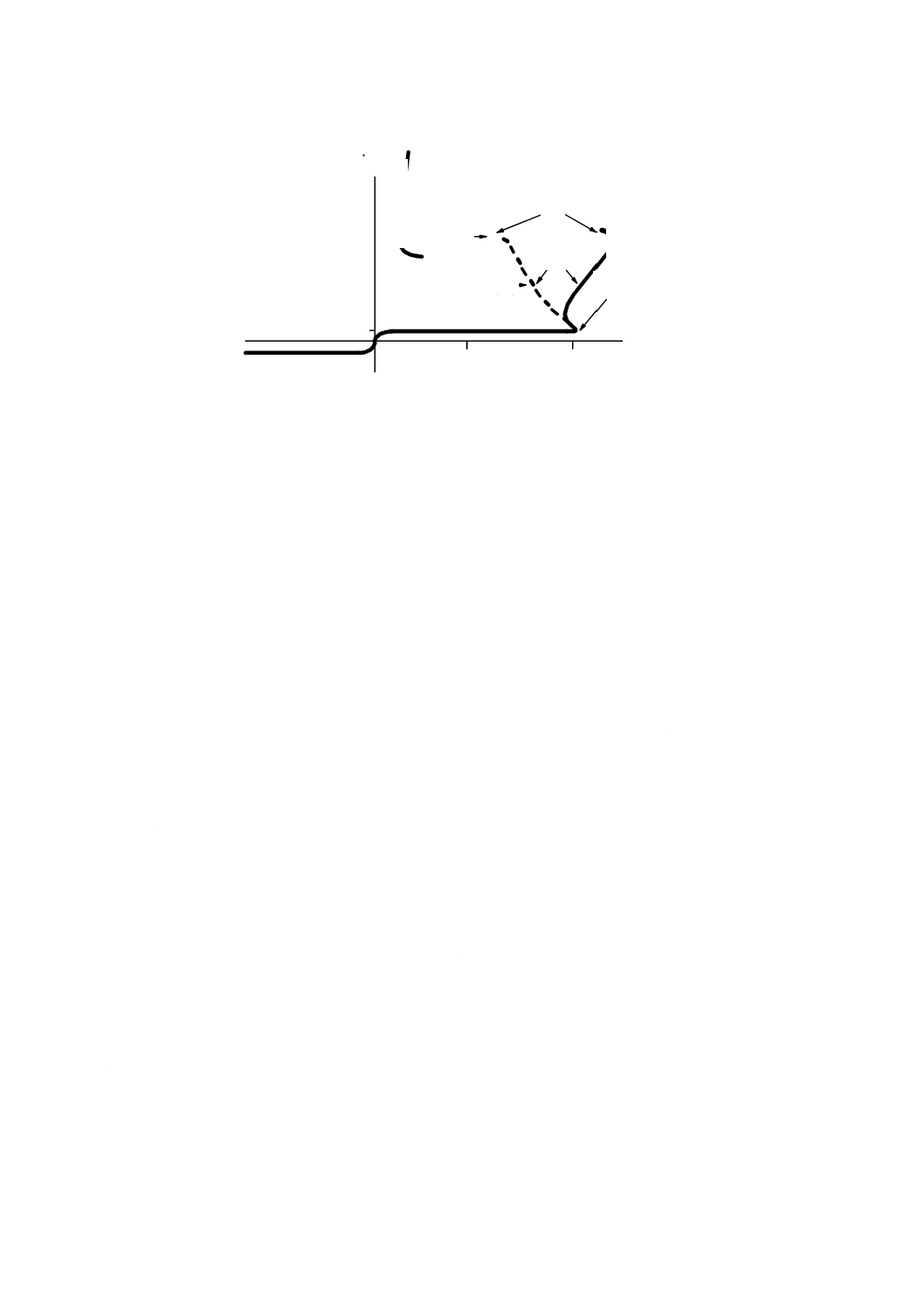

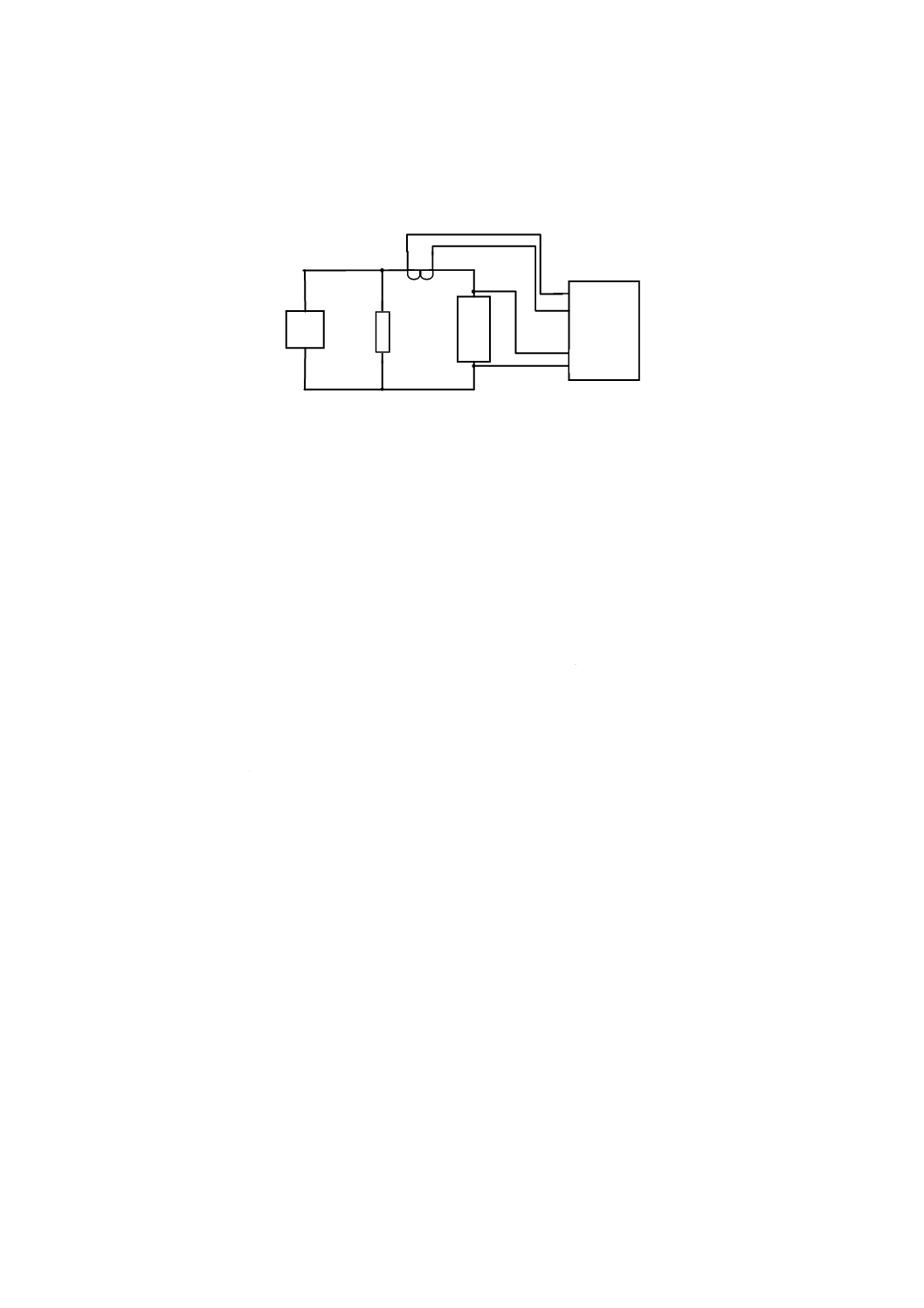

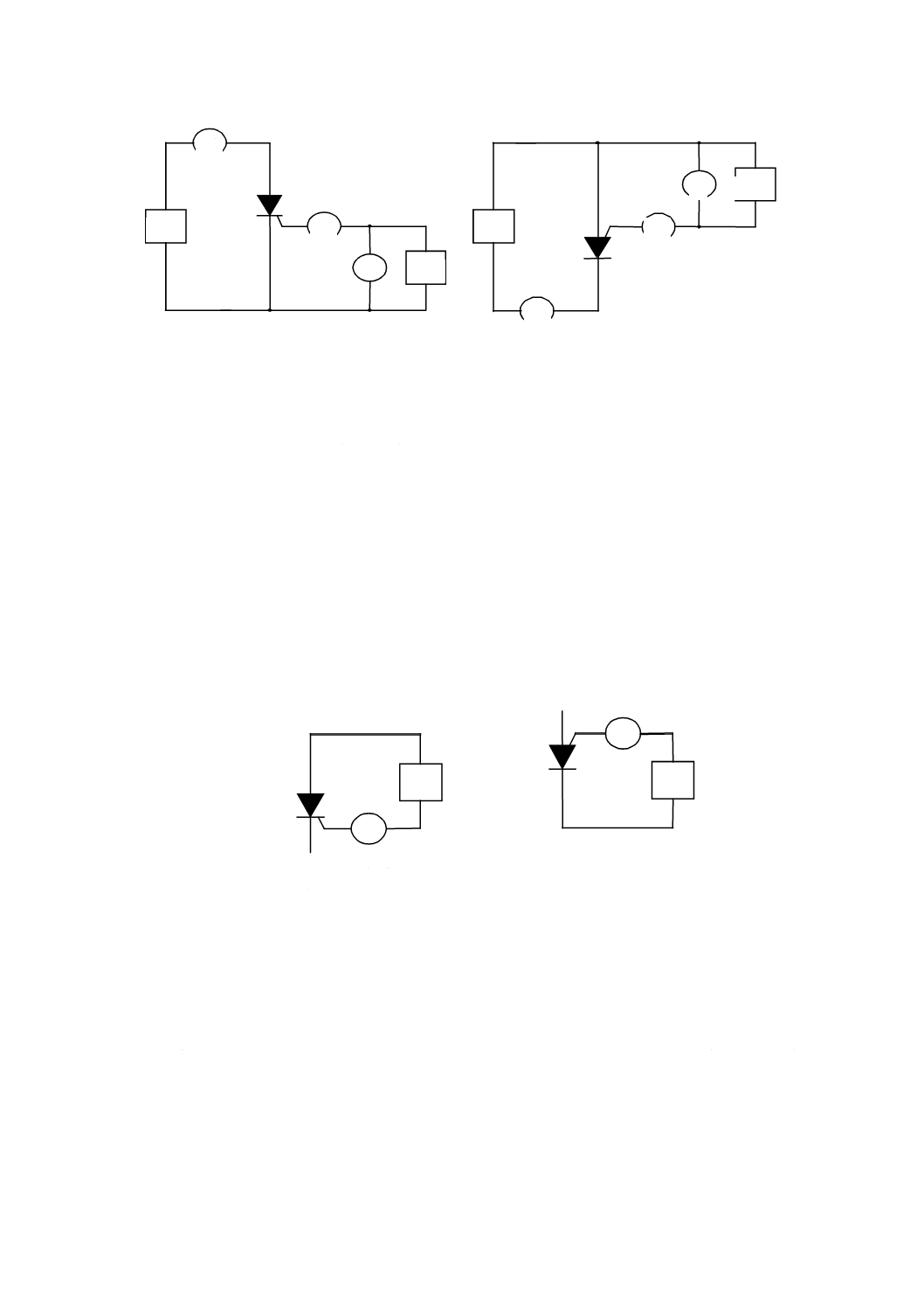

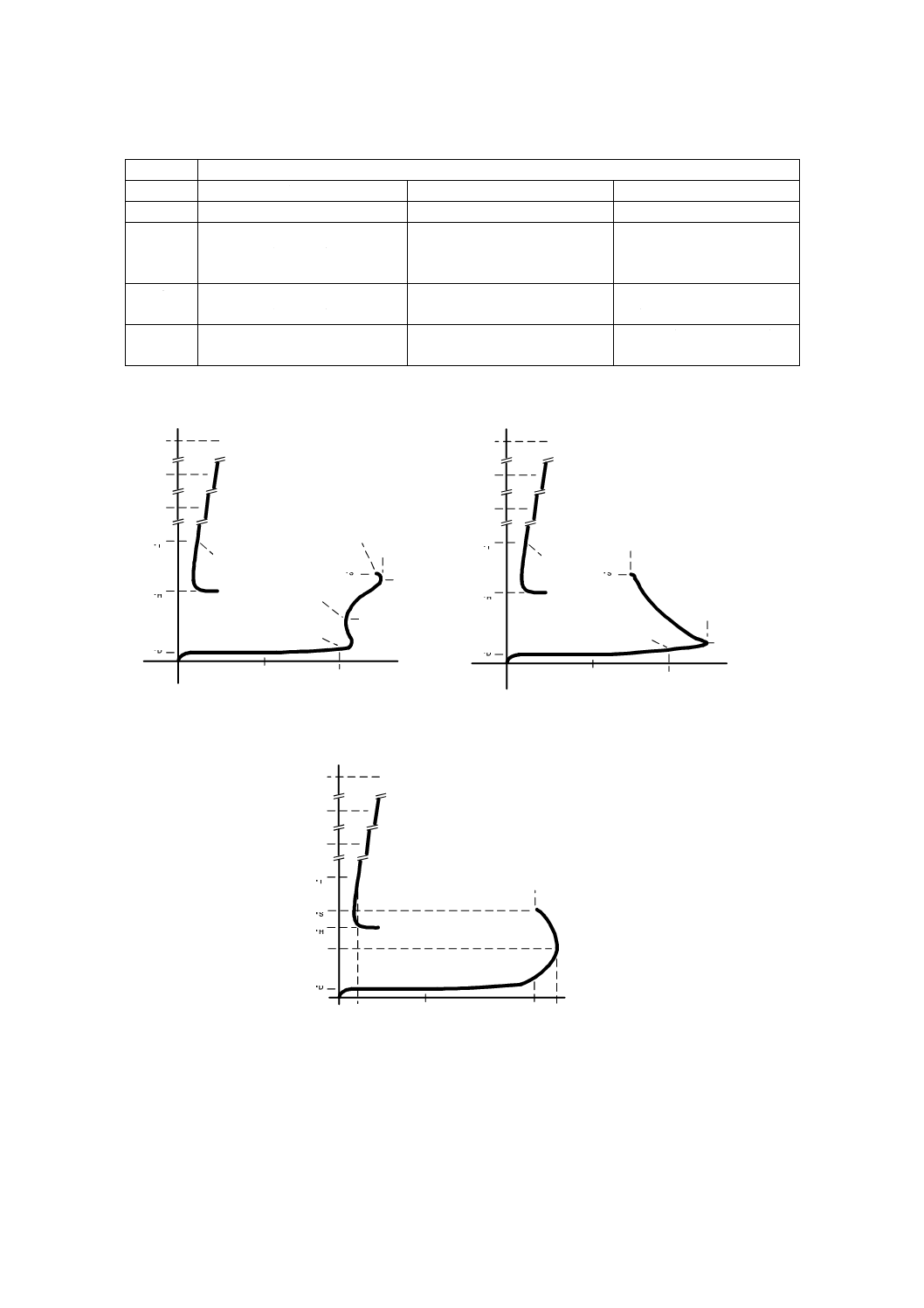

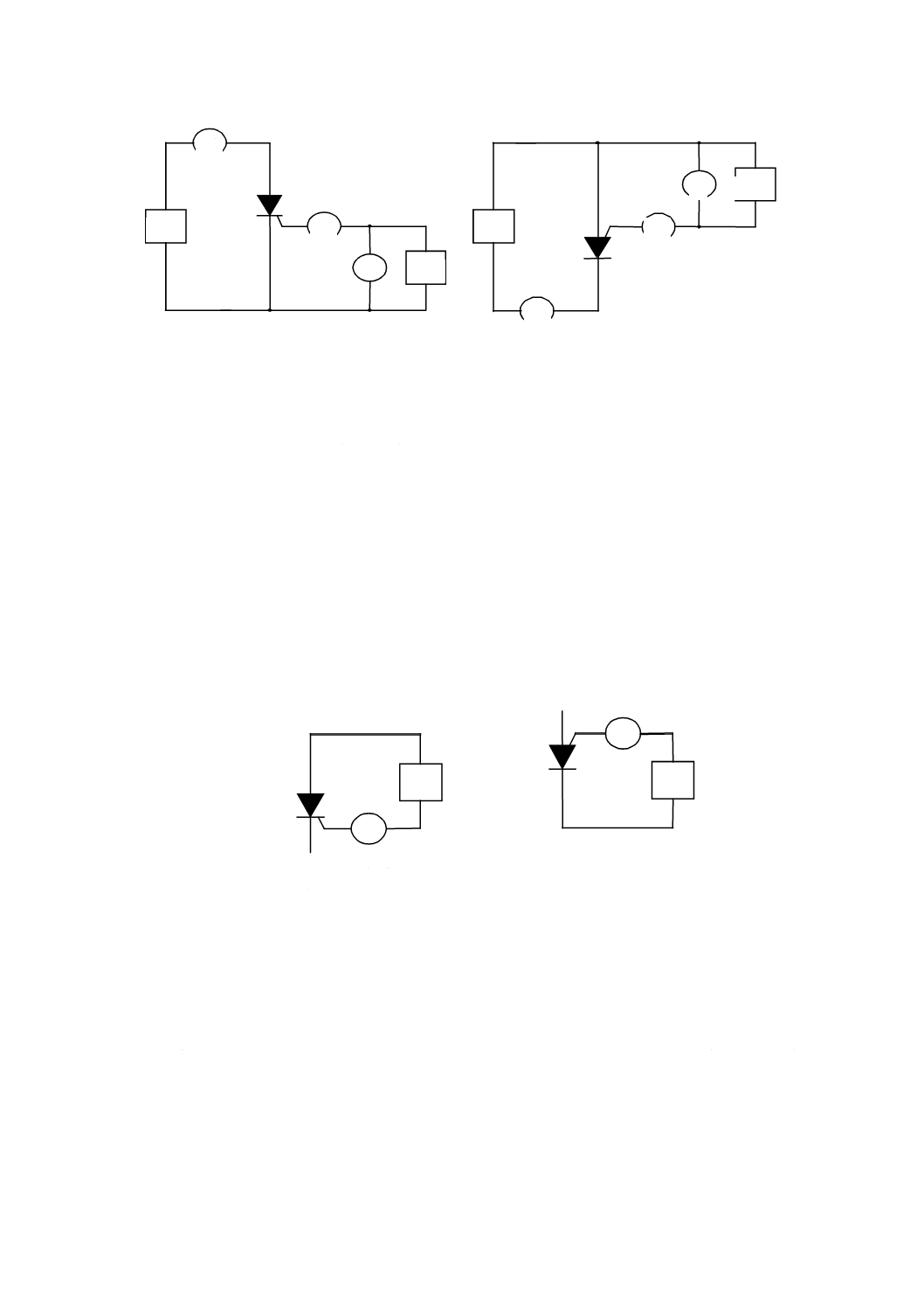

TSSの種類 TSSは,第一象限及び第三象限における特性並びに端子数によって分類できる。TSS

は,少なくとも一つの象限においてスイッチング特性を示す(図1参照)。他の象限ではスイッチング,阻

止又はダイオード導通特性を示してもよい(図1及び図2参照)。スイッチング象限が一つだけのデバイス

は,片方向と呼び,2端子,3端子,又は4端子のいずれでもよい。さらに,スイッチング象限が二つのデ

バイスは,双方向と呼び,5端子以下の端子をもっていてもよい(表1参照)。

10

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

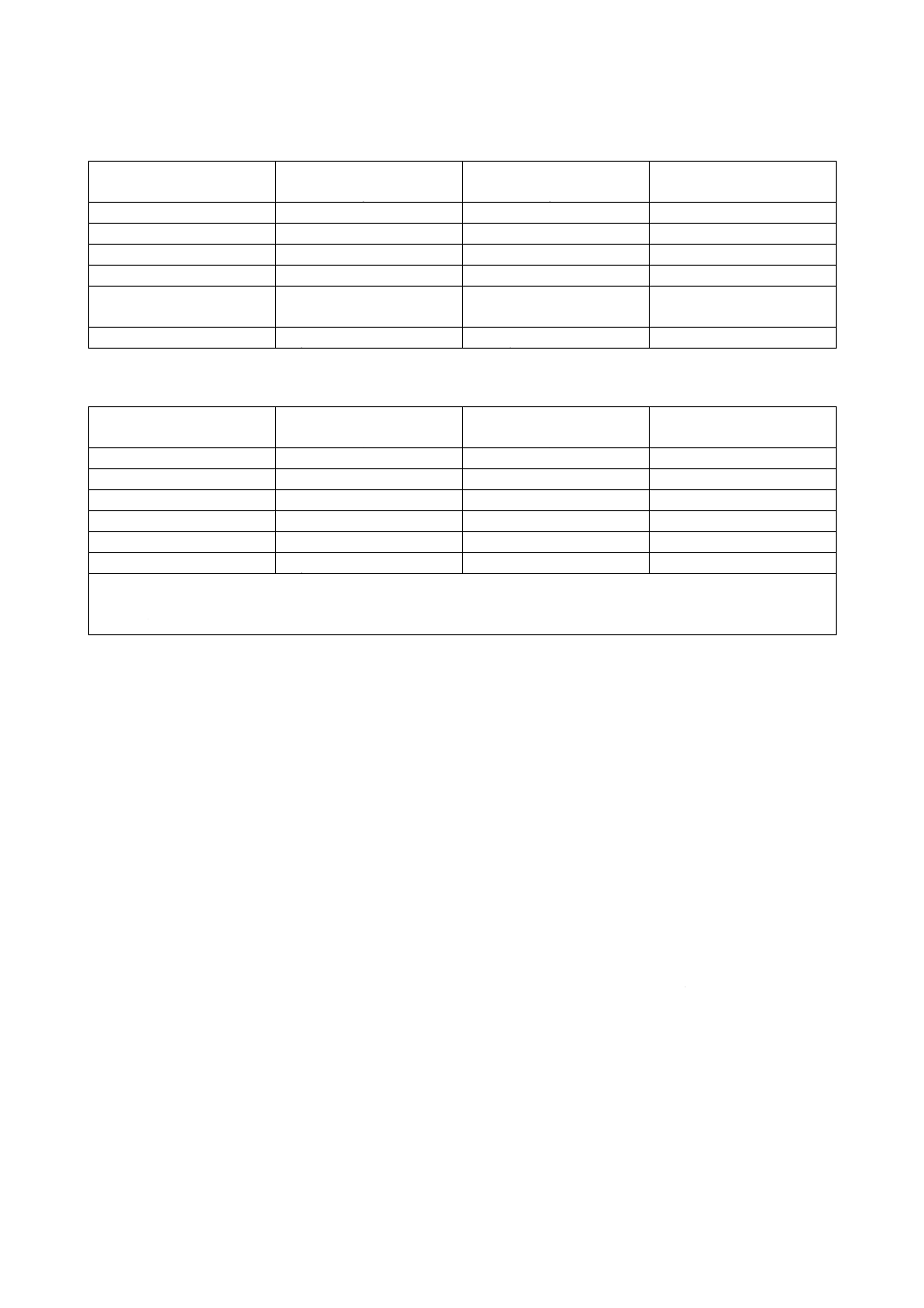

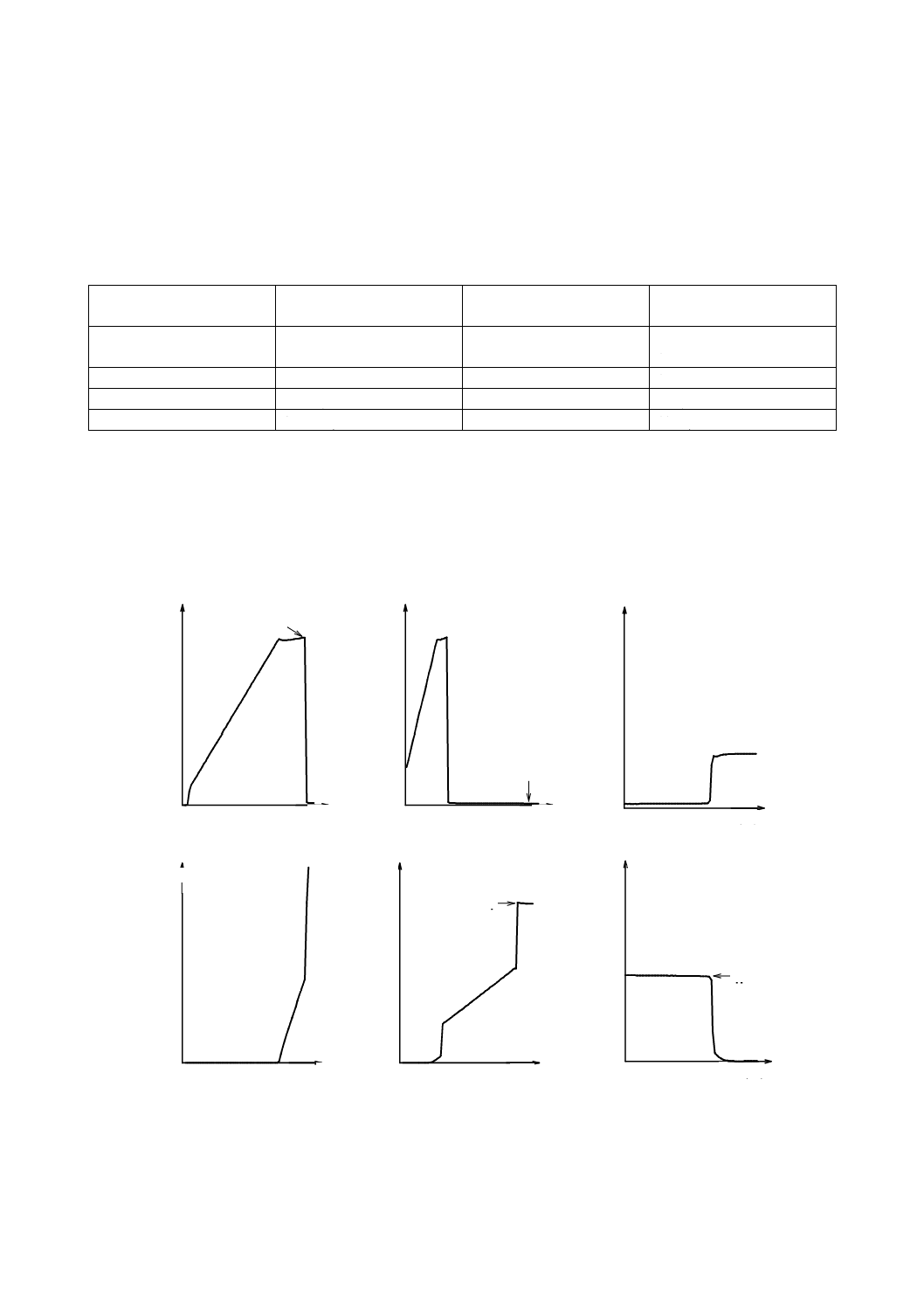

表 1 TSSの種類

端子数

他の象限における特性

阻止

導通

スイッチング

2

逆阻止又は順阻止2端子TSS

逆導通又は順導通2端子TSS

双方向2端子TSS

3

Pゲート又はNゲートをもつ逆

阻止又は順阻止3端子TSS

Pゲート又はNゲートをもつ

逆導通又は順導通3端子TSS

Pゲート,Nゲート又はPN

結合ゲートをもつ双方向3

端子TSS(トライアック)

4

Pゲート及びNゲートをもつ逆

阻止又は順阻止4端子TSS

Pゲート及びNゲートをもつ

逆導通又は順導通4端子TSS

二つのゲートをもつ双方向

4端子TSS

5

三つのゲートをもつ双方向

5端子TSS

ゲート制御クリッピング電圧

+v

+i

(BO)

I

SI

TI

DI

HI

PPSM

I

V(BO)

VS

VT

VD

TSM

I

TRM

I

VG

+v

+i

TI

DI

HI

PPSM

I

VT

VD

TSM

I

DRM

V

IDRM

TRM

I

SI

VS

(BO)

I

V(BO)

スイッチング特性

正性ブレークダウンスロープ

+v

+i

(BO)

I

(BR)

I

SI

TI

DI

HI

PPSM

I

V(BO)

V(BR)

VS

VT

VD

TSM

I

DRM

V

IDRM

TRM

I

スイッチング特性

負性ブレークダウンスロープ

スイッチング特性

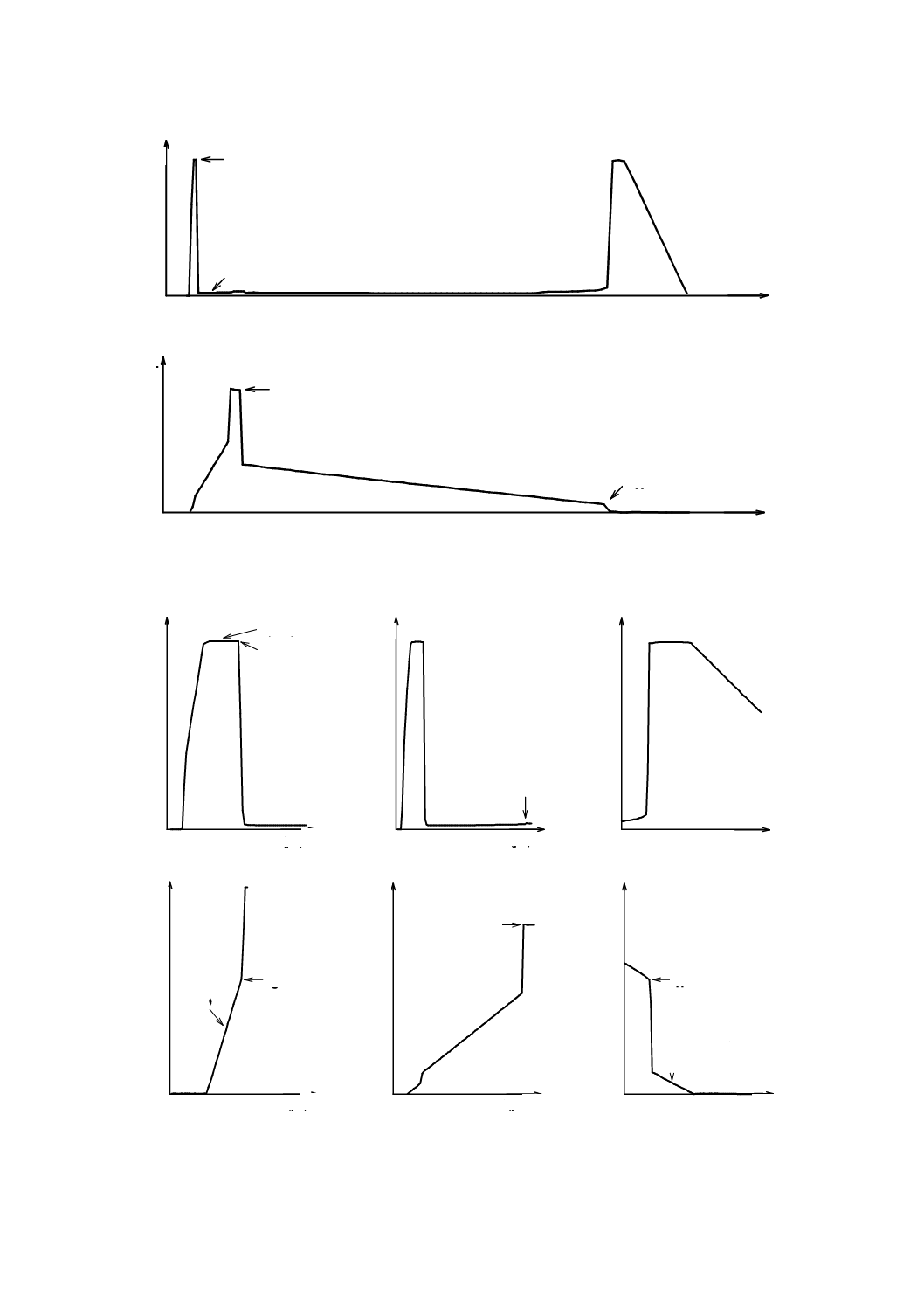

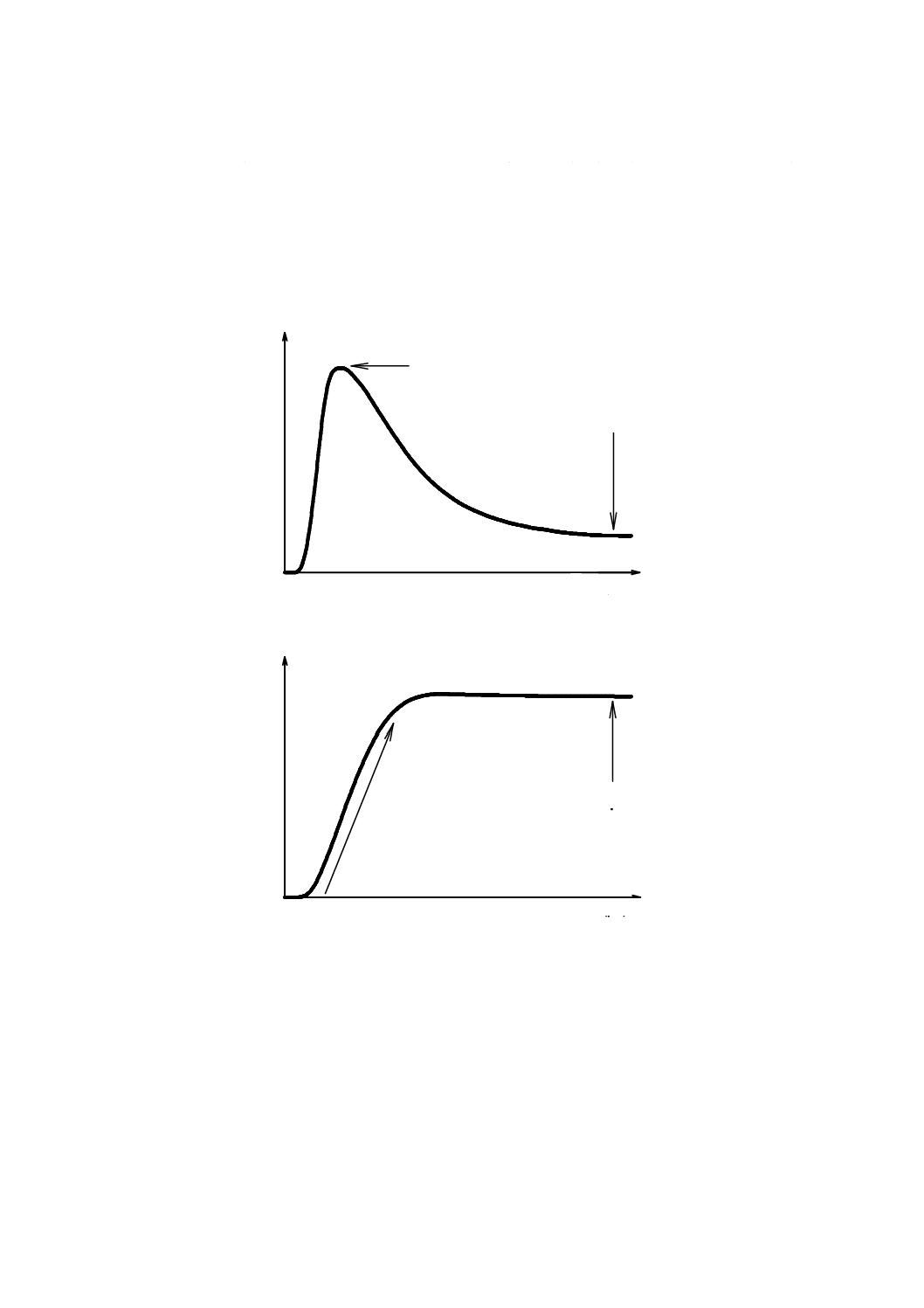

図 1 スイッチング特性

11

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

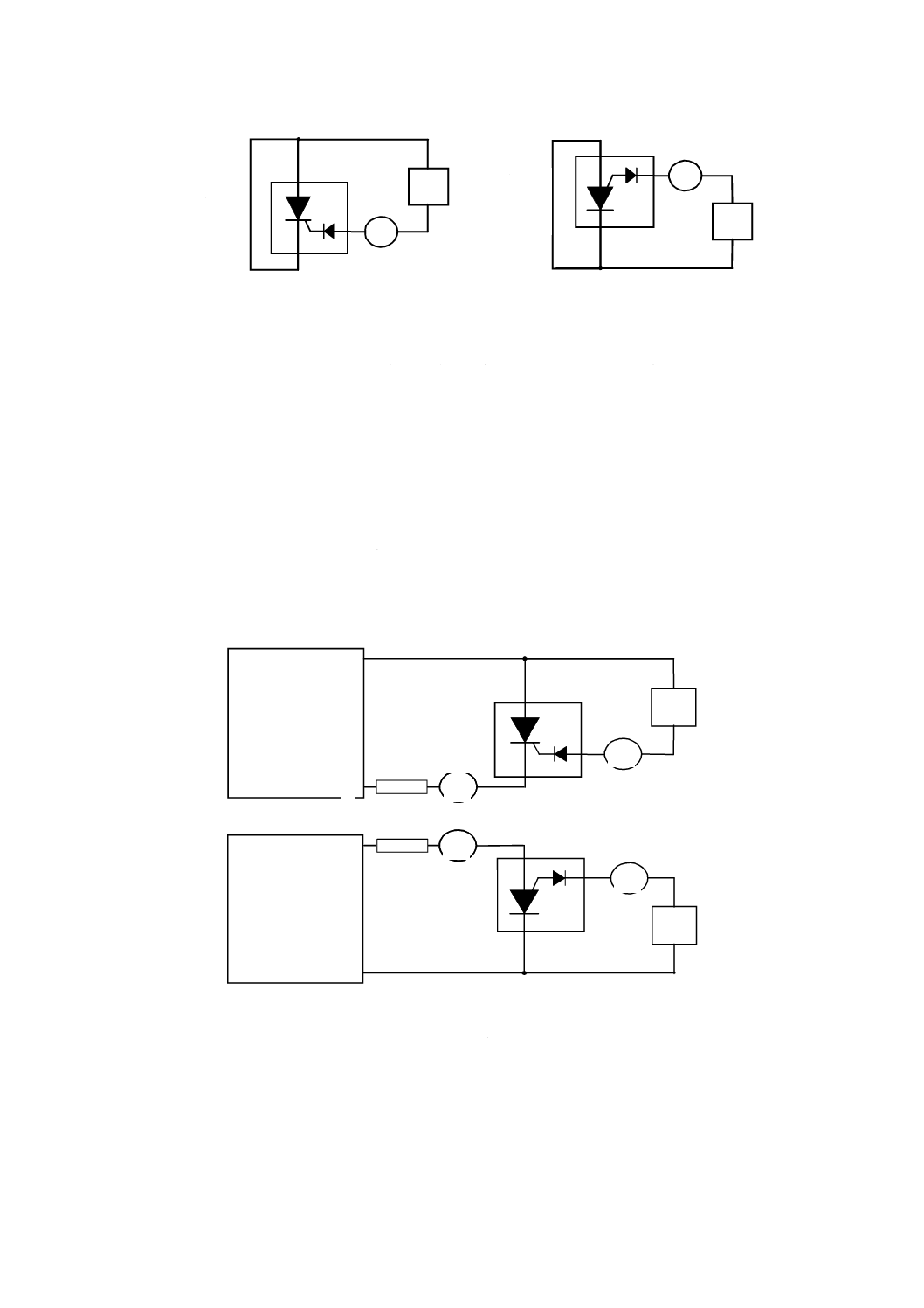

順導通特性

+v

+i

PPSM

I

F

V

IF

FSM

I

FRM

I

+v

+i

順阻止特性

RRM

V

IRRM

逆導通特性

-v

-i

PPSM

I

F

V

IF

FSM

I

FRM

I

-v

-i

逆阻止特性

RRM

V

IRRM

図 2. 非スイッチング特性

図 2 非スイッチング特性

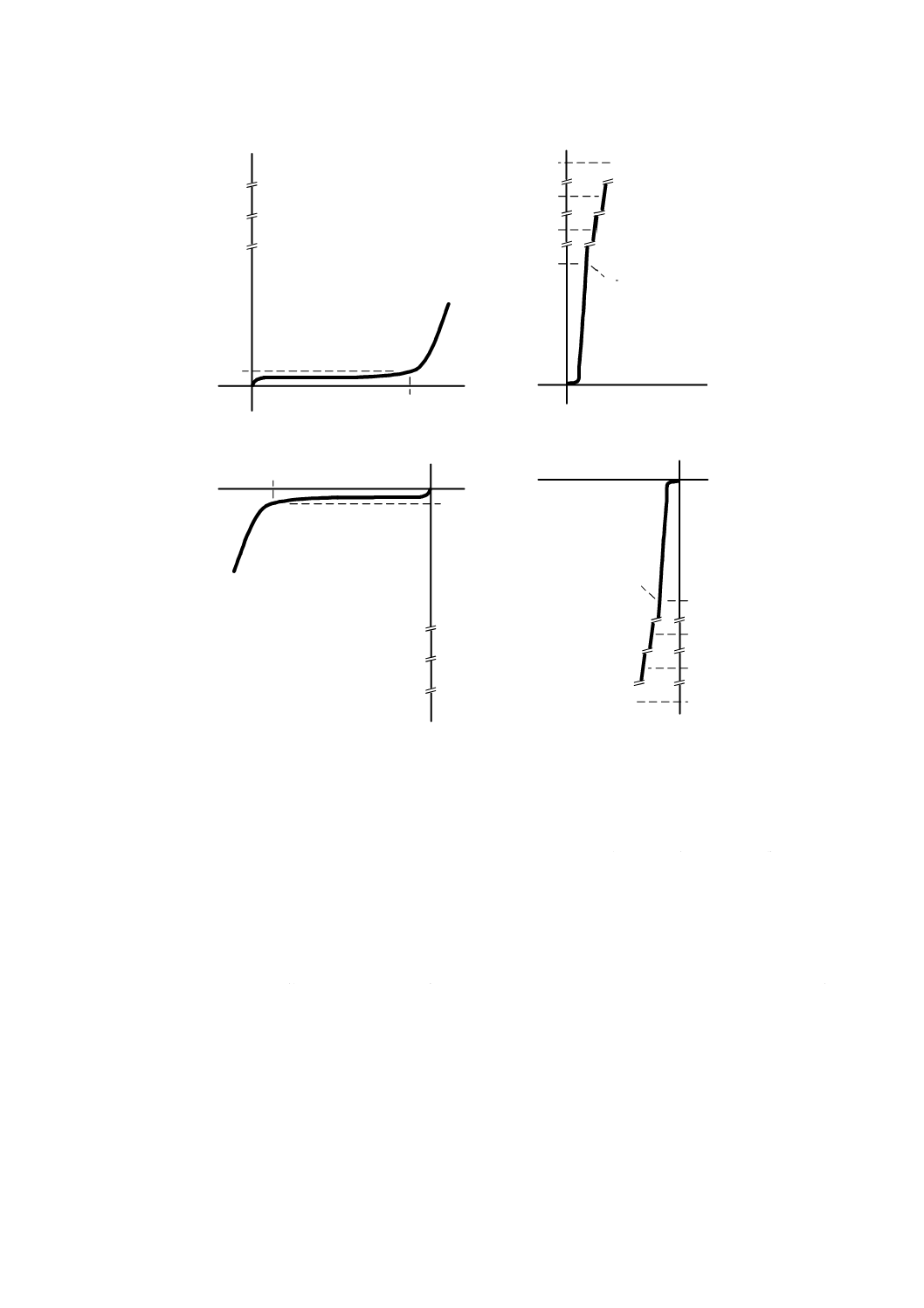

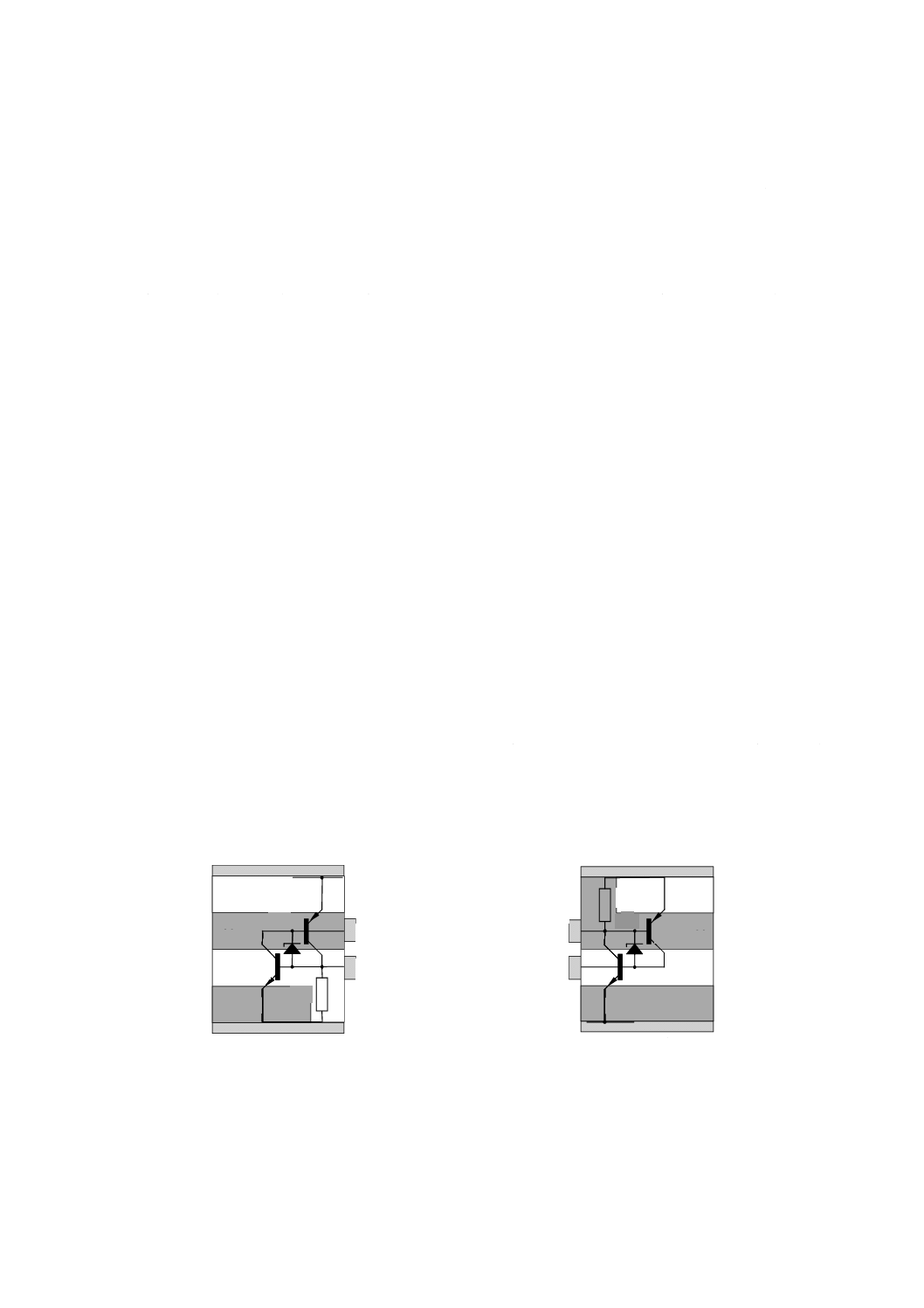

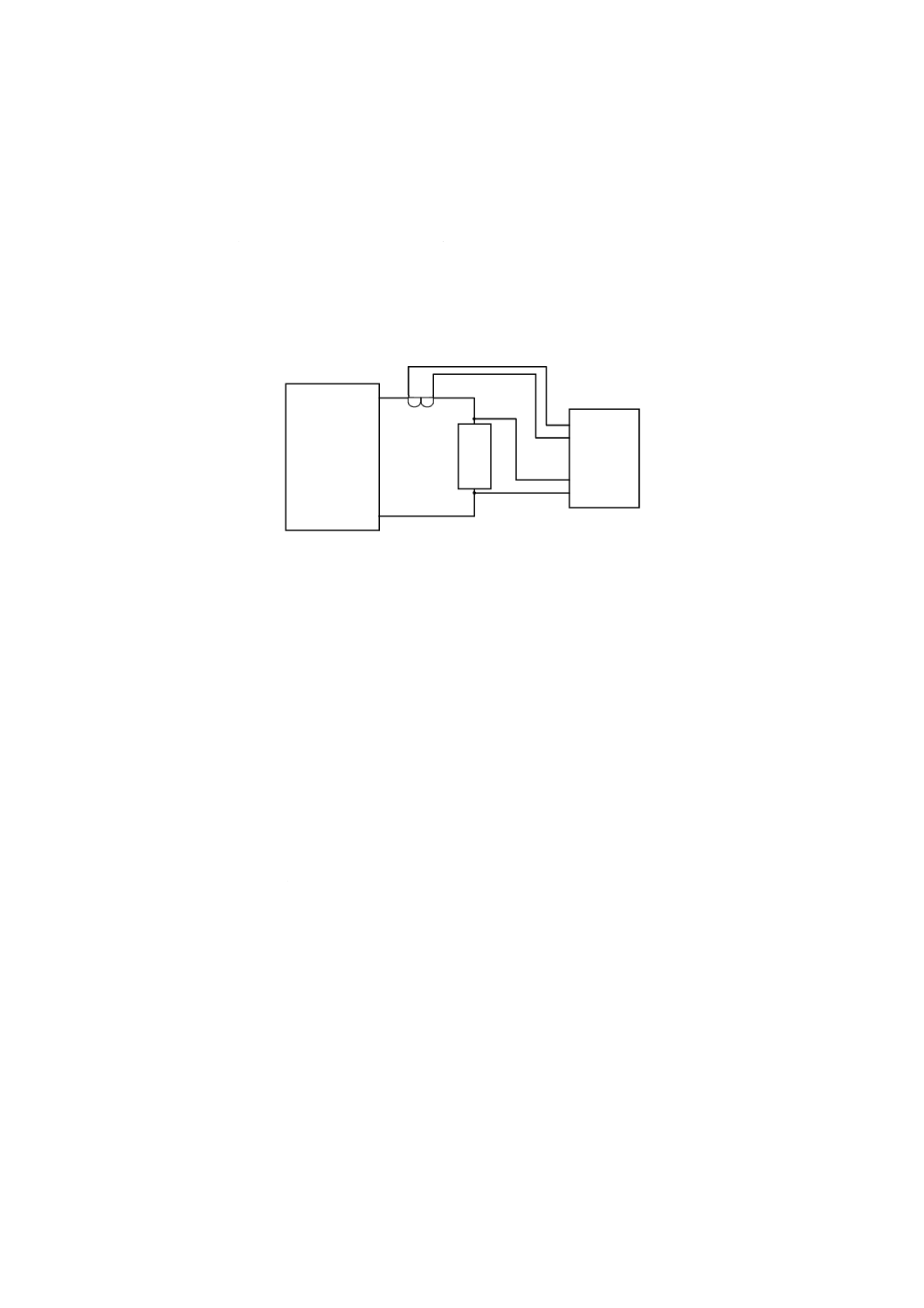

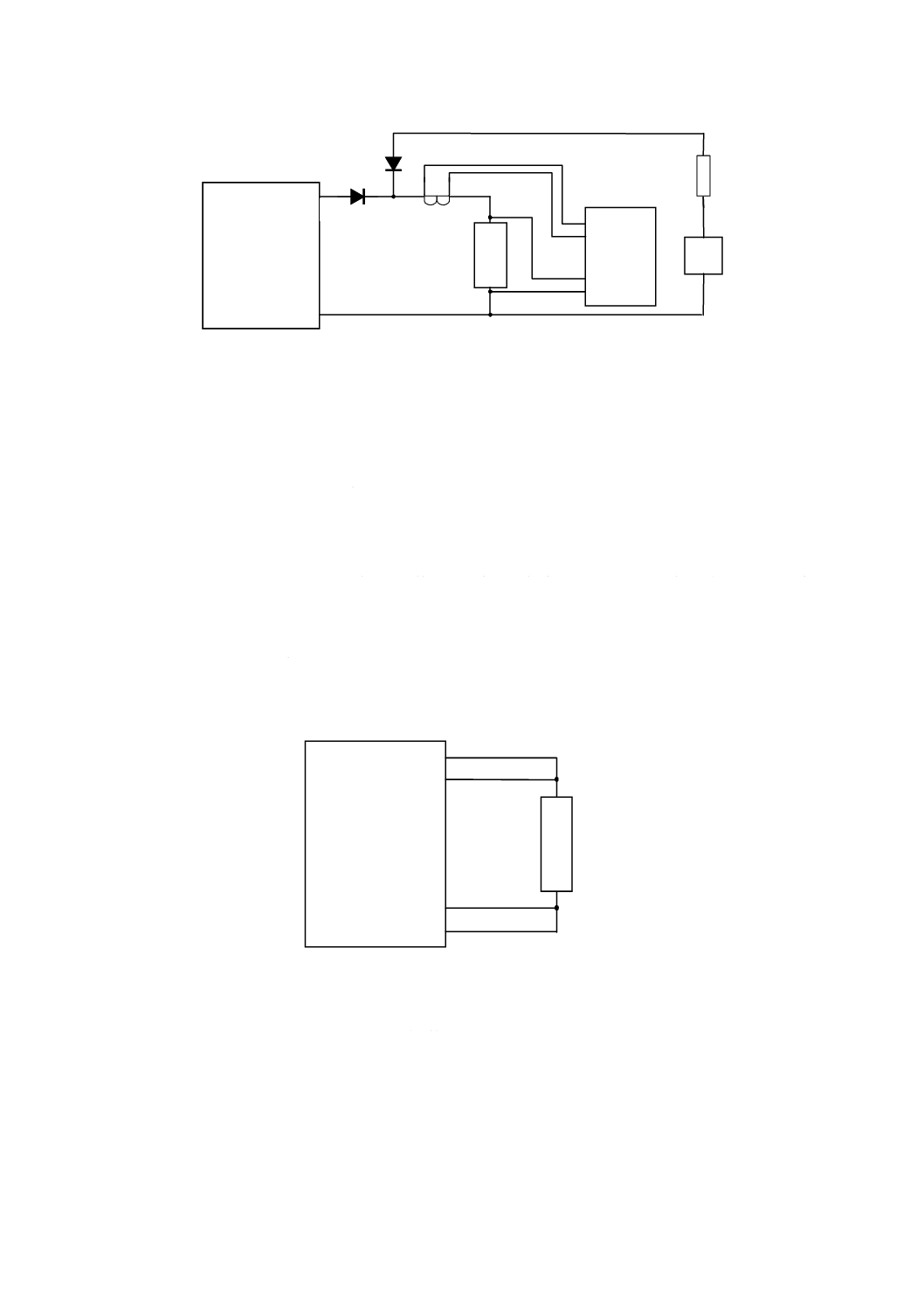

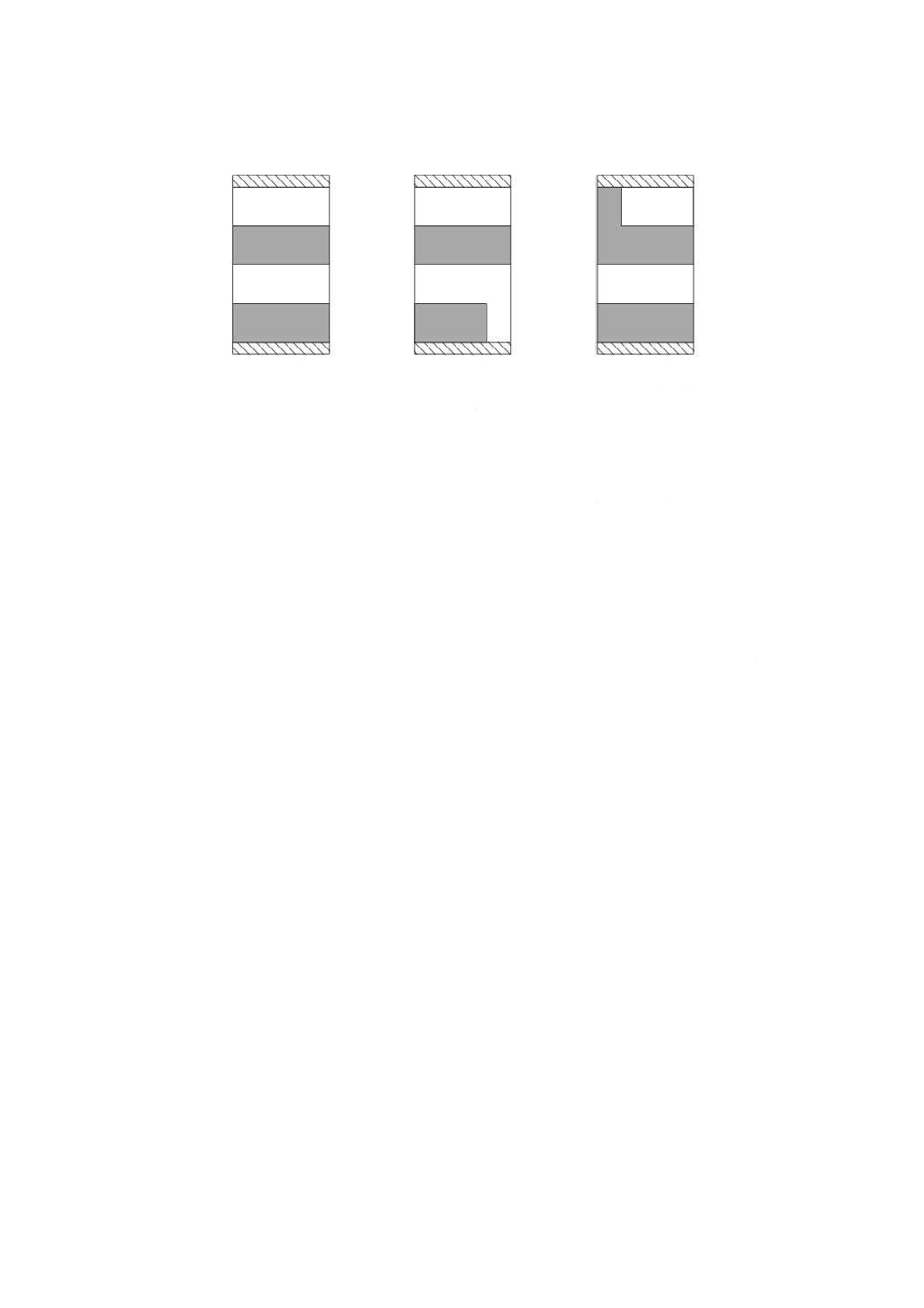

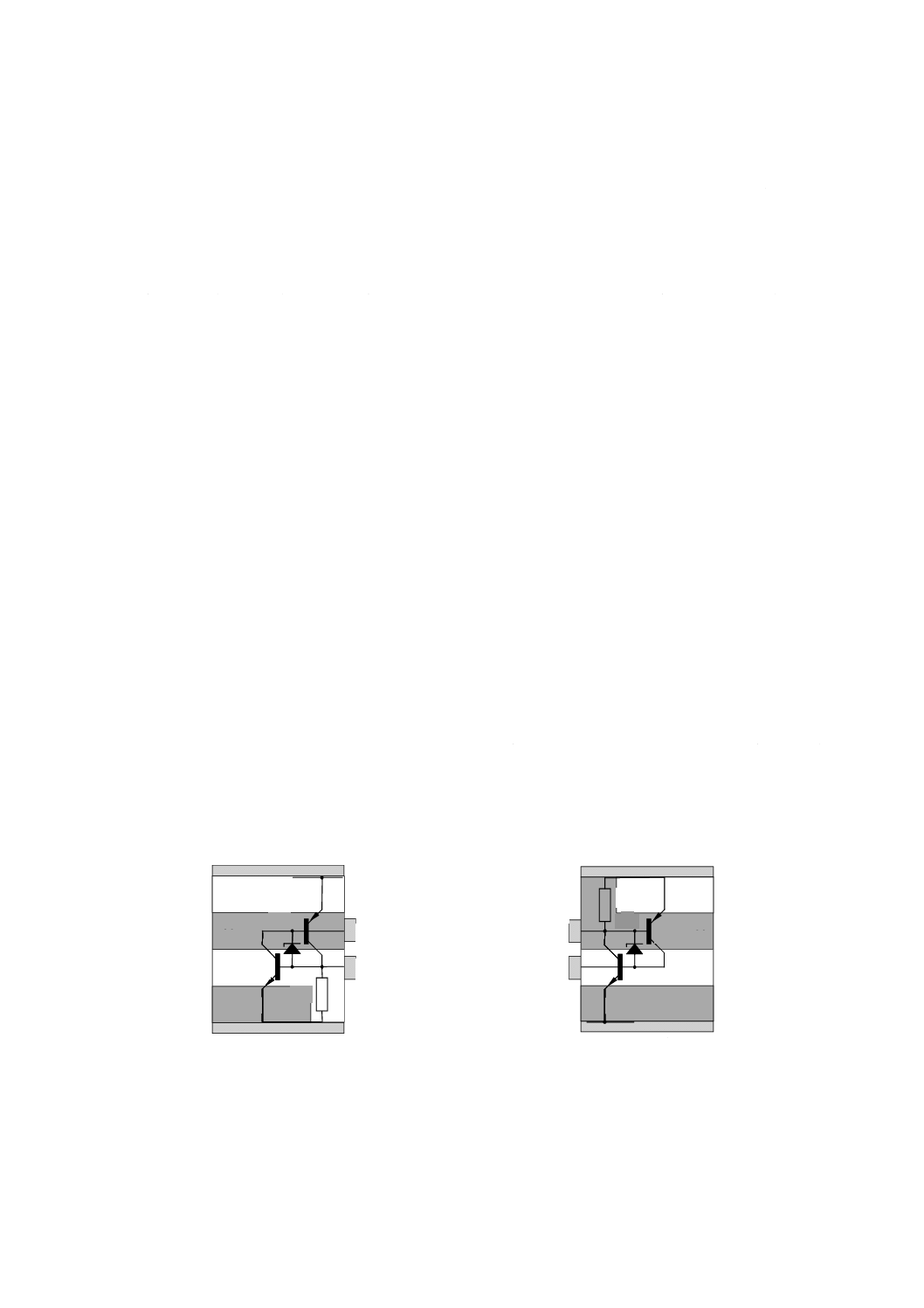

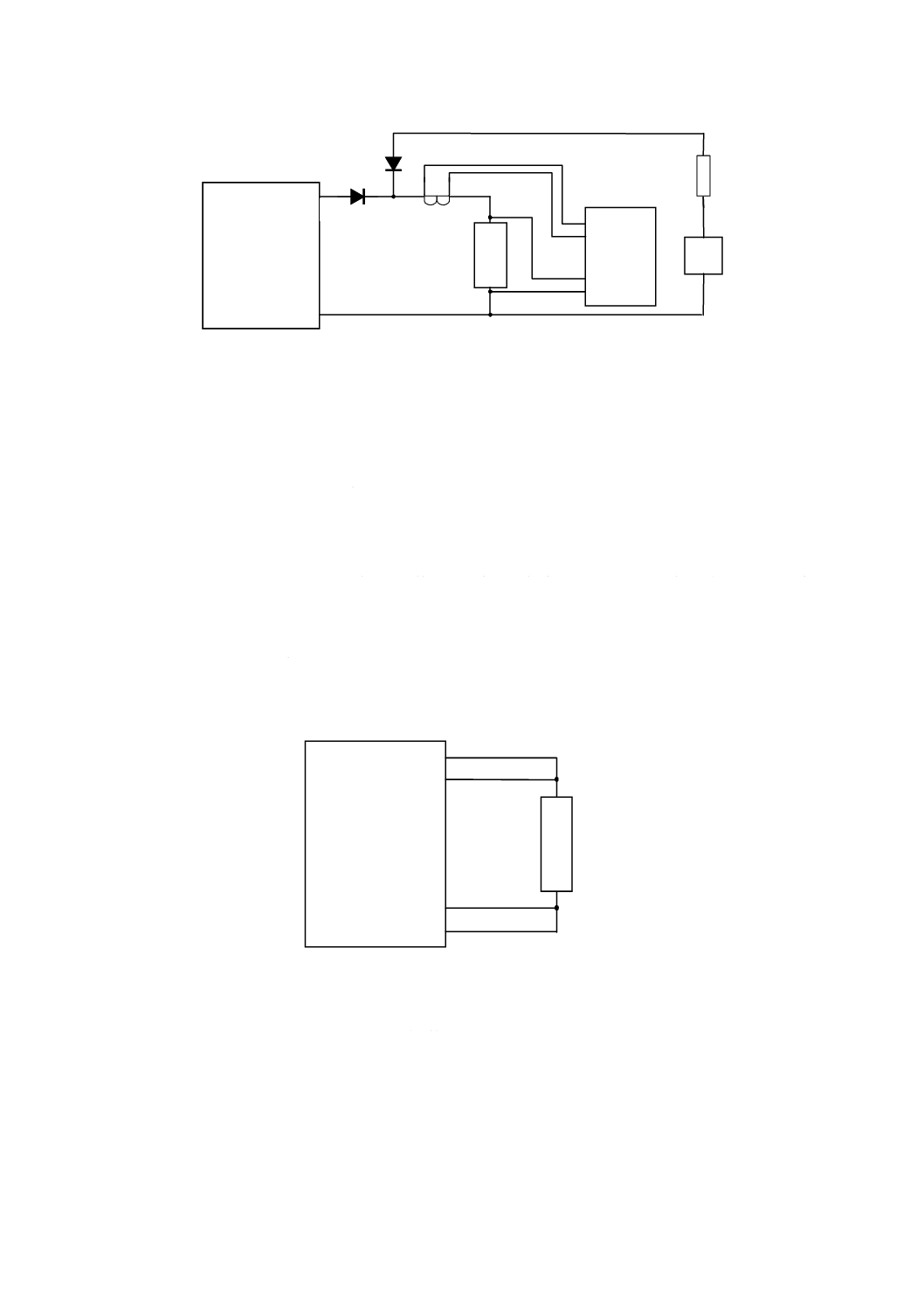

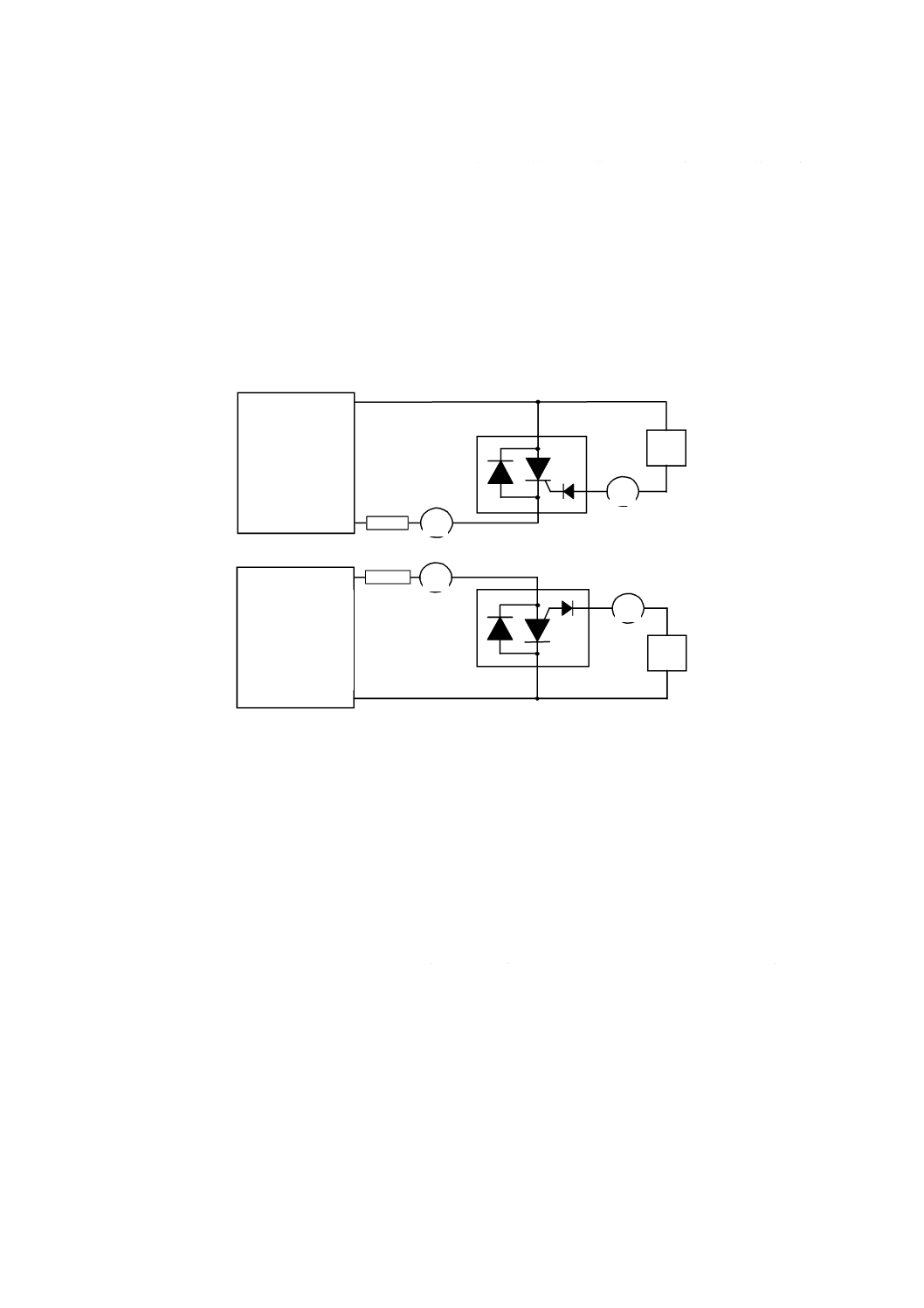

4.2

基本デバイス構造 TSSは,シリコンチップにN形層及びP形層を繰返し形成することで製造でき

る。基本的なサイリスタは,三つのPN接合をもつ4層構造である[図3a)参照]。一層はシリコン基板自

体(P形又はN形シリコン)に作り,更に3層をPNPN構造として形成する。P形及びN形層への電気的

接続は,金属電極によって形成する(図3の上下斜線部に示す。)。

図3は,簡略化した3種類の片方向サイリスタ構造を示す。いったんスイッチオンすると,基本的なサ

イリスタは微小電流値まで導通を維持する。一方,TSSは十分に大きい電流値でスイッチオフしなければ

ならない。PN接合を電極と抵抗短絡することで,大きいスイッチオフ電流値を得ることができる。図3b)

はP形部のカソード電極への抵抗短絡を示し,図3c)はN形部のアノード電極への抵抗短絡を示す。スイ

ッチング象限は,上のアノード電極が下のカソード接続に対して正電位の場合に起こる。

12

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

N

N

P

P

アノード

a) 基本PNPN

サイリスタ

N

N

P

P

b) カソード短絡

サイリスタ

N

N

P

P

c) アノード短絡

サイリスタ

アノード

アノード

カソード

カソード

カソード

図 3 サイリスタの簡略化構造

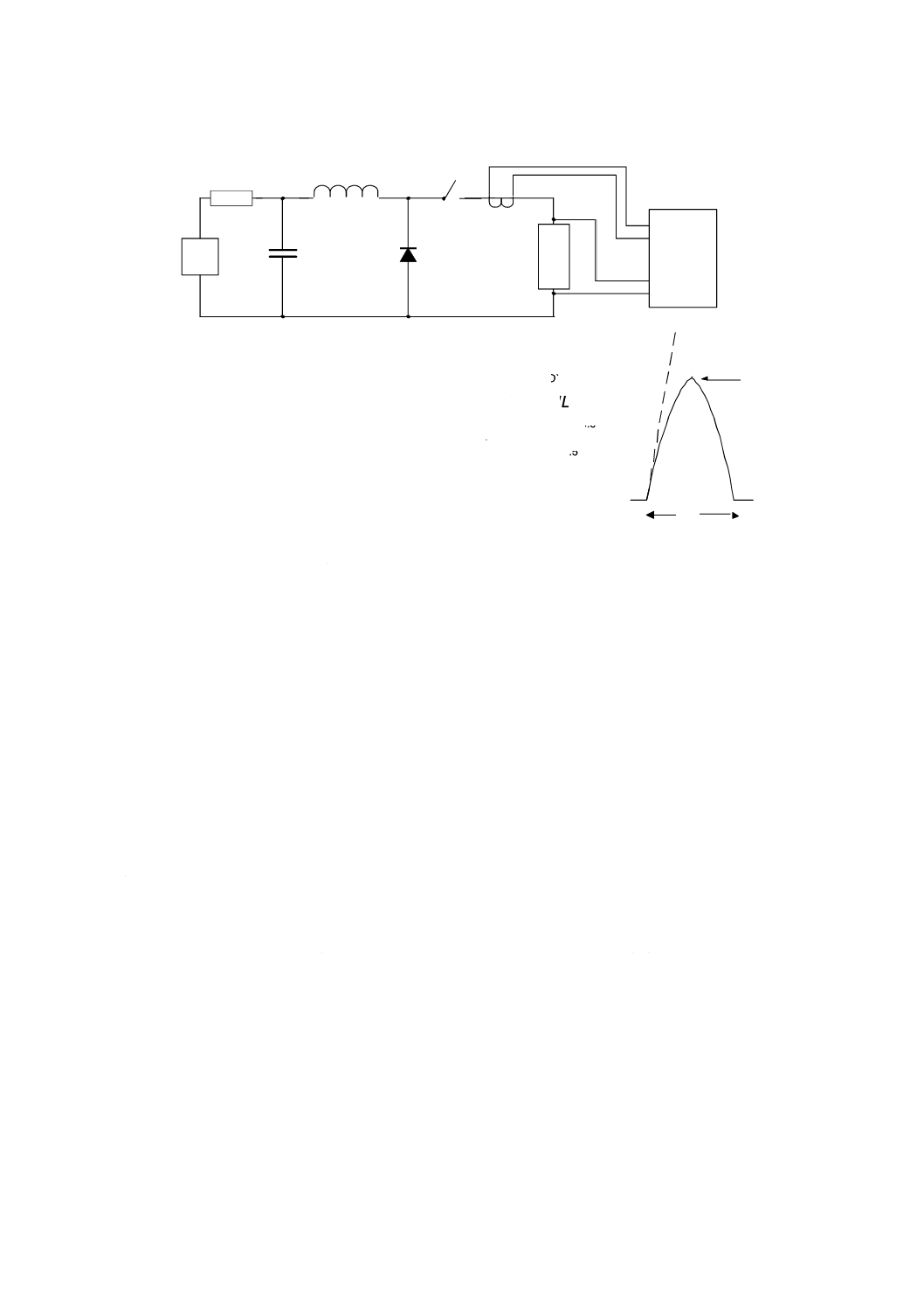

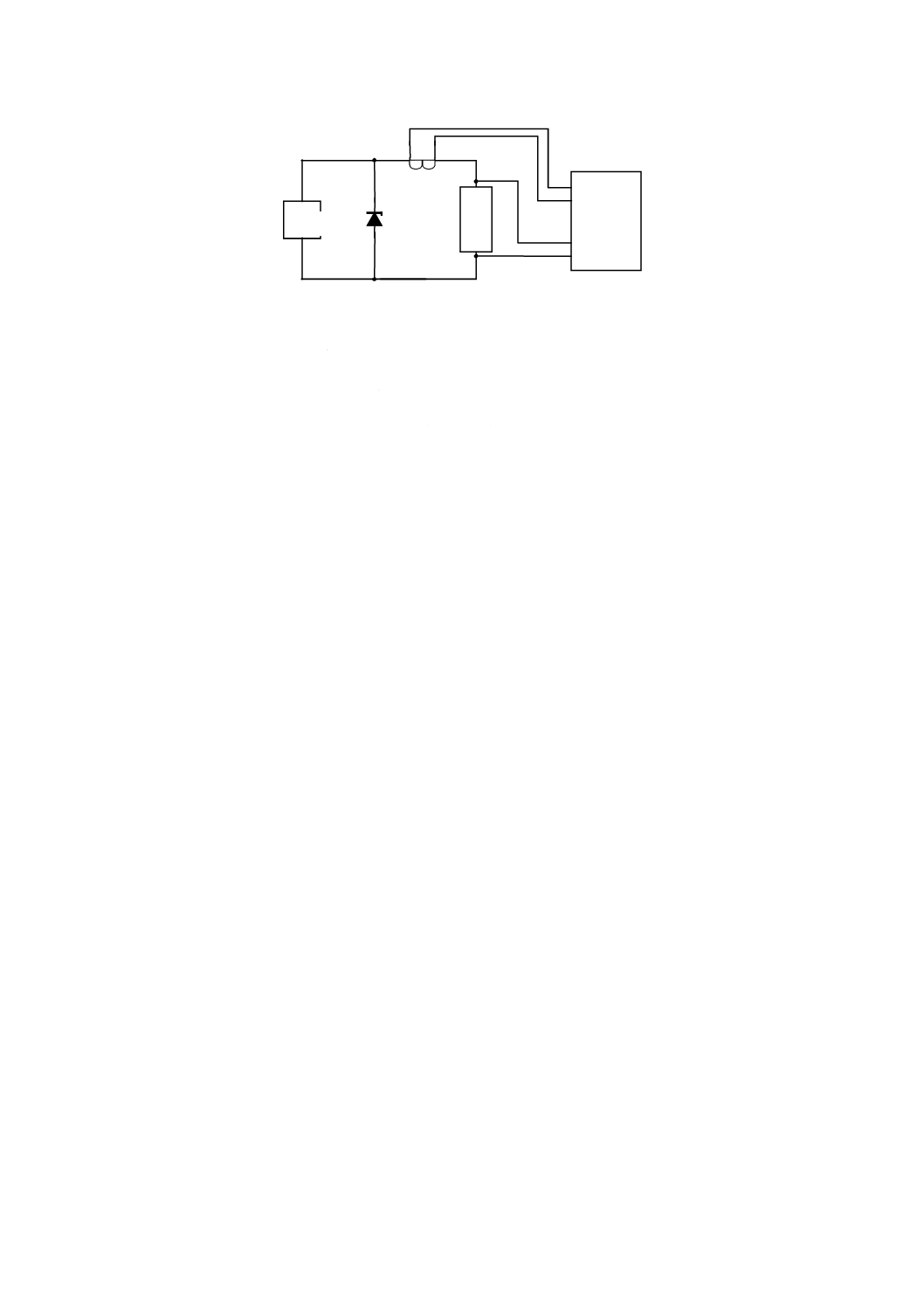

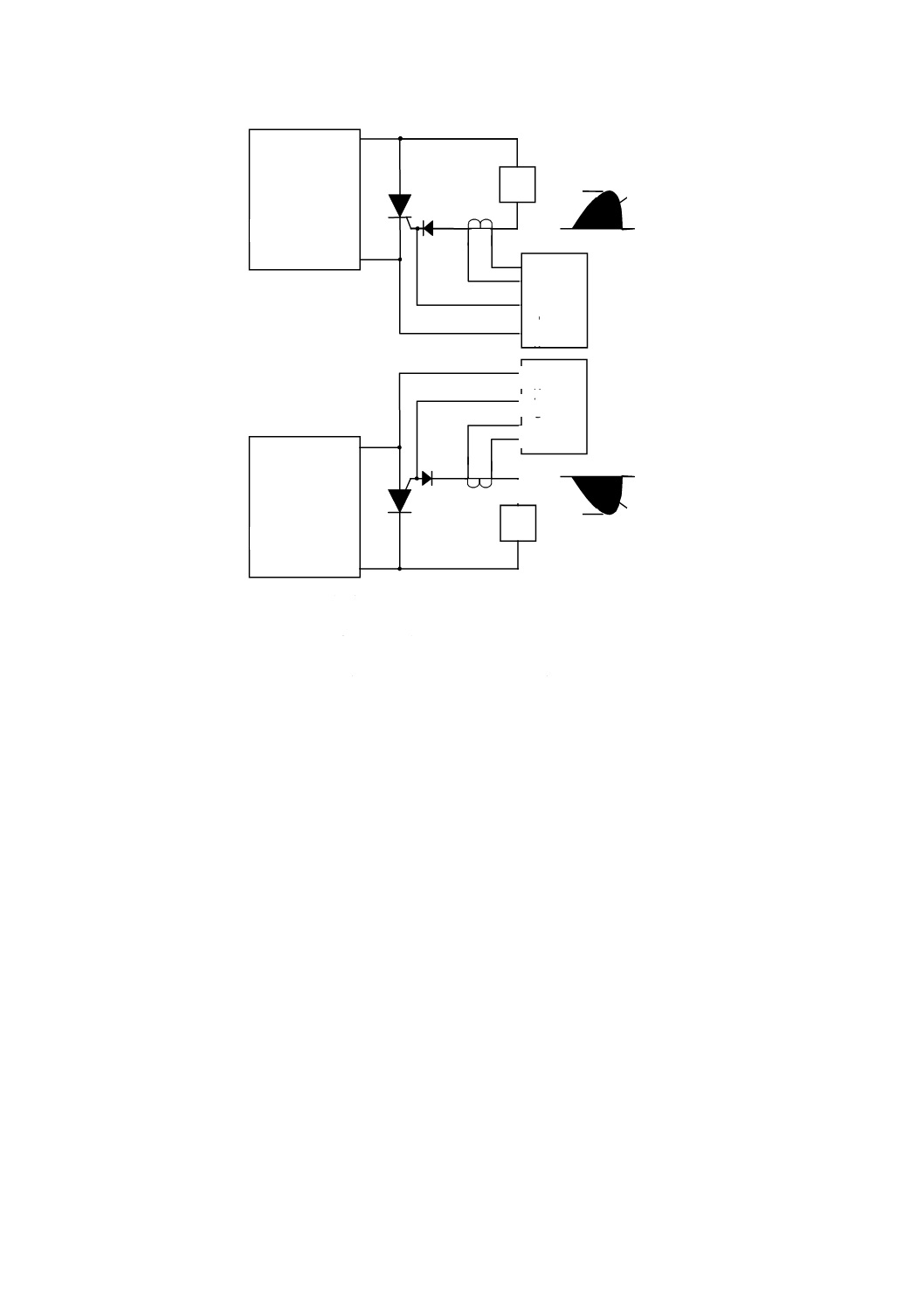

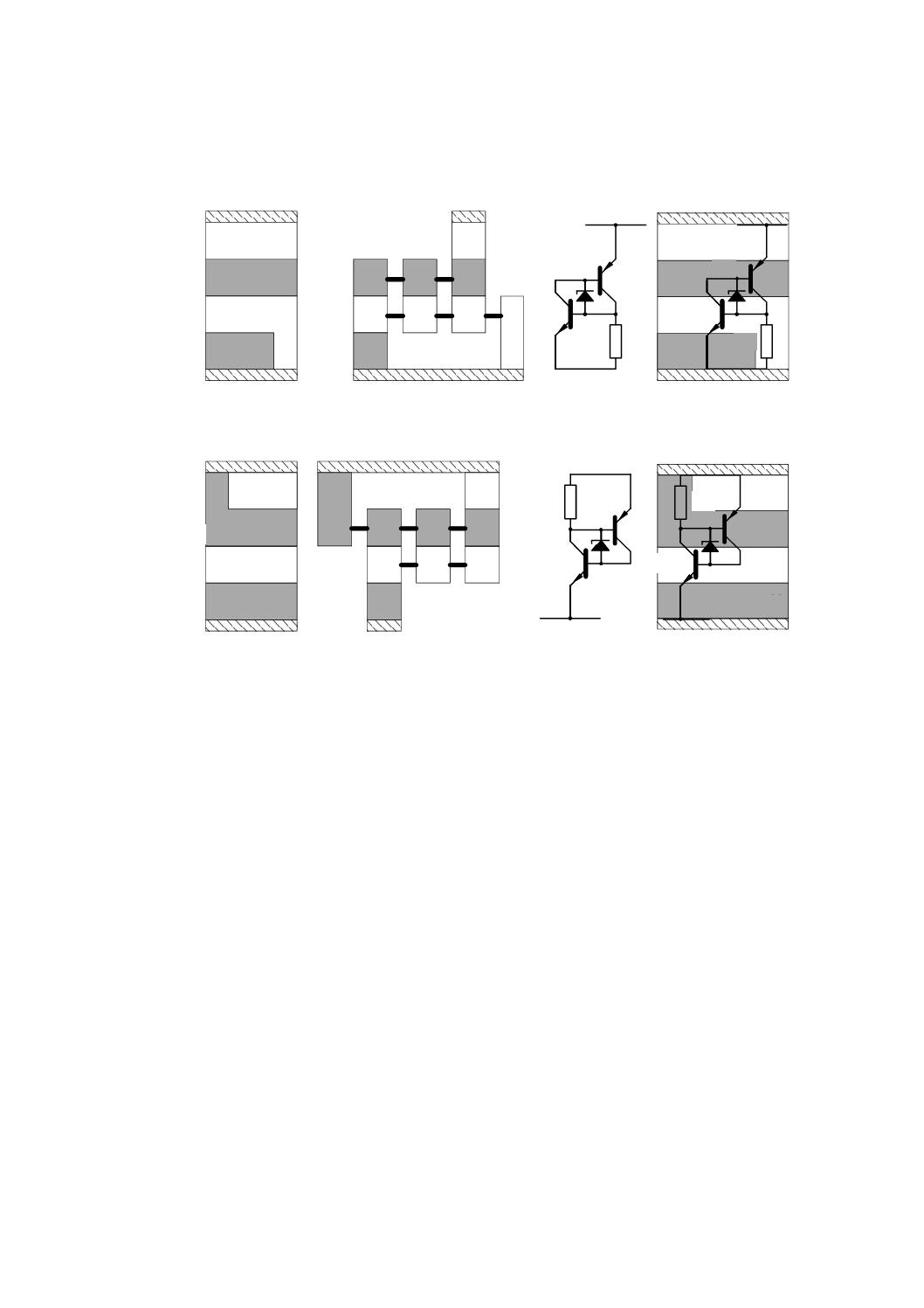

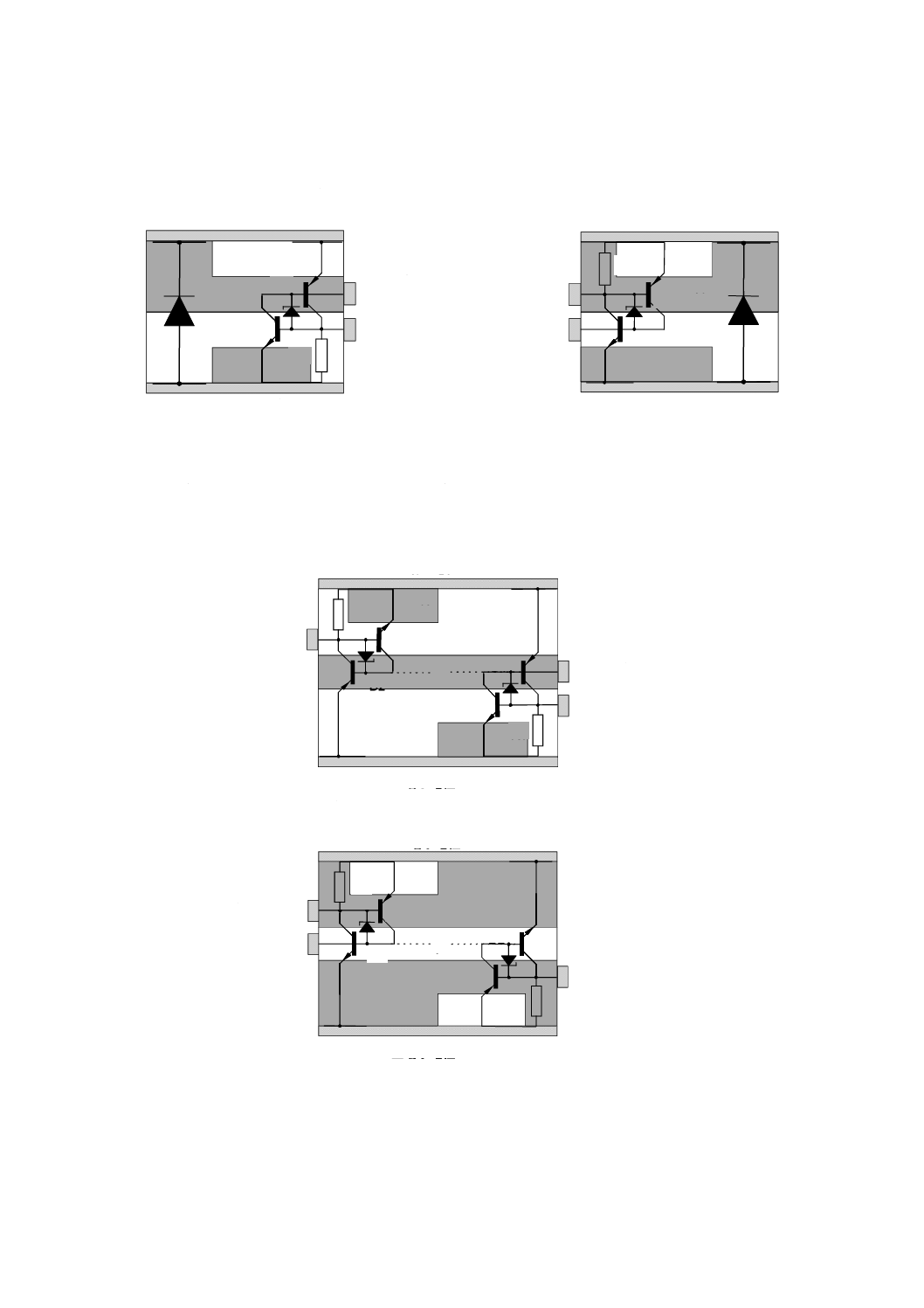

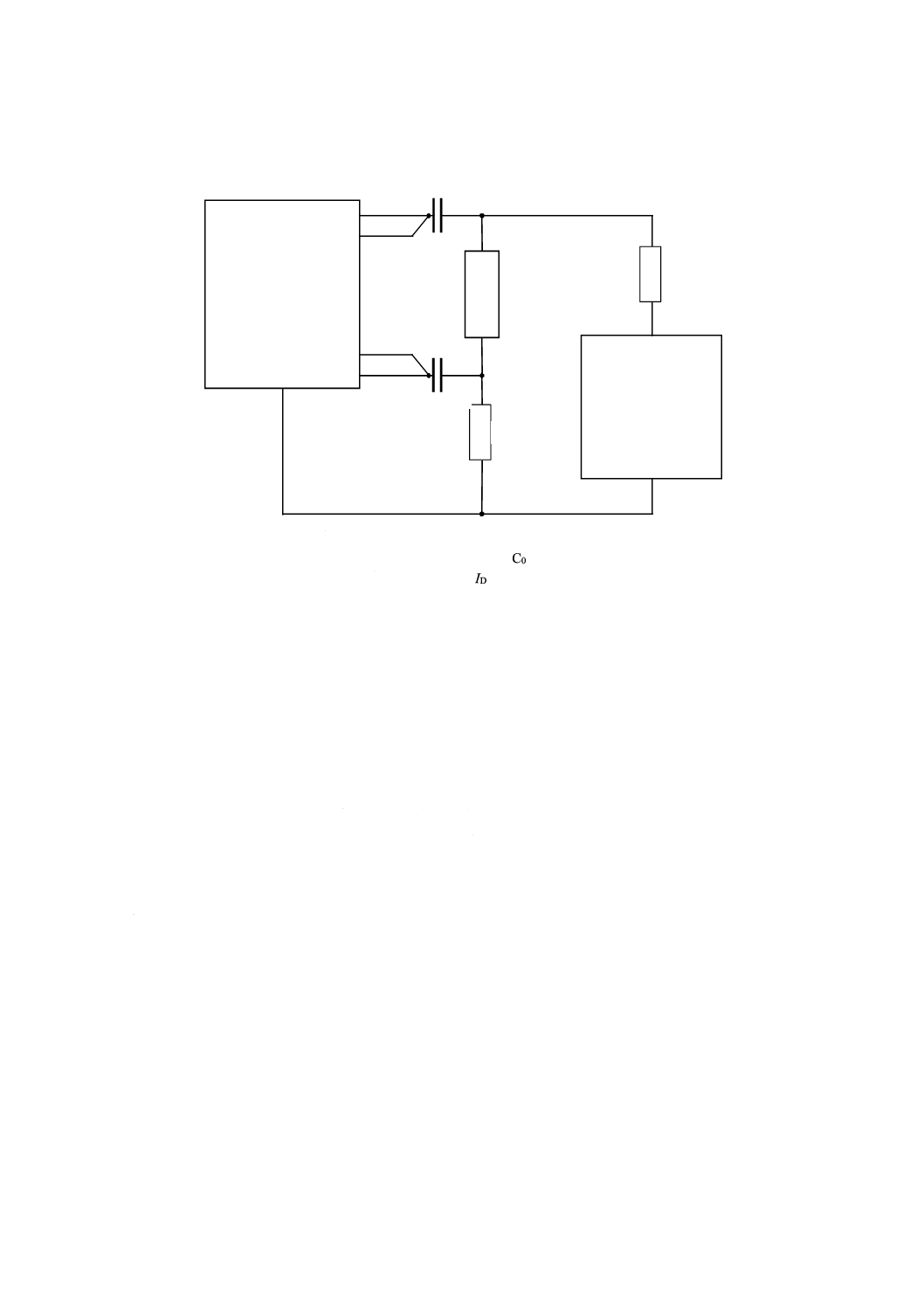

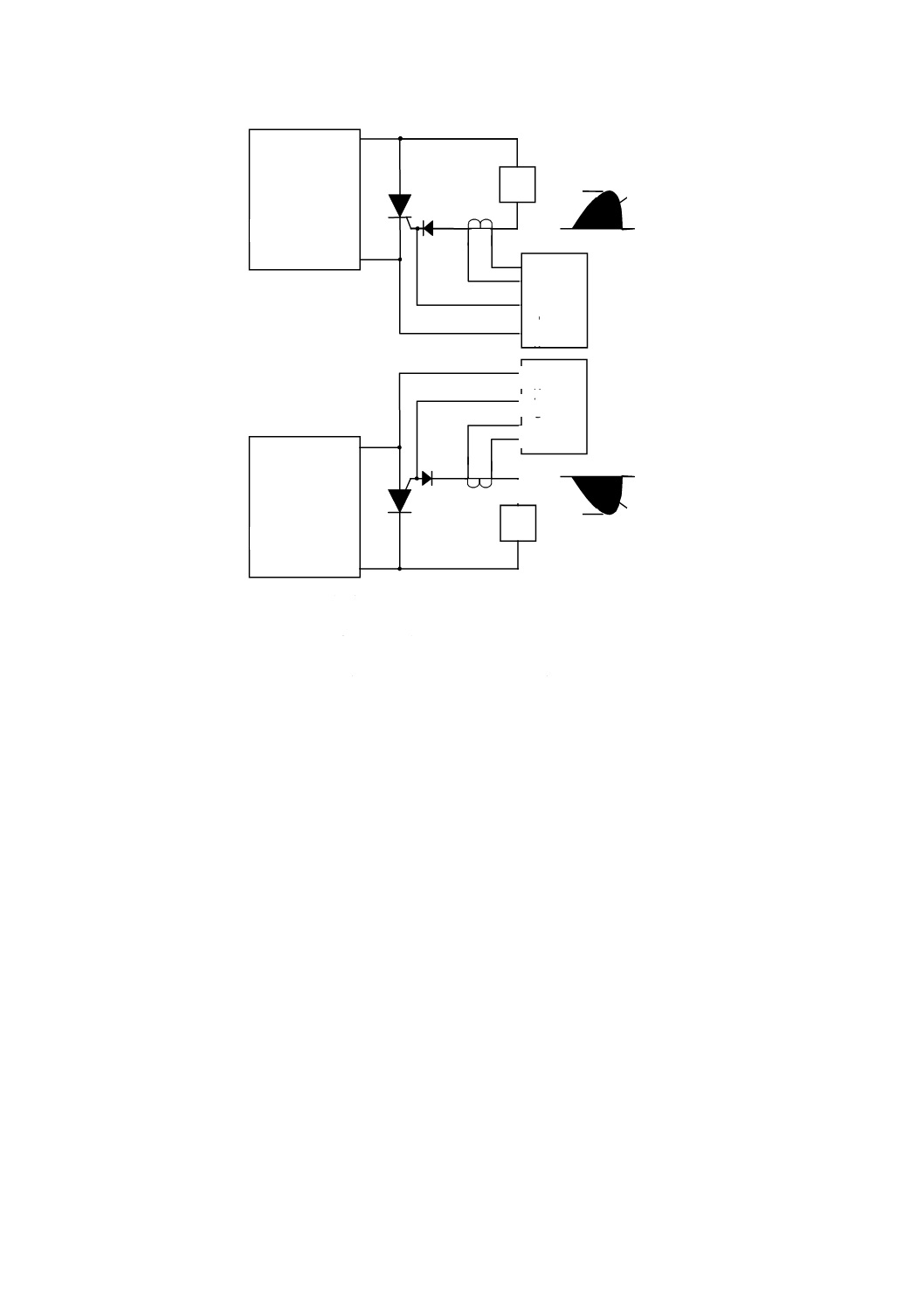

4.3

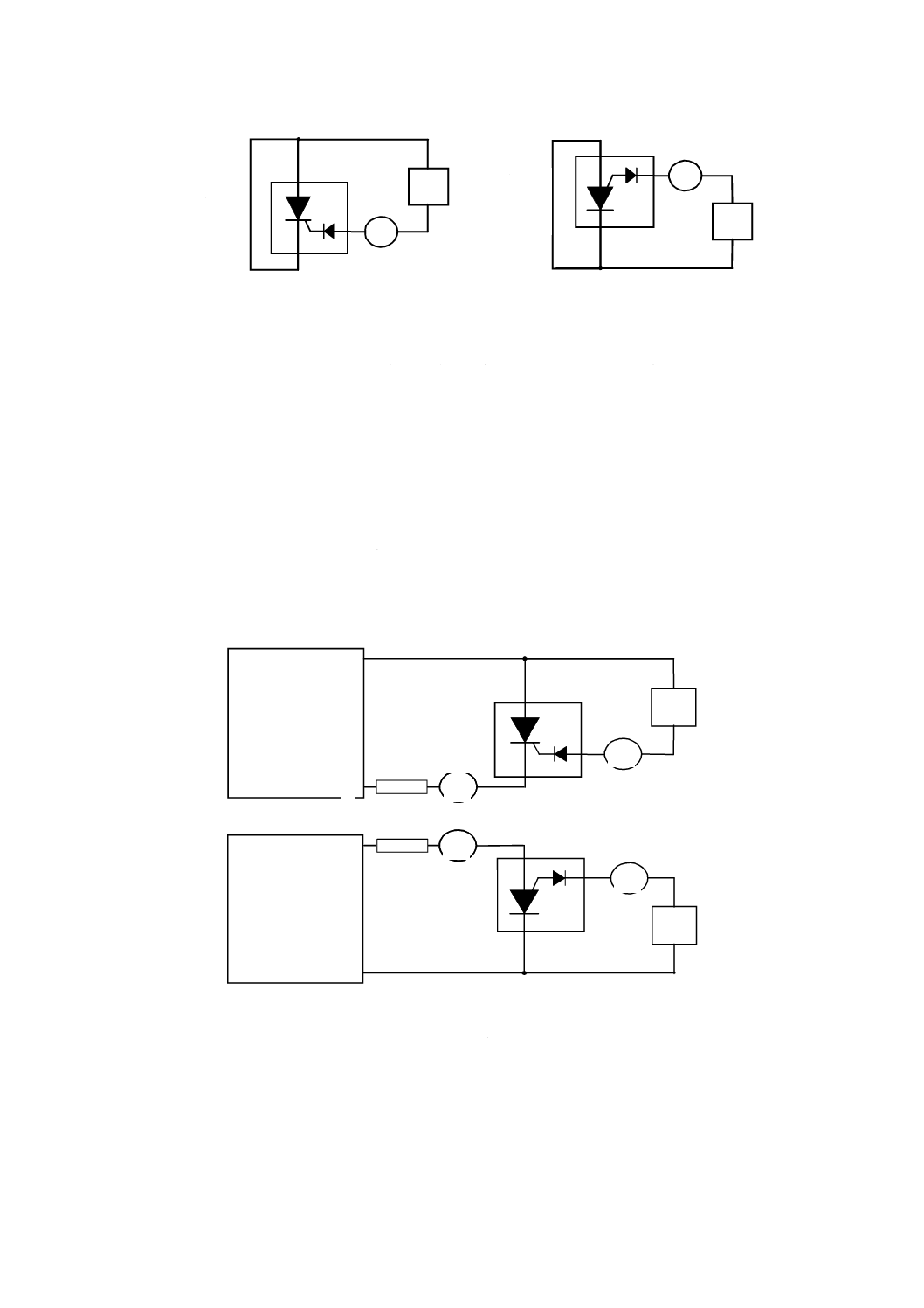

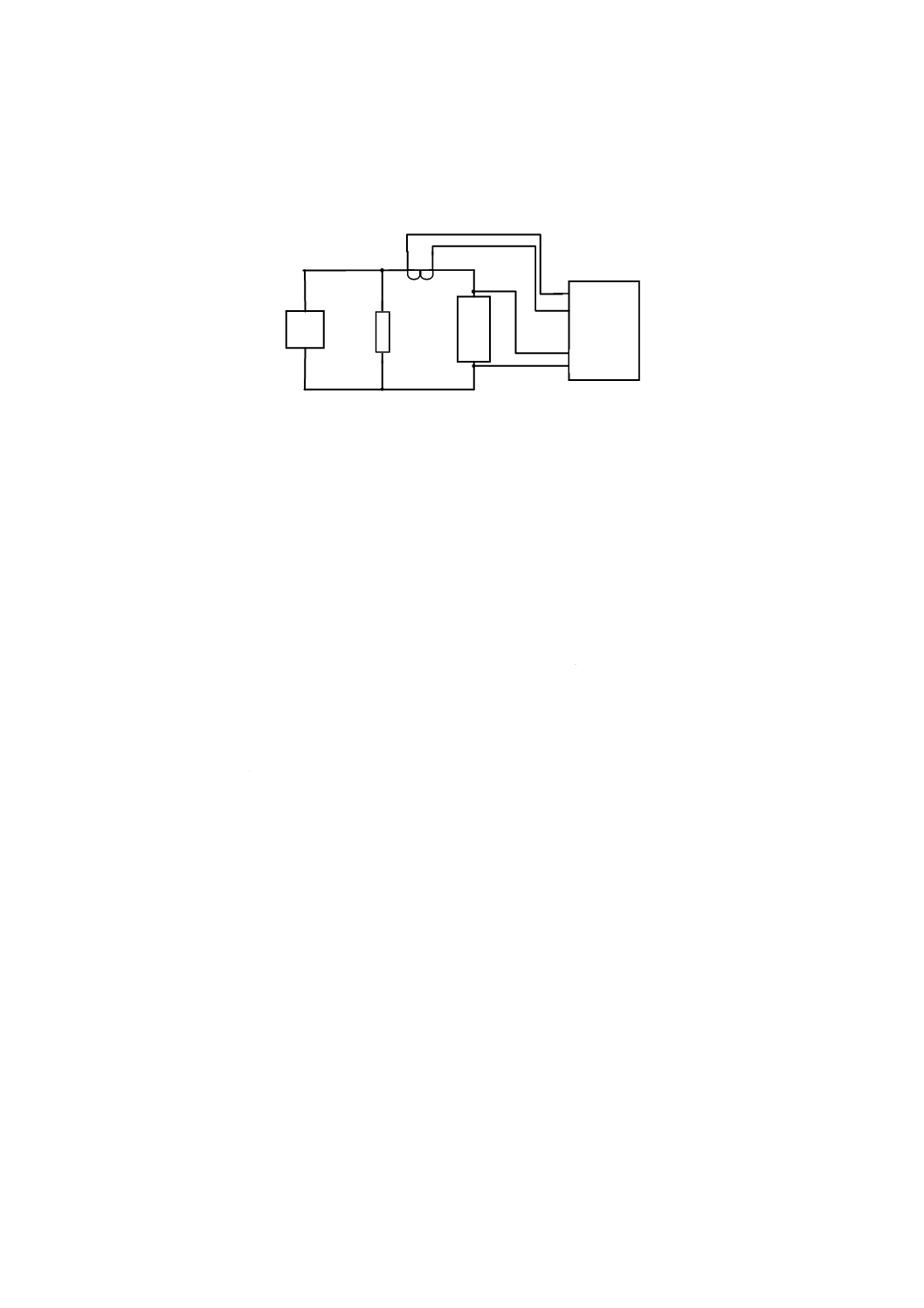

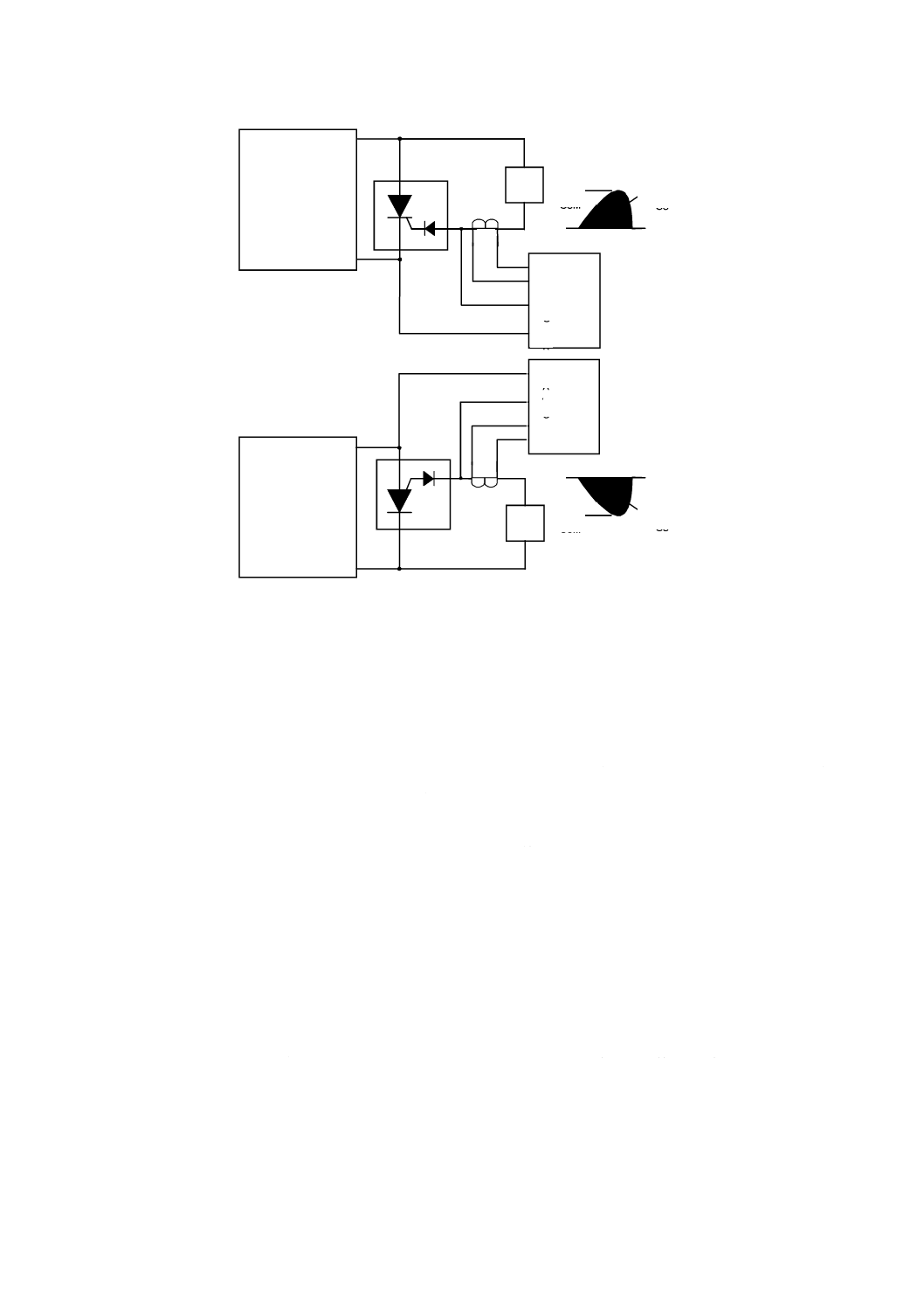

デバイス等価回路 図3に示す構造に基づき,図4にカソード短絡(P形短絡)TSS及びアノード短

絡(N形短絡)TSSの等価回路の導き方を示す。次に図4a)を用いてカソード短絡TSSの導き方を示すが,

図4b)のアノード短絡TSSについても同様である。

構造構成図において,簡略化構造は四つのシリコンブロックに分割できる。カソード電極に接続した第

一のNPN部は,NPNトランジスタTR1を形成する。第二のNP部は,アバランシブレークダウンダイオ

ードD1を形成する。アノード電極に接続した第三のPNP要素は,NPNトランジスタTR2を形成する。

カソード電極に接続した最後のP部は,短絡抵抗R1を形成する。各部の相互接続を太い水平線で示す。

13

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

b) アノード

短絡

N

N

P

P

TR1

TR2

R1

D1

N

N

P

N

P

N

P

P

N

TR1

D1

TR2

R1

TR1

TR2

R1

D1

N

N

P

P

a) カソード

短絡

カソード

N

N

P

N

P

N

P

P

P

TR1

TR2

R1

D1

R1

D1

TR1

TR2

N

N

P

P

アノード

R1

D1

TR1

TR2

N

N

P

P

簡易構造

構成部品構造

等価回路

構造 と 回路

TSS

タイプ

カソード

アノード

カソード

アノード

カソード

アノード

カソード

アノード

カソード

アノード

カソード

アノード

カソード

アノード

構造構成

構造及び回路

簡略化構造

図 4 TSS構造の等価回路

等価回路図は,構造構成図で定義した回路要素から導いた回路図である。トランジスタTR1及びTR2

は回生動作的ペア(regenerative pair)として接続する。不動作条件では,これらのトランジスタはオフ状

態にあり,高い回路インピーダンスを示す。十分な正の電圧を印加すると,ダイオードD1はブレークダ

ウンして電流をトランジスタのベース領域に供給する。初期状態ではトランジスタTR2が導通し,トラン

ジスタTR1のベース−エミッタ間の短絡抵抗R1が電流をバイパスする。この条件においてデバイスの電

圧電流特性は,トランジスタTR2のBVCEO特性で決まる。十分な電流が短絡抵抗R1に流れると,トラン

ジスタTR1の導通が開始するために,トランジスタのペアは回生し,低電圧のオン状態にスイッチ(クロ

ーバ動作)する。トランジスタのペアは,導通電流が少なくなり,動作トランジスタTR1の短絡抵抗にお

ける電圧を維持できなくなるまでこの状態を維持する。トランジスタのペアがスイッチオフ(非ラッチン

グ)動作を始めるときの電流を保持電流と呼ぶ。

構造及び回路図では,回路要素が構造に対して適切な位置となるように,簡略化構造上に等価回路を重

ねている。

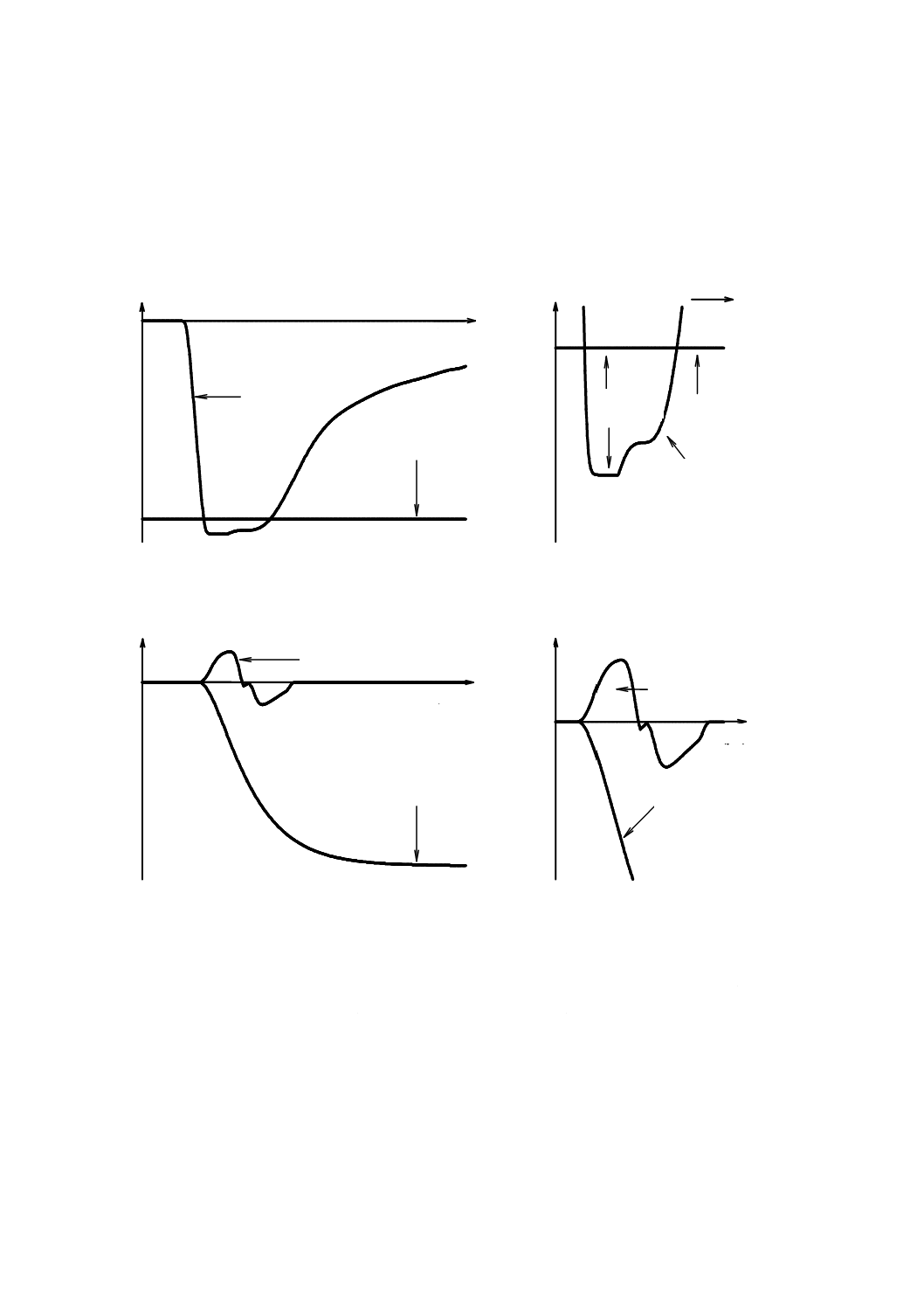

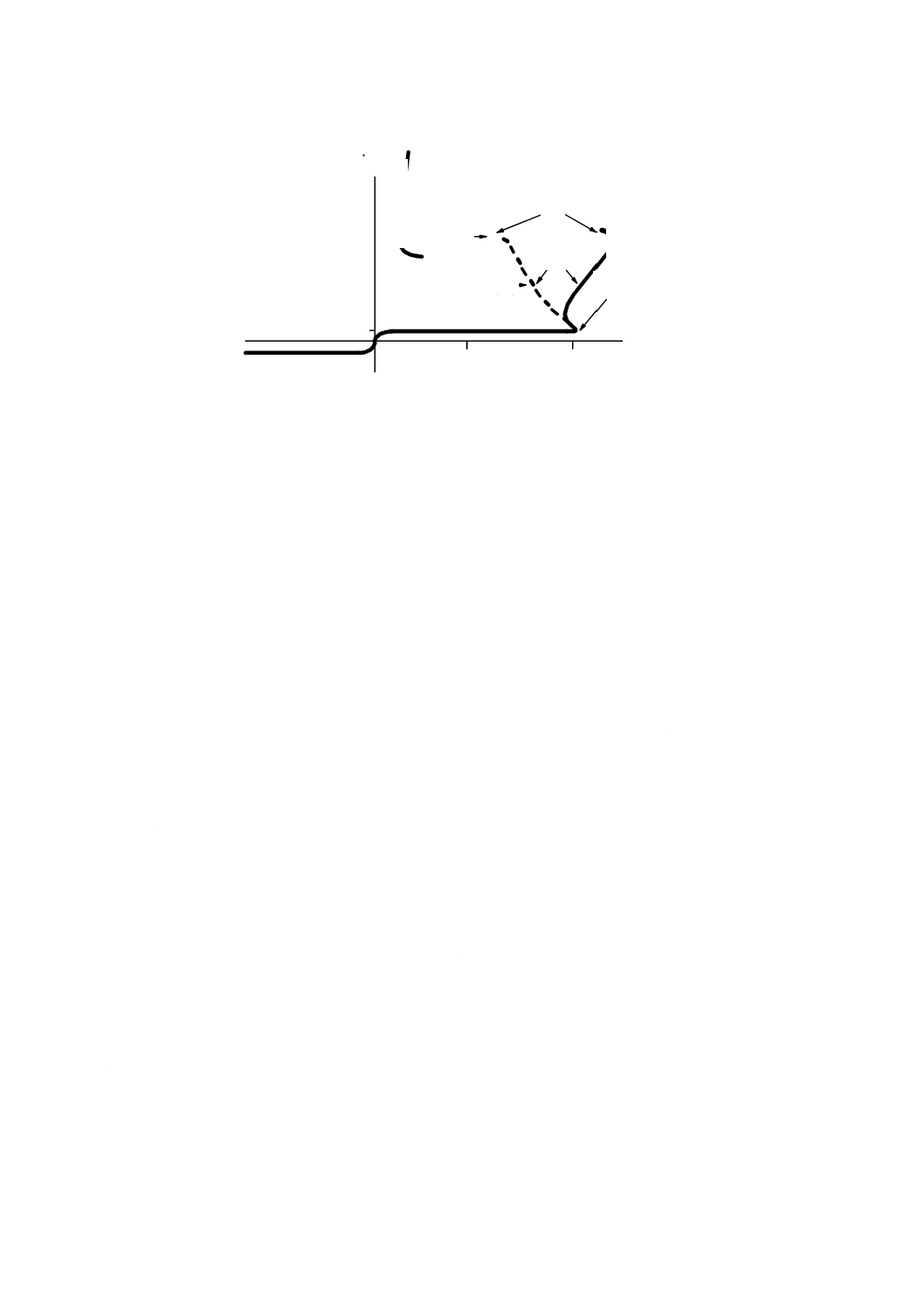

4.4

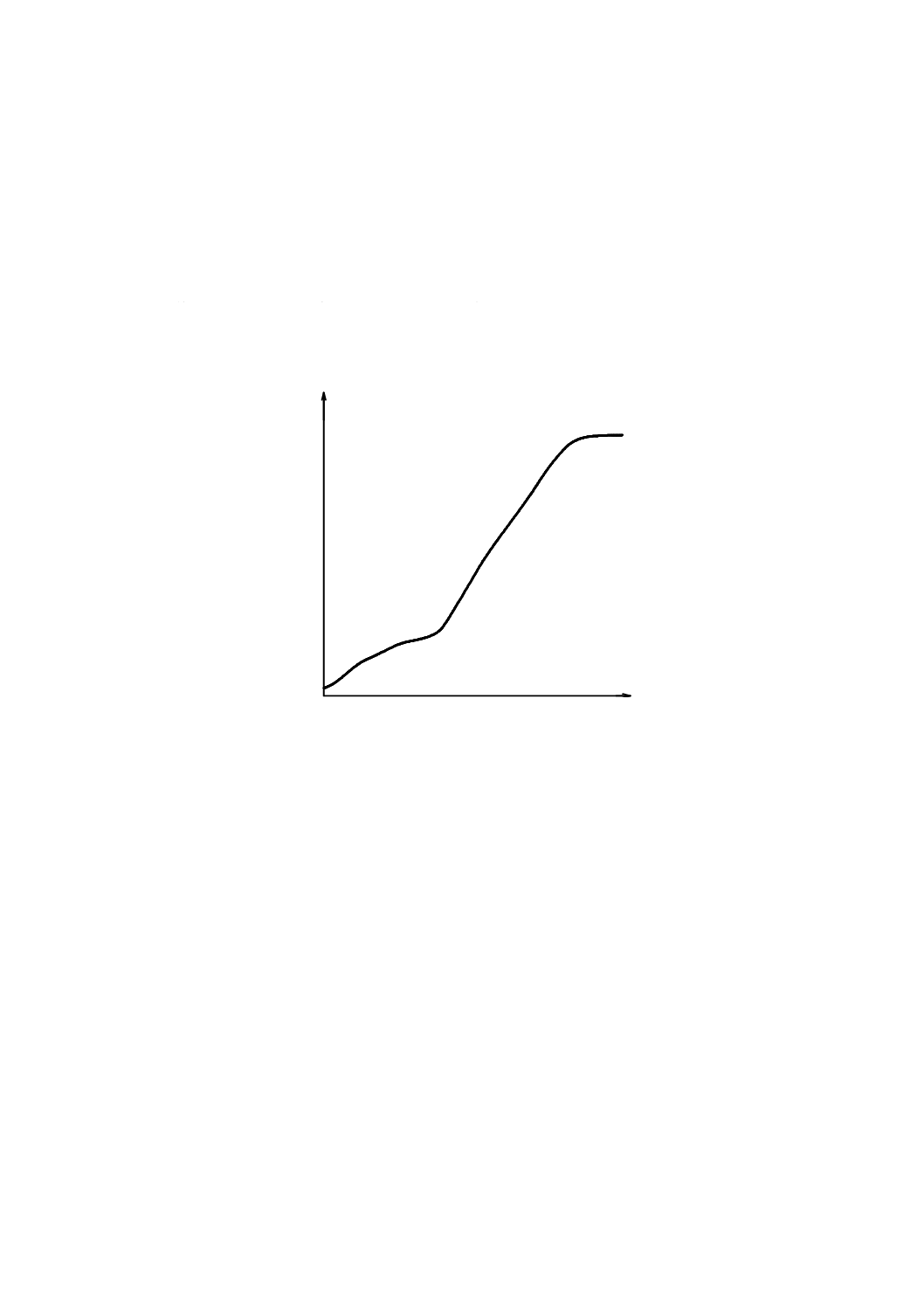

スイッチング象限特性 TSSのスイッチング特性は,次に示す四つの領域からなる(図5参照)。

a) オフ状態

b) ブレークダウン

c) 負性抵抗

d) オン状態

14

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

第一象限

第四象限

VDRM

I(BR)

V(BR

)

V(BO)

VS

IH

VD

ID

i

v

オフ状態

オ

ン

状

態

ブ

レ

ー

ク

ダ

ウ

ン

状

態

IS

領域

領

域

ブ

レ

ー

ク

ダ

ウ

ン

領

域

第三象限

V(BR)

図 5 TSSのスイッチング特性

4.4.1

オフ状態領域 オフ状態領域は,電圧電流特性の高抵抗・小電流部である。この領域は,原点から

ブレークダウンの手前まである。オフ電流は,逆接合電流及び表面漏れ電流の合計である。この領域では,

次に示すような二つの測定がある。

− 直流のオフ電圧(VD)印加において測定するオフ電流(ID)

− 定格繰返しピークオフ電圧(VDRM)印加において測定する繰返しピークオフ電流(IDRM)

4.4.2

ブレークダウン領域 ブレークダウン領域は,電圧電流特性の低抵抗・高電圧部である。この領域

は,電圧電流特性の小電流部分の変化が,電流の増加によって高い動的抵抗部から十分に低い動的抵抗に

移行するところで始まる。最終的にこの領域は,十分なサイリスタ回生電流によってスイッチング起動を

生じるときに終了する。ブレークダウン領域の終わりは,サイリスタの設計及び温度に依存し,開始電圧

より高くなっても又は低くなってもよい。この領域の低抵抗特性は,接合のアバランシブレークダウンに

トランジスタ動作を含んだ結果である。ブレークダウン領域で生じる最大電圧は,ブレークオーバ電圧

[V(BO)]と定義する。付加的に,指定したブレークダウン電流[I(BR)](正性ブレークダウンスロープTSS

デバイスの場合)のブレークダウン電圧[V(BR)]並びにスイッチングポイントの電圧及び電流(Vs,Is)を

測定してもよい。

4.4.3

負性抵抗領域 負性(負の傾きをもった)抵抗領域は,ブレークダウン領域のスイッチングポイン

トからオン状態に移行する軌跡を表す。この領域は動的状態であり,オン状態の条件に到達するまでサイ

リスタ間の電圧を引き下げるような増加電流要求に起因するサイリスタの回生電流が時間とともに増加す

る。

4.4.4

オン状態領域 オン状態領域は,電圧電流特性の低抵抗,大電流部である。オン状態条件でサイリ

スタは十分に回生し,この電流によって最小の電圧降下を生じる。オン状態条件を維持する最小電流を,

保持電流(IH)として定義する。この値未満の電流では,サイリスタはスイッチオフとなる。

4.5

TSSの性能基準 TSSの特性は,三つに分類できる。

a) システム負荷:電流特性図,保持電流及び静電容量による。

b) 機器防護:侵入するピーク電圧及び故障モードとして定義する。

c) 耐久性:サージ寿命及び環境寿命として評価する。

15

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.5.1

システム負荷 通常のシステム動作において,TSSは無影響であることが望ましい。TSSは,スタ

ンバイ状態若しくは最大信号状態での過大な電流通過,サージ後の通常動作への未復帰又は静電容量の差

異によるライン不平衡によって,システム負荷とならないほうがよい。

スタンバイ状態での負荷は,パラメータのオフ電流IDの範ちゅう(疇)である。多くの電話回線への適

用に対して,−50 Vの試験バイアス電圧VDは適切である。オフ電流は,温度に従って増加するため,こ

のパラメータは,想定されるシステムの最高周囲温度における最大値として規定する必要がある。

主な電圧クリッピングなしの最大システム電圧は,二つのパラメータの一つとして定義することができ

る。TSSが最高信号振幅においてオフ状態を維持することを保証するために,繰返しピークオフ電圧VDRM

は,このレベルより低くてはならない。多くのシステムでは,数ミリアンペアのクリッピング電流は,シ

ステム動作の妨げとはならない。このような場合,正性ブレークダウンスロープをもつTSSデバイスに対

して,小電流[I(BR)=1 mA]のブレークダウン電圧V(BR)は,最高信号振幅に等しいと規定できる。これら

の両パラメータの電圧値は,低温で低下するため,要求値は,想定されるシステムの最低周囲温度で規定

することが望ましい。

TSSによって信号線を大地に対して防護している場合,ラインの不平衡は,防護器の静電容量の差異に

よって生じる。TSSのオフ状態静電容量は,接合温度TJの上昇によって増加し,直流電圧VD及び交流信

号電圧Vdからなるバイアス電圧の増加に従い減少する。VD≫Vdの場合,静電容量は,Vdの値に対して無

関係となる。通常の電気通信周波数の範囲では,静電容量は一定であることが必須である。一対のTSSの

静電容量差異を正確に評価するには,通常動作を反映した試験条件でなければならない。

TSSが,サージ電流を分流するためにオン状態に移行し,サージ後に通常動作へ復帰するためにスイッ

チオフしなければならない。TSSの保持電流IHは,スイッチオフ電流を決定する。接合温度及び回路イン

ピーダンスの増加は,保持電流値を低下させる。保持電流は,最悪条件(例えば,電源回路インピーダン

ス及びデバイス接合温度が最大となる場合)で,最大直流ライン電流より大きいことが望ましい。一般に,

最大接合温度は,想定される最高周囲温度での交流電力サージ後に発生する。

4.5.2

機器防護 防護の目的のため,TSSの端子ピーク電圧は,すべての過電圧条件下で機器の定格電圧

を超えてはならない。幾つかの適用では最大サージレベルが不明であり,過大なサージレベルによって起

こる故障が望ましい故障モードとなるように設定しなければならない。

過電圧は,インパルス又は比較的長い交流ストレスに依存する。交流サージ条件では,加熱及び結果と

して生じる接合温度上昇がブレークオーバ電圧を上昇させる。小電流では,加熱はブレークダウン領域の

損失に依存する。大電流は,オン状態領域における主損失の原因となる。ピークインパルス電圧は,上昇

増加のインパルスの上昇率に従い増加する。

サージがTSSの能力を大きく超える場合には,TSSは破壊する。電気通信分野での適用では,二つの防

護のクラス(一次及び二次)がある。一次防護は,ストレスのあるエネルギーの大部分が指定したインタ

フェースを超えて波及することを防止するシステム位置に適用する。二次防護は,一次防護の後に適用し,

より小さく,より限定的なストレスレベルに対応する。過大なサージ条件下では,一次防護器が短絡によ

り破損することで,更なるサージの波及を防止することが望ましい。一次防護器は,故障モードが安全で

効果的であることを保証するために,一般に破壊試験を実施する。

4.5.3

耐久性 TSSは,適切な耐用年数及び設計寿命をもっていなければならない(一般的には20年程

度)。この期間の大部分は標準動作条件下での値であり,製品は期待寿命を検証するための一連の環境加速

試験に合格しなければならない。サージ条件は小さいが,耐久寿命の重要な部分を占めている。サージに

対する耐久性は,各種の電流レベルで防護器に繰返しサージを印加することによって評価する。

16

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.6

追加のTSS構造

4.6.1

ゲート付きTSS これらのデバイスは,スイッチング領域特性を制御するゲート(G,g)端子及

び防護機能を備えた2主端子をもっている。追加端子をTSSの中間のP形又はN形層若しくは複合形NP

領域に接続する3ゲートタイプも可能である。ゲート制御なしの動作も許容するよう設計しているゲート

付きTSSもある。ゲート制御なしの場合,デバイスの動作及び特性は,定電圧TSSと同じである。

すべてのゲート付きTSSは,回生動作的ペアとして接続されるPNPトランジスタ及びNPNトランジス

タと等価である(図4参照)。不動作状態において,このトランジスタ対はオフ状態にあり,高回路インピ

ーダンスを示す。ゲート端子層及びその隣接した主端子層は,PN接合を形成する。電流がこのPN接合に

よって導通すると,電荷キャリアはトランジスタ対に注入される。十分なゲート電流が流れるとトランジ

スタ対は回生動作し,低電圧オン状態にスイッチ(クローバ動作)する。トランジスタ対は,主電流が非

常に少なくなりトランジスタ対の導通を維持できなくなるまでこの状態を保持する。

ゲート電流には,二つの電流ループが起こり得る。一つは,ゲート電流を生成する回路がゲート端子及

び隣接した主端子に接続する場合であり,もう一つは,ゲート電流を供給する回路が主端子間に接続する

場合である。TSSがオフ状態にある場合,実質的には主端子間に流れる電流は存在しない。この状態で電

流のループは,ゲートとその非隣接主端子との間に接続する回路によって完了する。隣接主端子及びゲー

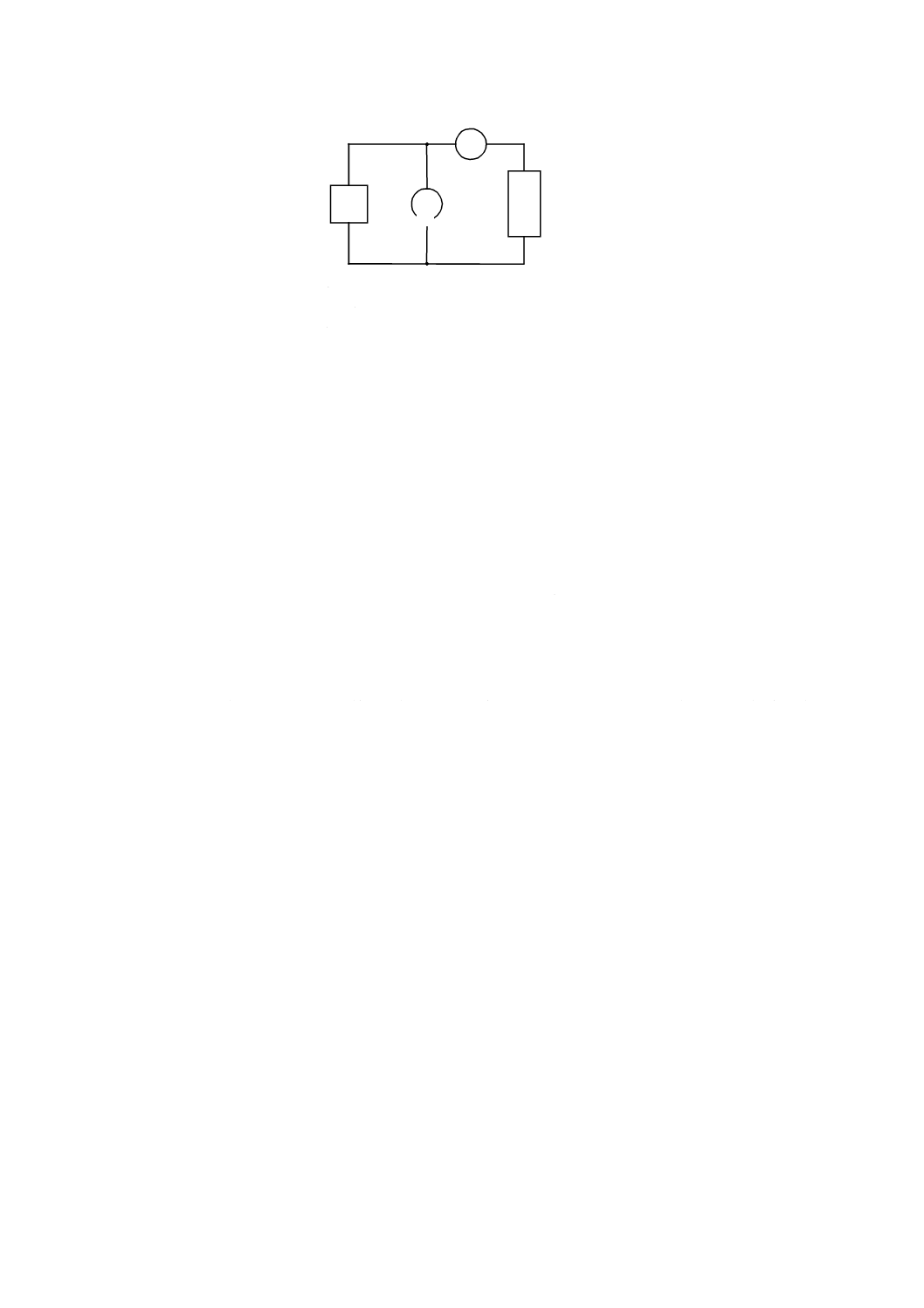

ト端子が電流経路を構成し,ゲート網を通して非隣接主端子に至る(図41参照)。

これらのデバイスを用いる通常の回路は,共通ゲート構成である。防護したIC供給電圧のような外部基

準電圧でゲートをバイアスすることで,防護電圧は基準電圧値になる。

アノードに対して負にゲートバイアスしたPゲートデバイスは,アノードに対して負の過渡電圧防護を

行う。同様にカソードに対して正にゲートバイアスしたNゲートデバイスは,カソードに対して正の過渡

電圧防護を行う。

これらのデバイスは,従来の方法で電流トリガすることもできる。これは,ゲートと隣接電極とを被保

護回線の抵抗で直列接続することによって達成できる場合もある。

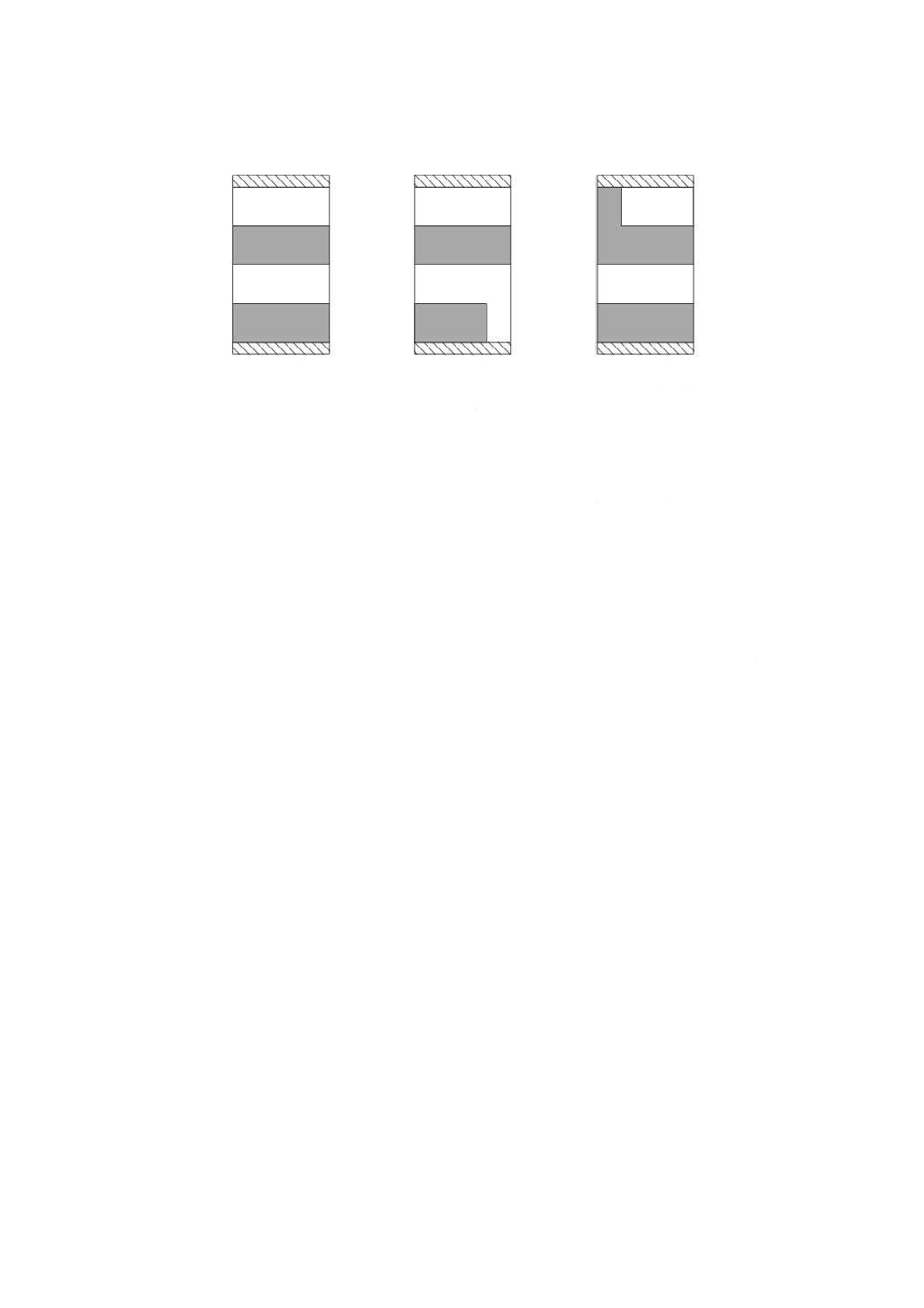

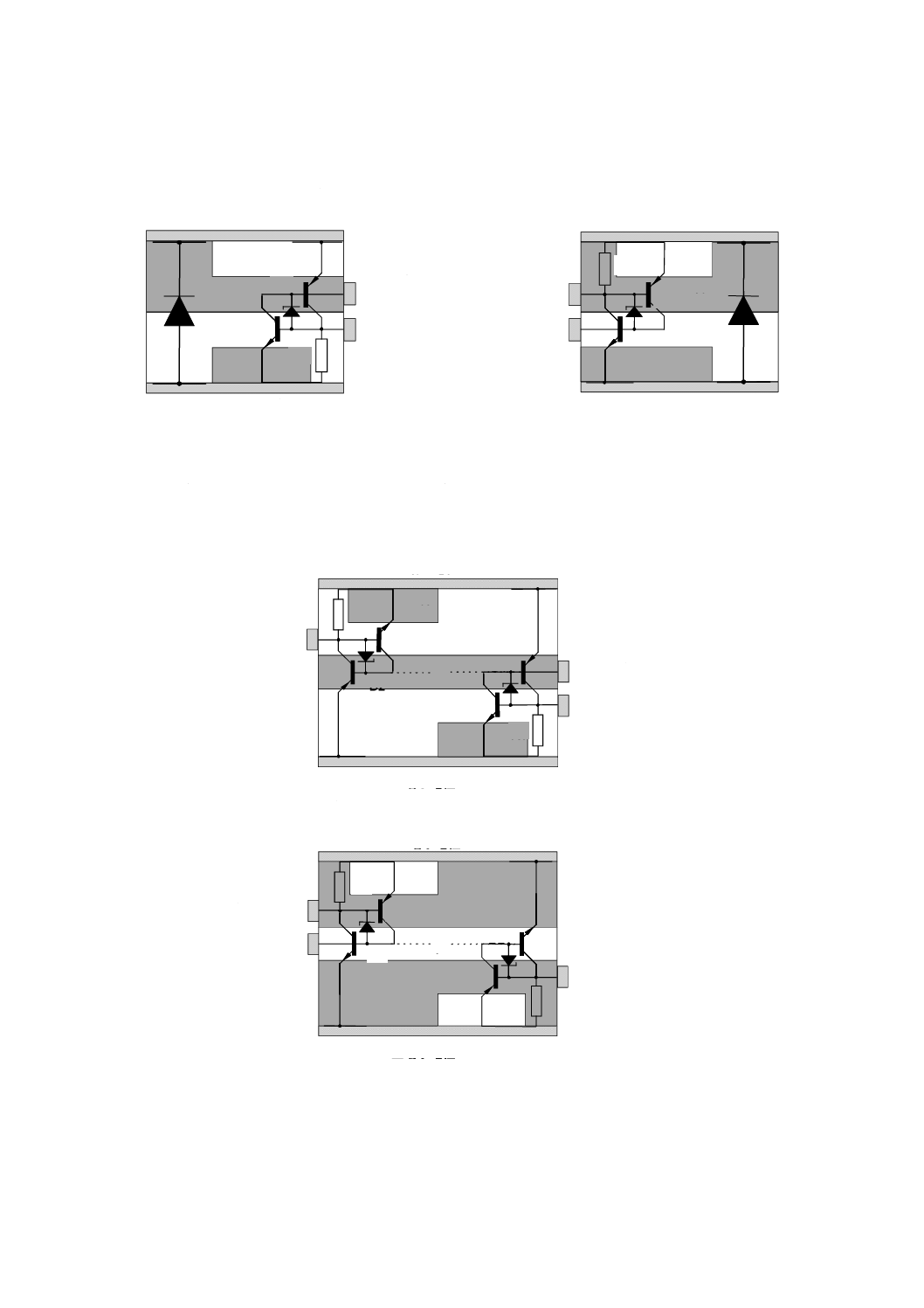

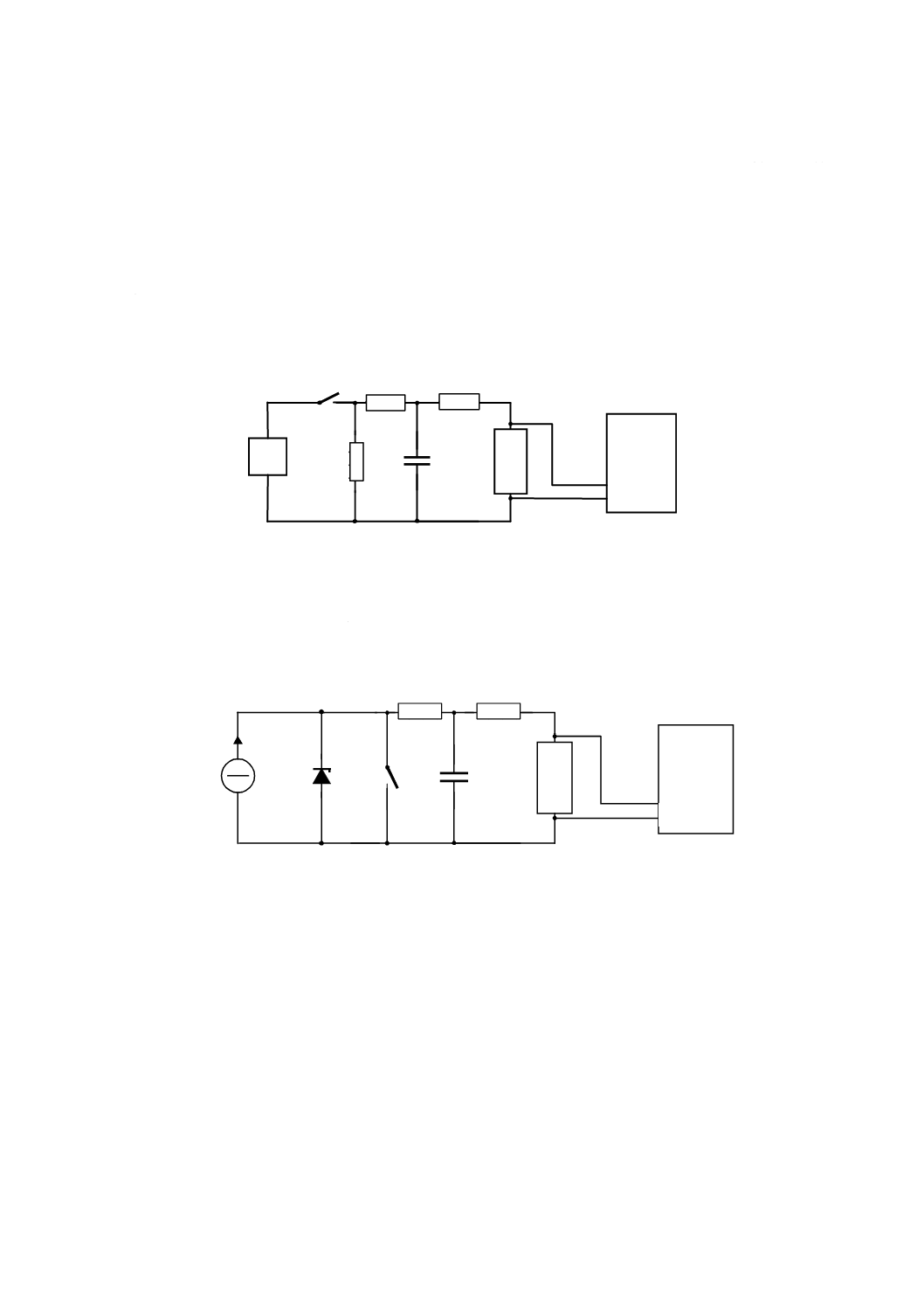

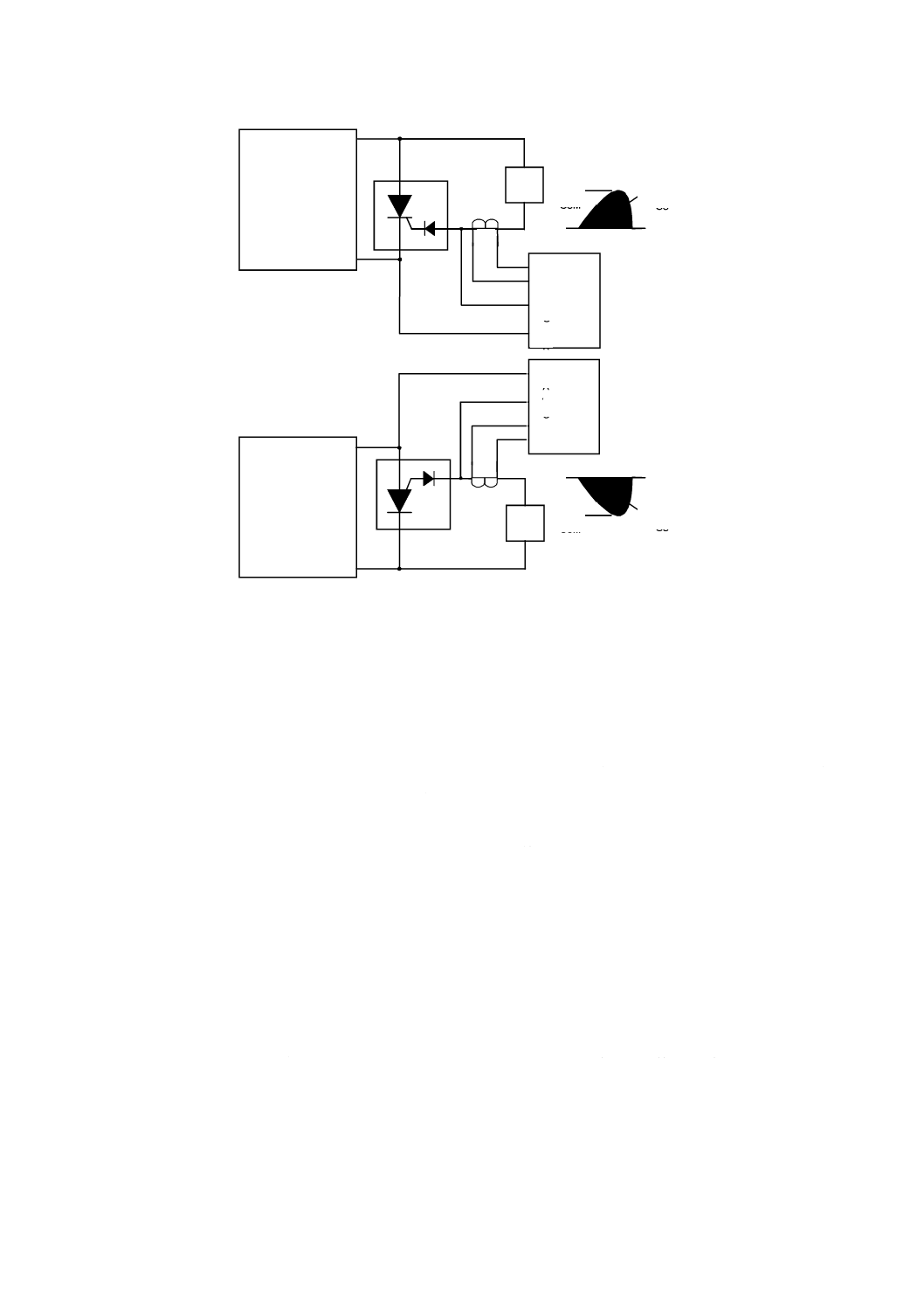

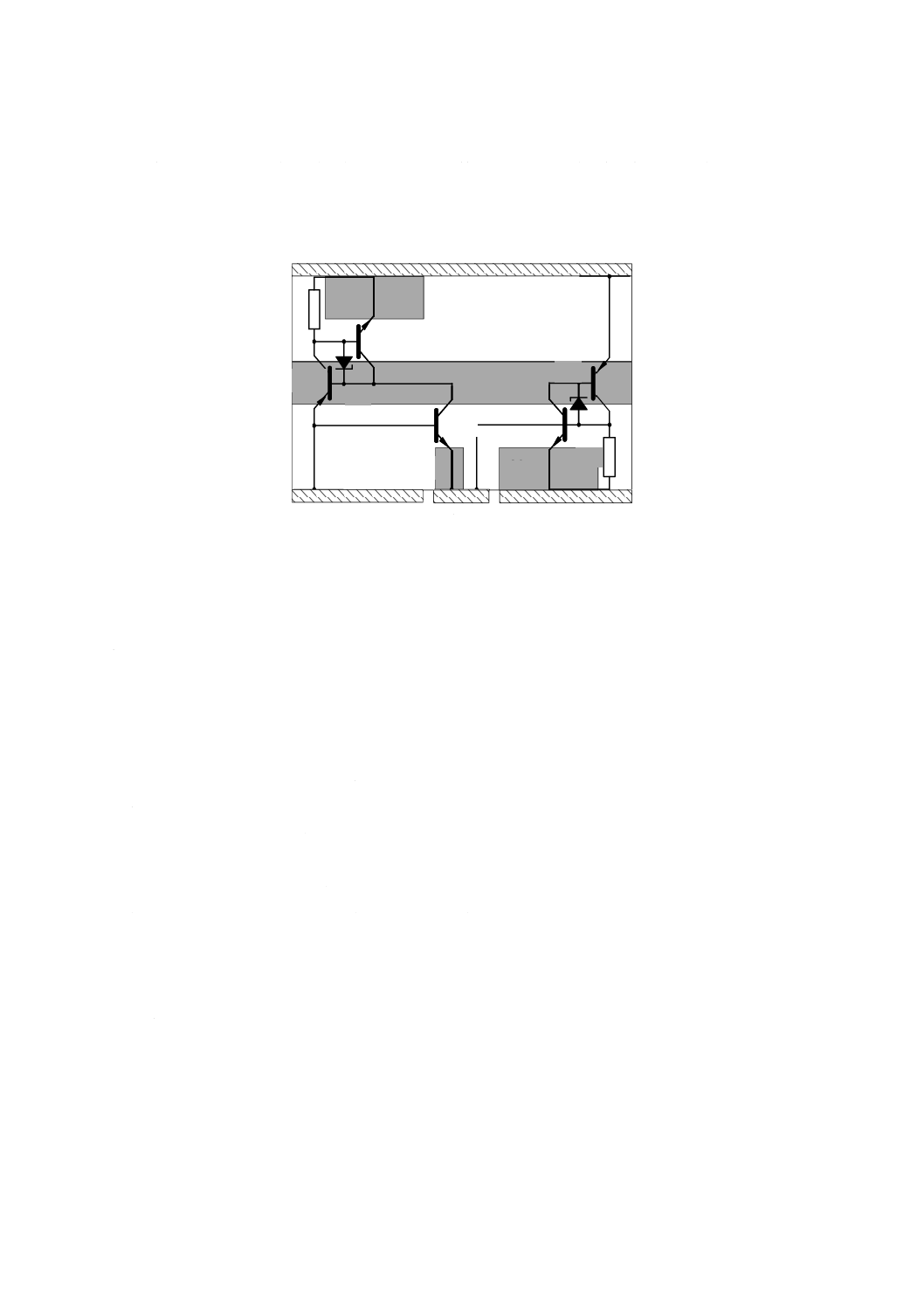

4.6.2

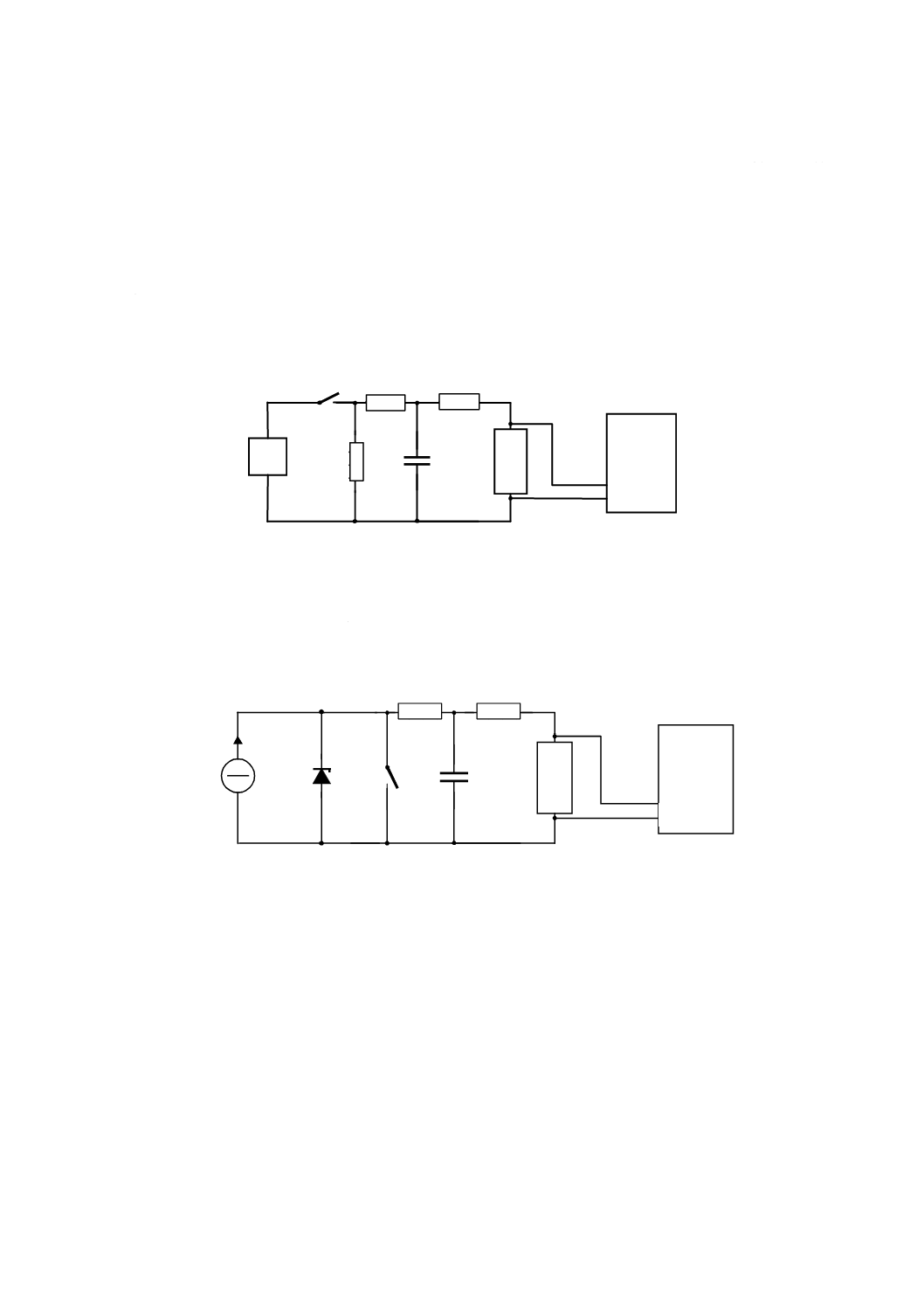

片方向阻止TSS この構造(図6)のスイッチング象限動作についての内容は,4.4に含む。固有

の(一定の)ブレークダウン電圧は,ゲート制御(片方又は両方のゲートを用いること)によって下げる

ことができる。P形短絡TSSの場合は,非スイッチング象限において逆バイアスしたNPアノード接合が

電流を阻止する。N形短絡TSSの場合は,同様にPNカソード接合が電流を阻止する。

a) カソード短絡

b) アノード短絡

アノード

カソード

N形ゲート電極

R1

D1

TR1

TR2

N

N

P

P

TR1

TR2

R1

1

D1

N

N

P

P

P形ゲート電極

N形ゲート電極

アノード

カソード

P形ゲート電極

図 6 片方向阻止TSS

17

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

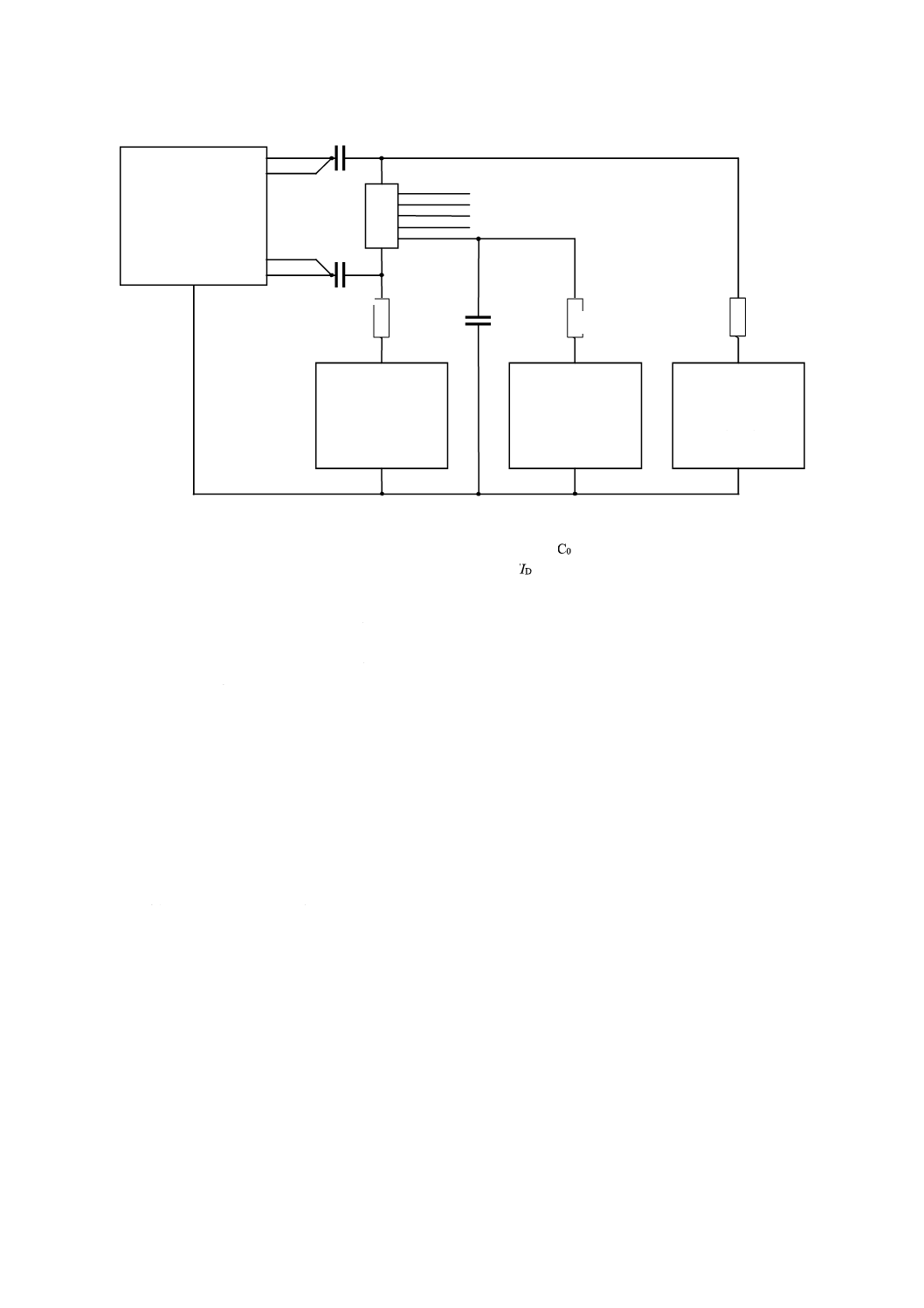

4.6.3

片方向導通TSS この構造(図7)のスイッチング象限動作についての内容は,4.4に含む。固有

の(一定の)ブレークダウン電圧は,ゲート制御(片方又は両方のゲートを用いること)によって下げる

ことができる。非スイッチング象限で,電流は順バイアスPNダイオードを流れる。

a) カソード短絡

P形ゲート電極

サイリスタアノード電極

R1

D1

TR1

TR2

N

N

P

P

D2

TR1

TR2

R1

D1

N

N

P

P

D2

サイリスタカソード電極

P形ゲート電極

N形ゲート電極

サイリスタアノード電極

サイリスタカソード電極

N形ゲート電極

b) アノード短絡

図 7 片方向導通TSS

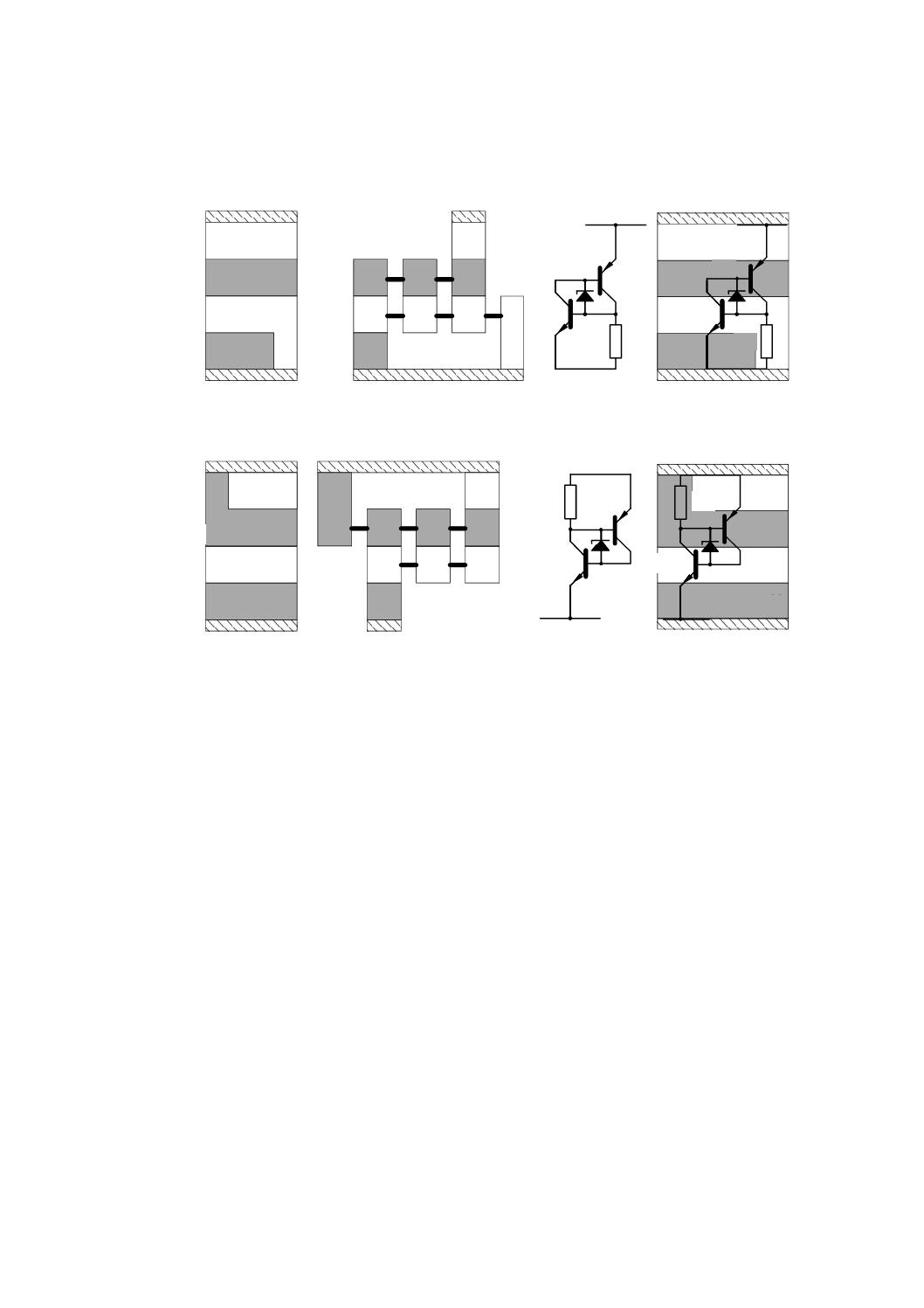

4.6.4

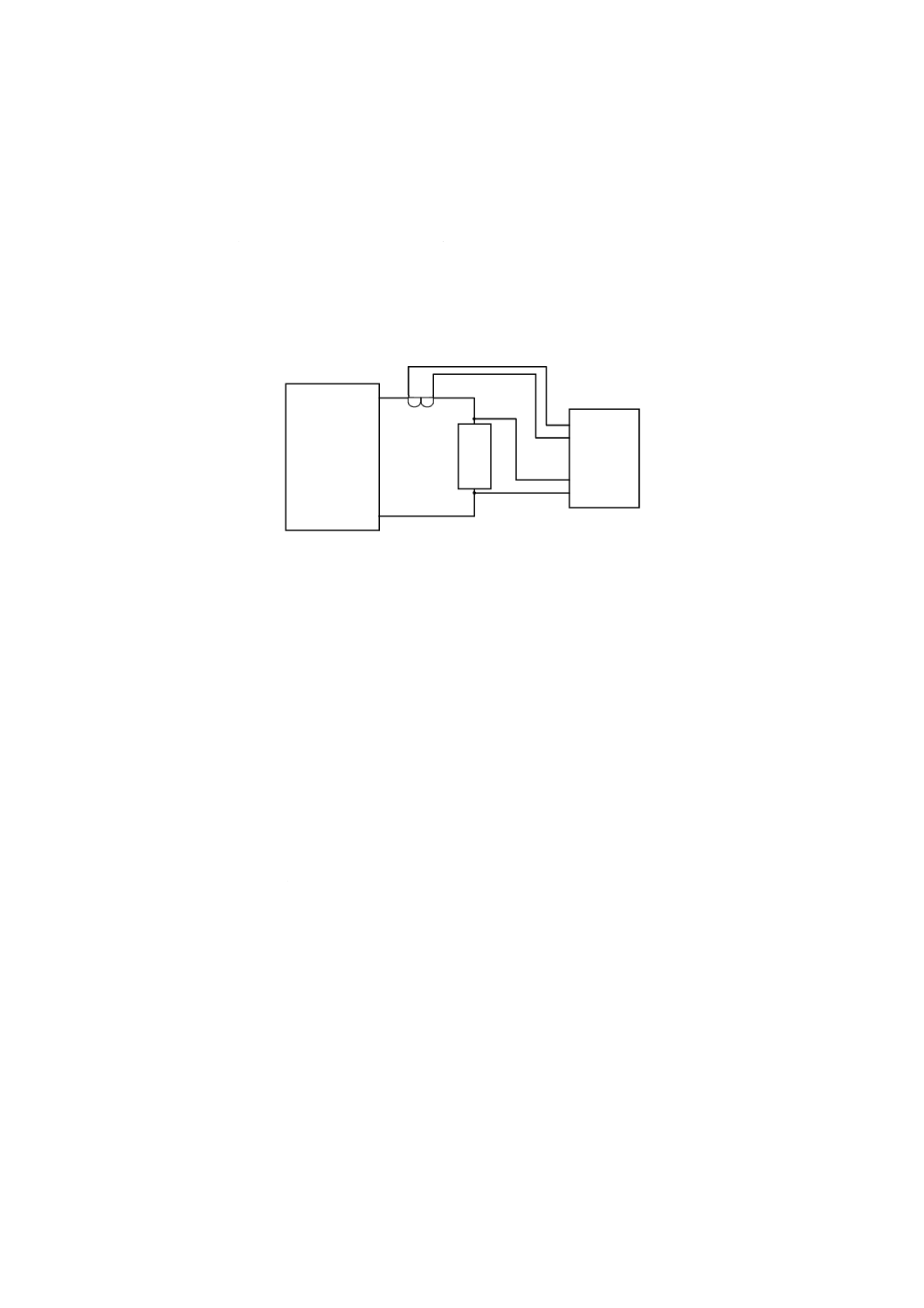

双方向TSS このTSSは,第一及び第三象限でスイッチングするように逆並列に接続した二つの

片方向阻止領域をもつ(図8参照)。それぞれの象限での固有の(一定の)ブレークダウン電圧は,適切な

一つ又は複数のゲートを制御することによって下げることができる。

a) カソード短絡形逆並列サイリスタ

主端子電極2

P形ゲート電極

主端子電極1

N形ゲート電極

P形ゲート電極

R1

D1

TR1

TR2

N

N

P

P

N

R2

D2

TR3

TR4

TR1

TR2

R1

D1

P

N

N

P

P

TR4

TR3

D2

R2

b) アノード短絡形逆並列サイリスタ

主端子電極2

主端子電極1

N形ゲート電極

N形ゲート電極

P形ゲート電極

図 8 双方向TSS

18

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

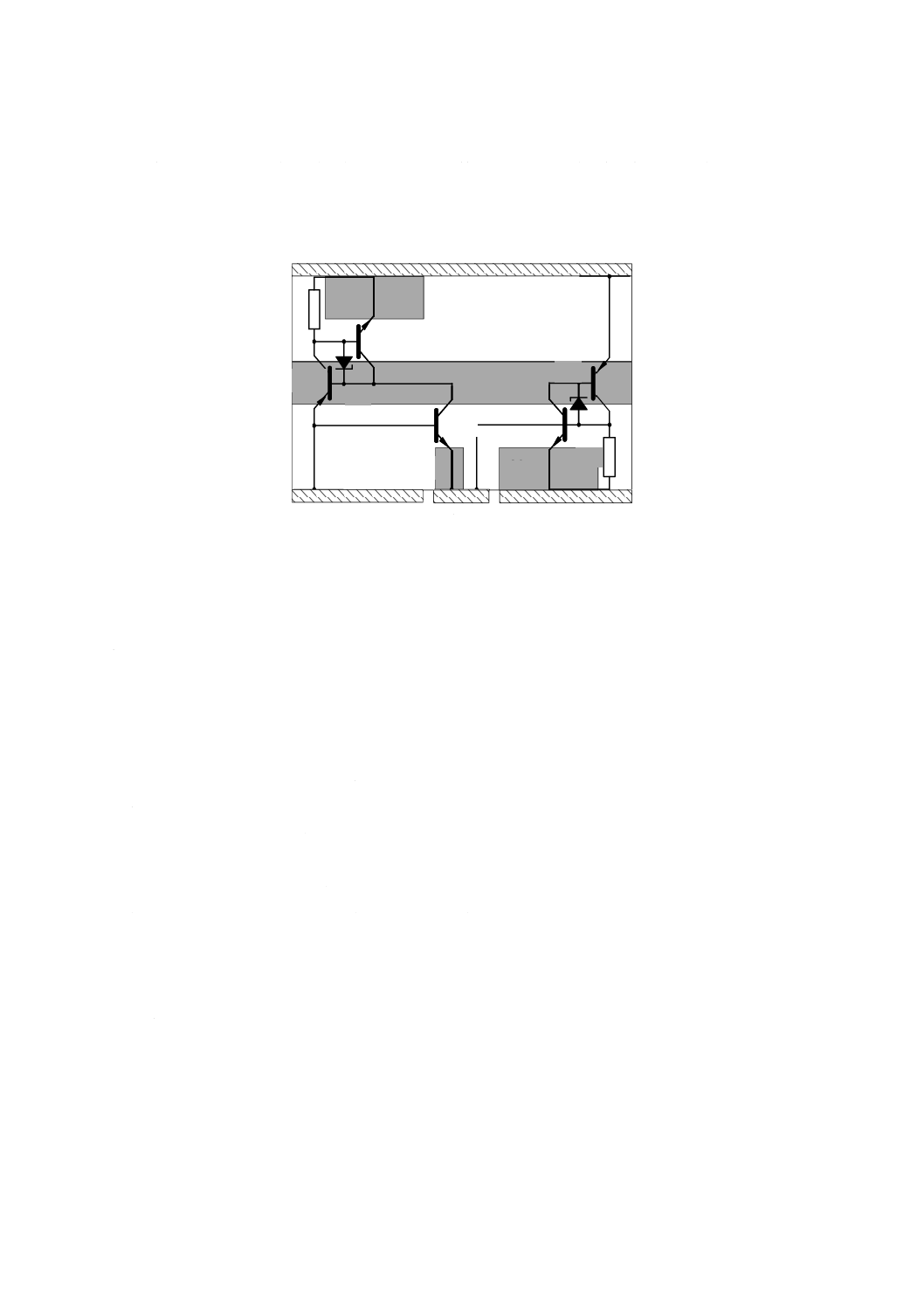

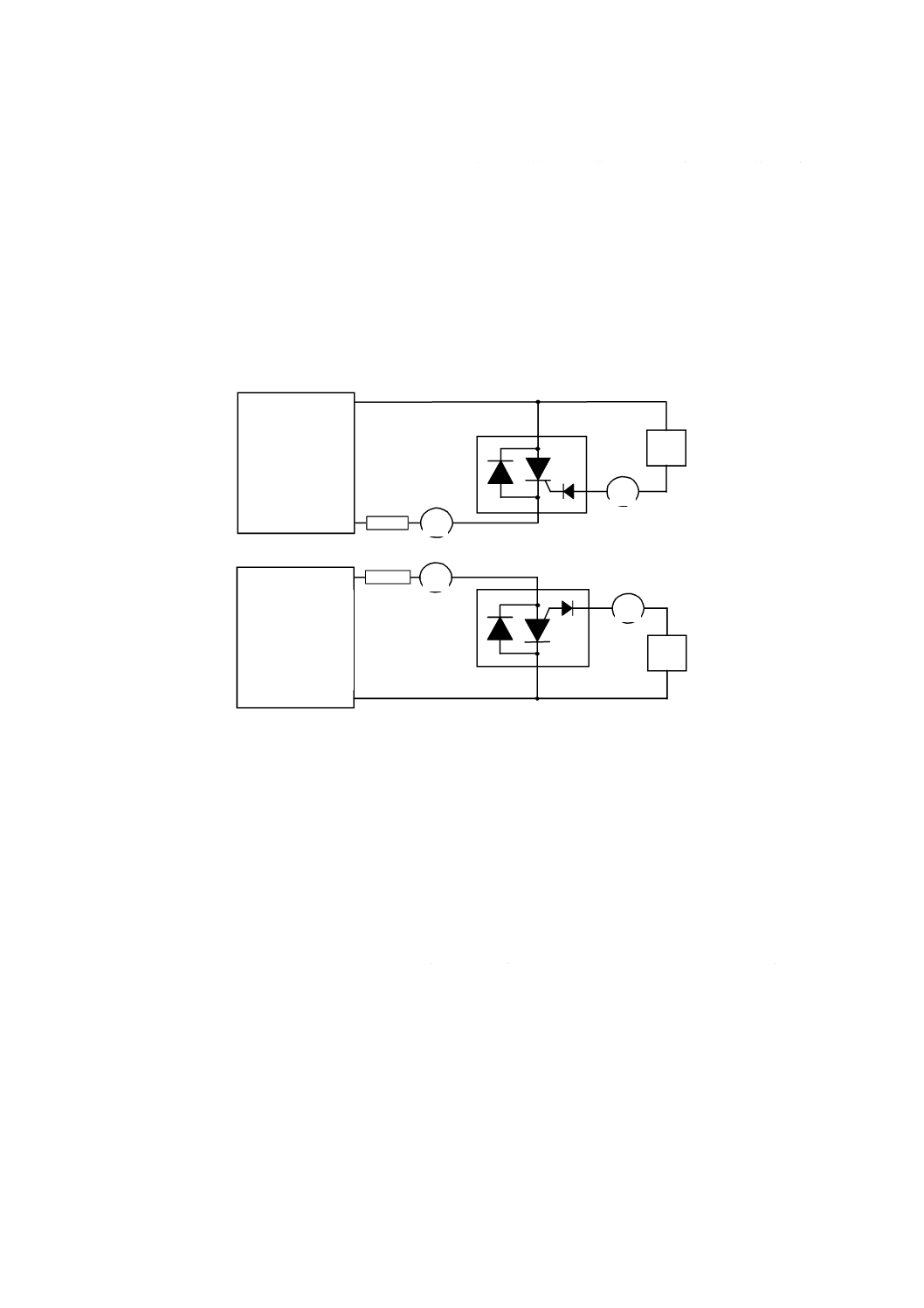

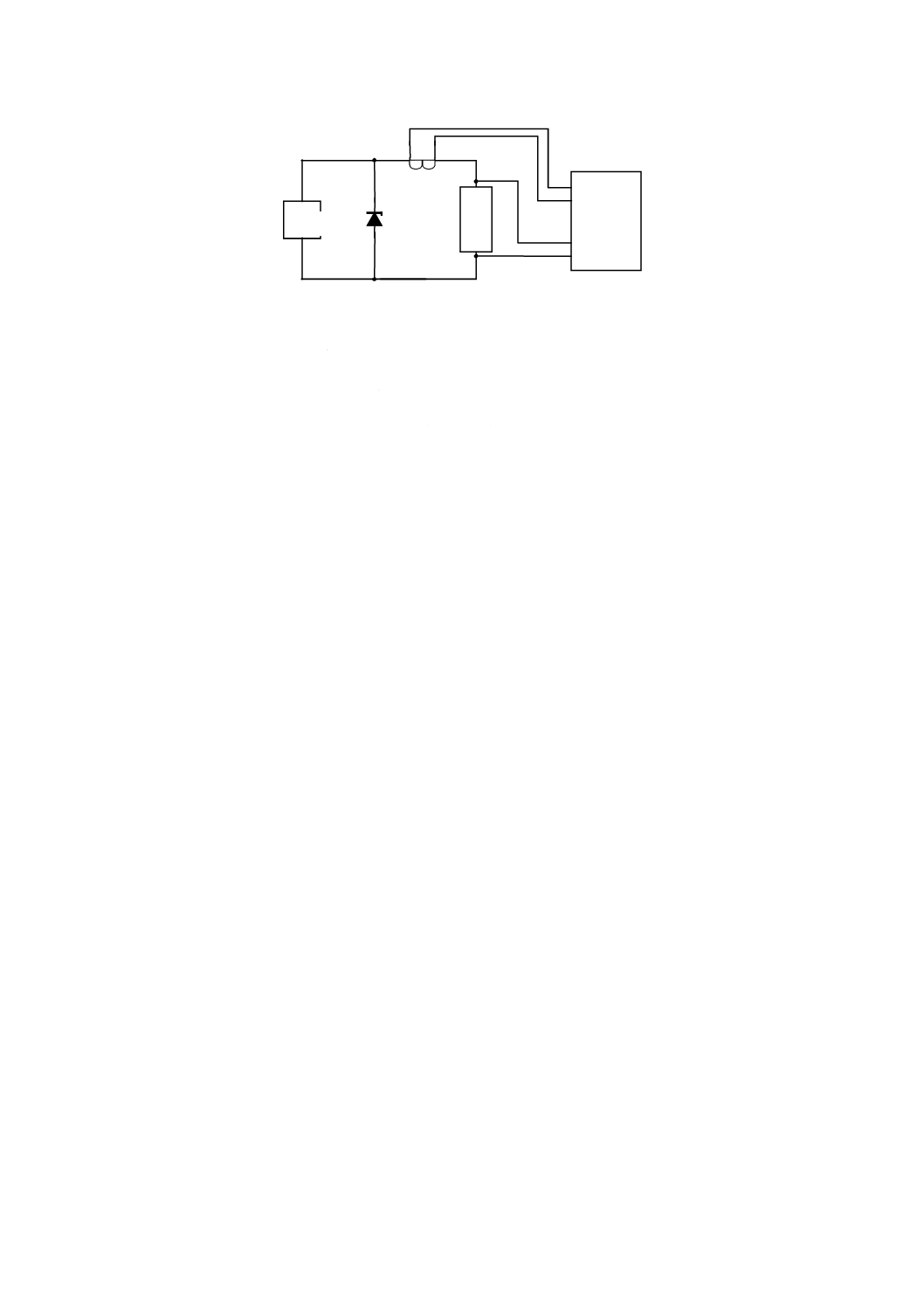

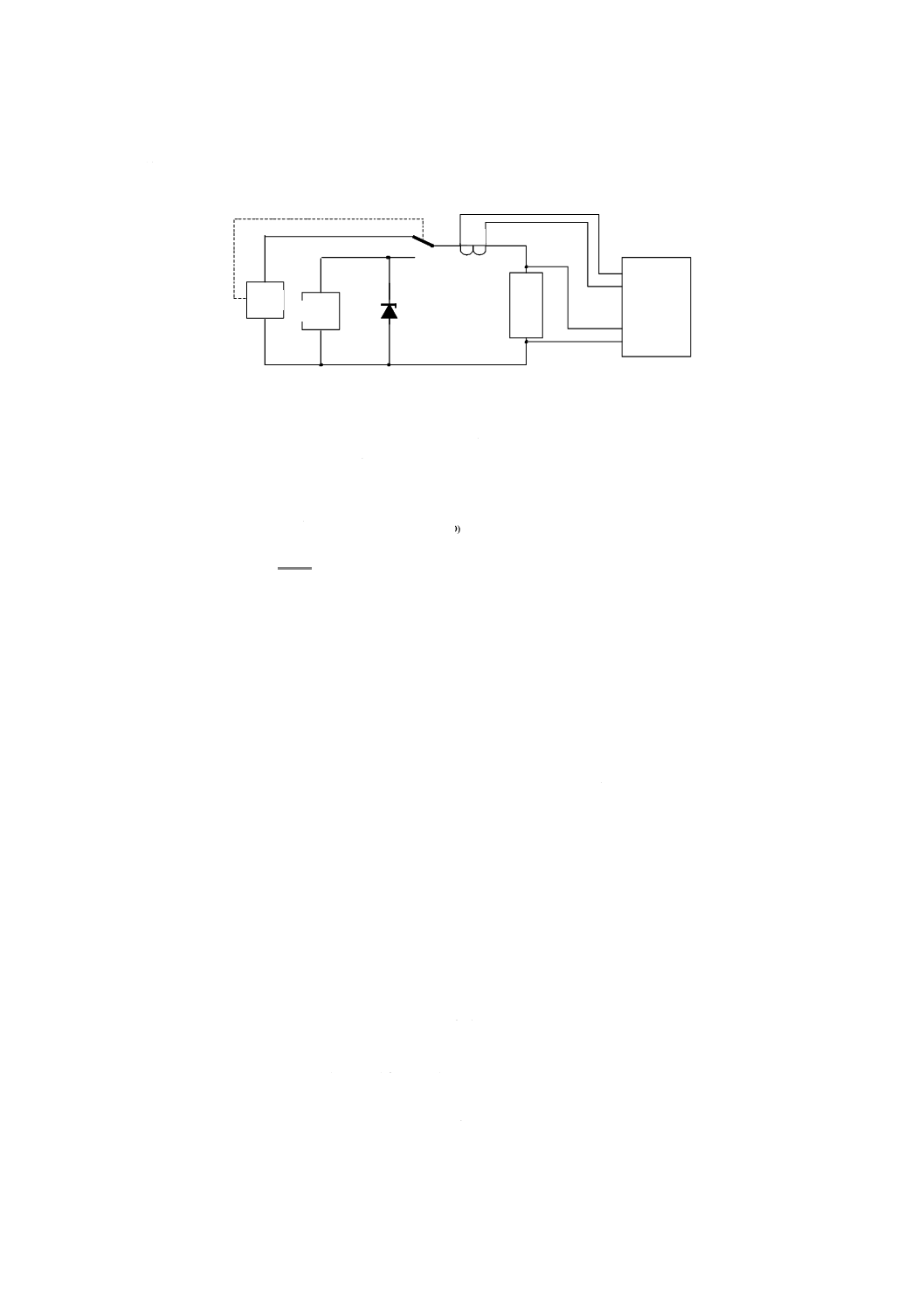

4.6.5

双方向トライアックTSS この双方向TSSは,一つのゲート端子で両象限での制御を可能にする

特殊なゲート構造をもつ(図9参照)。これは,標準的トライアック(交流制御用3端子)構造である。こ

の図は等価回路としては不完全であり,単にゲートトリガが主端子2(MT2)と同じ極性のゲートトリガ

に対応した回路要素を示している。

主端子電極 2

主端子電極 1

R1

D1

TR1

TR2

N

N

P

P

N

R2

D2

TR3

TR4

N

TR5

ゲート

主端子電極 1

図 9 双方向トライアックTSS

5. 標準試験方法

5.1

試験条件 定格及び特性試験は,TSS適用上での要求又はデバイス仕様の細目に従い実施しなけれ

ばならない。TSSは,温度範囲及び実装形態などを規定した環境条件で試験を行わなければならない。

5.1.1

標準大気状態 IEC 60749の1.4で規定するとおり,測定後の回復も含むすべての室温での電気的

測定は,次の条件で行わなければならない。

− 温度:

25±5 ℃

− 相対湿度:

45〜75 %の適切な値

− 気圧:

86〜106 kPa(860〜1 060 mbar)

判定試験は,次の標準大気条件で行わなければならない(IEC60749の1.4参照)。

− 温度:

25±1 ℃

− 相対湿度:

48〜52 %

− 気圧:

86〜106 kPa(860〜1 060 mbar)

TSSパラメータをある温度範囲で試験する場合,試験温度はIEC60747-1の4.5の温度リストの中から適

切な値を選択することが望ましい。現在,これらの値以外としては−40 ℃及び35 ℃を推奨する。

特に規定がない限り,次に推奨する半導体周囲温度範囲のいずれかを使用する。

− 標準:

0〜70 ℃

− 拡張:

−40〜85 ℃

19

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.1.2

測定誤差 接地ループ,共通インピーダンス,磁気誘導,電気誘導及び電磁放射は,測定誤差を引

き起こす。ループインピーダンスの増加は,循環する接地ループ電流が引き起こす電圧誤差を低減できる。

通常,これはプローブケーブルのクリッピングフェライトコアで行う。供試品への電力供給及び測定系を

ケルビン接続することで共有インピーダンスを回避することができる。リード長を短くして配線ループ面

積を最小化すること及び可能な限り,より線を用いることによって,磁気誘導及び電気的誘導の影響を低

減することができる。非信号接地に接続したファラデーシールドを挿入することによって,電気誘導(容

量性ノイズ)を取り除くことができる。シールド及び磁気誘導を用いた技術は,電磁ノイズを低減するこ

とができる。

5.1.3

測定精度 アナログオシロスコープは,信号立ち上がり時間に比べて5倍以上速い立ち上がり時間

をもっていなければならない。これは,表示した立ち上がり時間で2 %未満の誤差を保証する。

デジタルオシロスコープ(IEC 61083-1参照)は,少なくとも30/Tx(Txは測定間隔)のサンプリング

レイトをもっていなければならない。インパルスパラメータを評価する試験には,定格分解能がフルスケ

ールの0.4 %(2-8のフルスケール偏差)以内の偏差のものが望ましい。記録の比較を要求する判定試験に

は,定格分解能がフルスケールの0.2 %(2-9のフルスケール偏差)以内の偏差のものを用いなければなら

ない。

5.1.4

インパルス形状及び値の表記 インパルス波形は,二つの数字の組合せによって表記する。第一は

規約立ち上がり時間(T1),第二は波尾の値の半値となる規約時間(T2)を表す。マイクロ秒単位でT1/T2

と表記する。“/”記号は,数学的意味をもたない(IEC 60099-4の2.15参照)。

TSSの定格電流は,試験機の短絡時の値を用いる。試験条件下で実際のデバイス電流は,デバイス特性

と試験機との相互作用によって異なる。

5.1.5

多端子TSS 同一パッケージした多端子TSSは,用途によってそれらが同時に動作してもよい。

個々のTSSパラメータが他のTSSの動作によって大きな影響を受けるとき,その際の試験は単体TSSの

動作と同じようにみなせる条件で行わなければならない。

5.1.6

ゲート付きTSS試験 定電圧TSSのすべての試験は,防護端子性能を検証し,決定するためにゲ

ート付きTSSに対して行わなければならない。ゲート付きTSSは,ゲートバイアス電圧VGG及びネットワ

ークの適切な値で試験しなければならない。特に規定がない限り,試験に使うゲートバイアス電圧は,意

図した用途での最大値及び最小値にしなければならない。ゲート付きTSSが電圧を制限する試験では,ゲ

ート供給電源は,低インピーダンス(分離した)にしなければならない。内部ゲート阻止のないTSSは,

ゲート端子に,ゲート端子と直列に極性を合わせて阻止ダイオードを付けなければならない。ゲート付き

TSSがゲート制御及び定電圧防護を与えるように設計してある場合,定電圧TSS試験は,ゲート開回路で

行わなければならない(すなわちIG=0)。

5.2

使用条件

5.2.1

標準使用条件 TSSは通常,機器又はモジュールの内部に実装するので,内部環境条件を適用する

(JIS C 0120参照)。この規格を満足するTSSは,屋内の固定した使用に適したものでなければならない

(JIS C 0116参照)。特に規定がない限り,TSSは次に示す共通使用条件及び二つの環境条件のうち一つ又

は二つの条件下での動作に適合しなければならない。

a) 標準環境条件

1) 周囲温度:0〜70 ℃

2) 気圧:86〜106 kPa

3) 相対湿度:20〜75 %

20

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

b) 拡張環境条件

1) 周囲温度:−40〜85 ℃

2) 気圧:70〜106 kPa

3) 相対湿度:10〜95 %

c) 共通使用条件

1) TSS定格電圧以下での最大システム信号レベル

2) TSS定格電流以下での最悪想定値

3) 他の過電圧及び過電流保護部品とのTSS協調動作

4) 適用の前提事項として,TSSは製造業者の推奨する取扱い組立及び実装を行う。

5.2.2

特殊な使用条件 通常の用途又は使用条件以外に適用するTSSは,設計,製造又は用途について

特別な考慮をしてもよい。特殊な使用条件でこの規格を使用する場合,製造業者と購入者との間で同意を

必要とする。起こり得る特殊な使用条件項目の一覧を附属書Aに示す。

5.3

故障及び不良モード デバイス故障は,要求した機能を果たすデバイス能力がなくなる現象である。

故障後にデバイスは不良となる。不良モードは,付与した要求機能に対して想定できるデバイスの不良状

態の一つである(IEV 191-05-22参照)。

特に規定がない限り,次の判定基準を勧める。不良状態の判定試験は,デバイス温度が25±5 ℃に回復

後に行われなければならない。

5.3.1

劣化故障 これは,初期に特性を満たすTSSが段階的及び部分的な故障となる現象である。TSS

は,ある特性において明確な変化を示す。デバイスは,ある適用回路において十分に機能する場合もある。

段階的な故障(又は不安定故障とも呼ぶ。)は,デバイスの付与特性の経時変化に依存する。部分的な故障

は,デバイスにすべてではないが,ある種の要求機能を果たすことができなくなる原因となる。

備考 この故障は,すべての機能を失うわけではないが,ある機能を損う。やがてその故障が壊滅的

なものになる場合もある。劣化に弱い主な特性項目は,逆阻止特性及びオフ電流特性である。

段階的故障は,事前試験又はモニタリングによって予期でき,予防保全によって回避できる場

合もある。

5.3.2

オフ電流増加不良モード このモードにおいて,TSSのオフ電流は,規定値よりも大きくなる。

備考 特殊な用途に関する規定がない場合,オフ電流は,ピーク繰返しオフ電圧値の印加条件で測定

することが望ましい。

5.3.3

逆電流増加不良モード このモードにおいて,TSSの繰返しピーク逆電流は,規定値よりも大きく

なる。

5.3.4

ブレークオーバ電圧増加不良モード このモードにおいて,TSSのブレークオーバ電圧は,規定値

よりも高くなる。

5.3.5

保持電流減少不良モード このモードにおいて,TSSの保持電流は,規定値よりも小さくなる。

5.3.6

壊滅的故障 これは,TSSが突発的及び完全な故障となる現象である。完全な故障は,デバイスの

全要求機能を完全に不能にする原因となる。突発的な故障は,事前試験又はモニタリングによる予測が不

可能な事象である。壊滅的故障は,TSSの全基本機能の停止を引き起こす。

備考 この故障は,一般的に主端子間の電気的短絡となる。しかし,その結果の短絡電流が非常に大

きい場合,デバイス内部部品は溶融し,デバイスを溶かし開回路となることもある。

5.3.7

短絡回路不良モード このモードにおいて,TSSは恒久的に短絡回路となる。

備考 特殊な用途に関する規定がない限り,短絡回路のインピーダンスの最大値は,通常的に被防護

21

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

機器を防護できる値から決定する。

5.3.8

開回路不良モード このモードにおいて,TSSは恒久的に開回路となる。

参考 特殊な用途に関する規定がない限り,このモードで故障デバイスに最大ブレークオーバ電圧の

150 %を印加した場合,流れる電流が規定のピーク繰返しオフ電流値以下であることが望まし

い。

5.3.9

致命的故障 これは,人間への危害,重大な物的損害又は他の許容できない重大事の原因になると

判断される故障である。

備考 非致命的故障は,人間への危害,重大な物的損害又は他の許容できない重大事の原因とはなら

ないと判断される故障である。

5.3.10 フェールセーフ これは,その故障が結果的に致命的不良になることを防止する設計事項である。

TSSの故障及び不良モードを示す“フェールセーフ”の利用は,次の理由で不適切である。デバイスの故

障は,前記のモードのいずれでも設定できる。ある使用者は,装置の防護機能を維持するための最も望ま

しい不良モードとして,例えば短絡回路不良モードをフェールセーフと考える。しかし,別の使用者は,

システムにとってデバイスの開回路不良モードが望ましいと要求する場合もある。

このように,短絡回路不良モードにおける故障は,多くの使用者がフェールセーフとみなす一方,別の

使用者が望むフェールセーフとは反対であるかもしれない。したがって,前述で定義した不良モードのう

ち,いずれによる故障かを示すことが望ましい。

5.4

定格試験手順 使用する過電圧及び過電流の試験レベルは,2.のIEC及びITU-T規格を引用しなけ

ればならない。

これらの試験レベルは,試験回路に装置機器のサージ協調部品を含めることによって,最終の装置機器

レベルに変更してもよい。

5.4.1

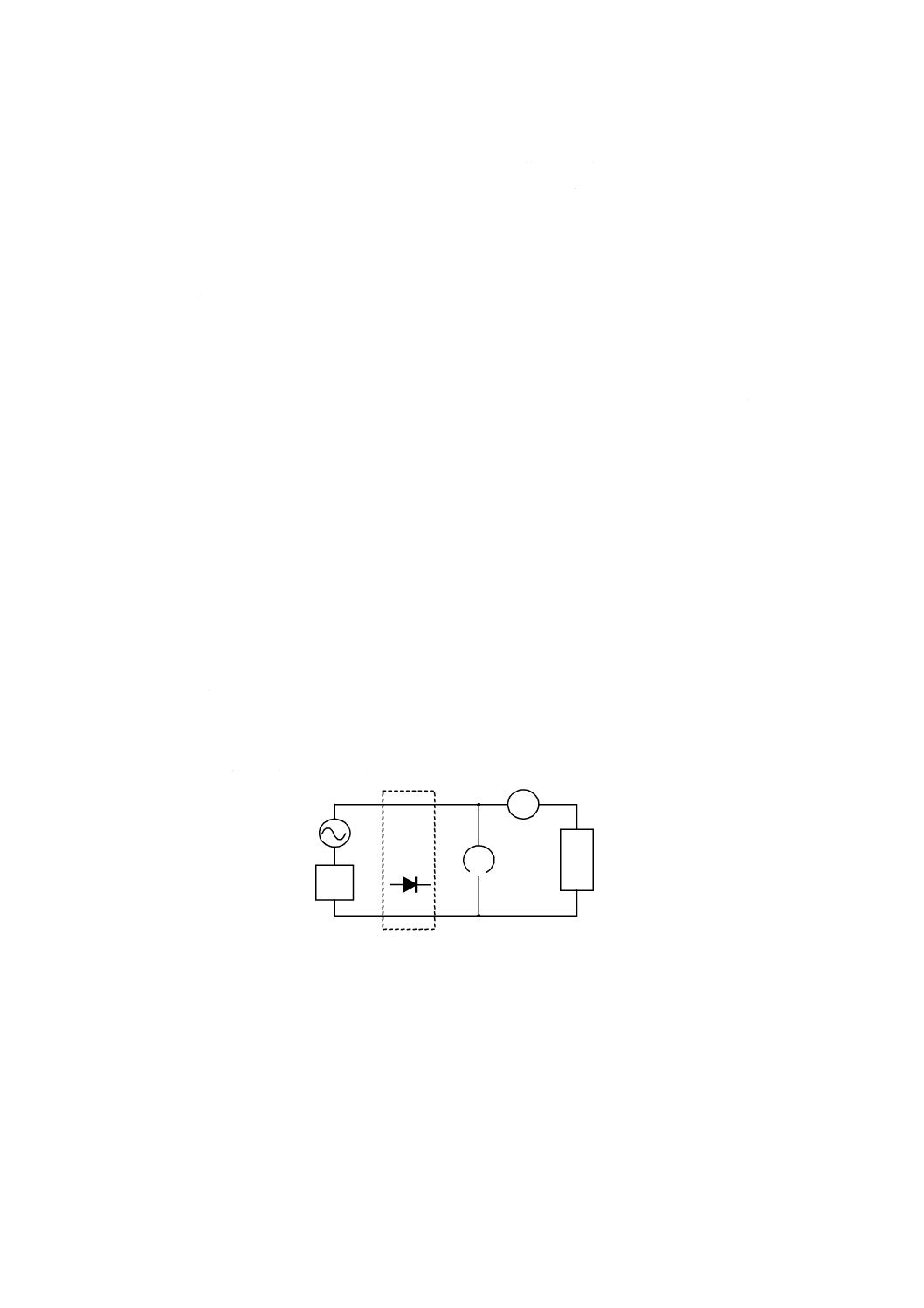

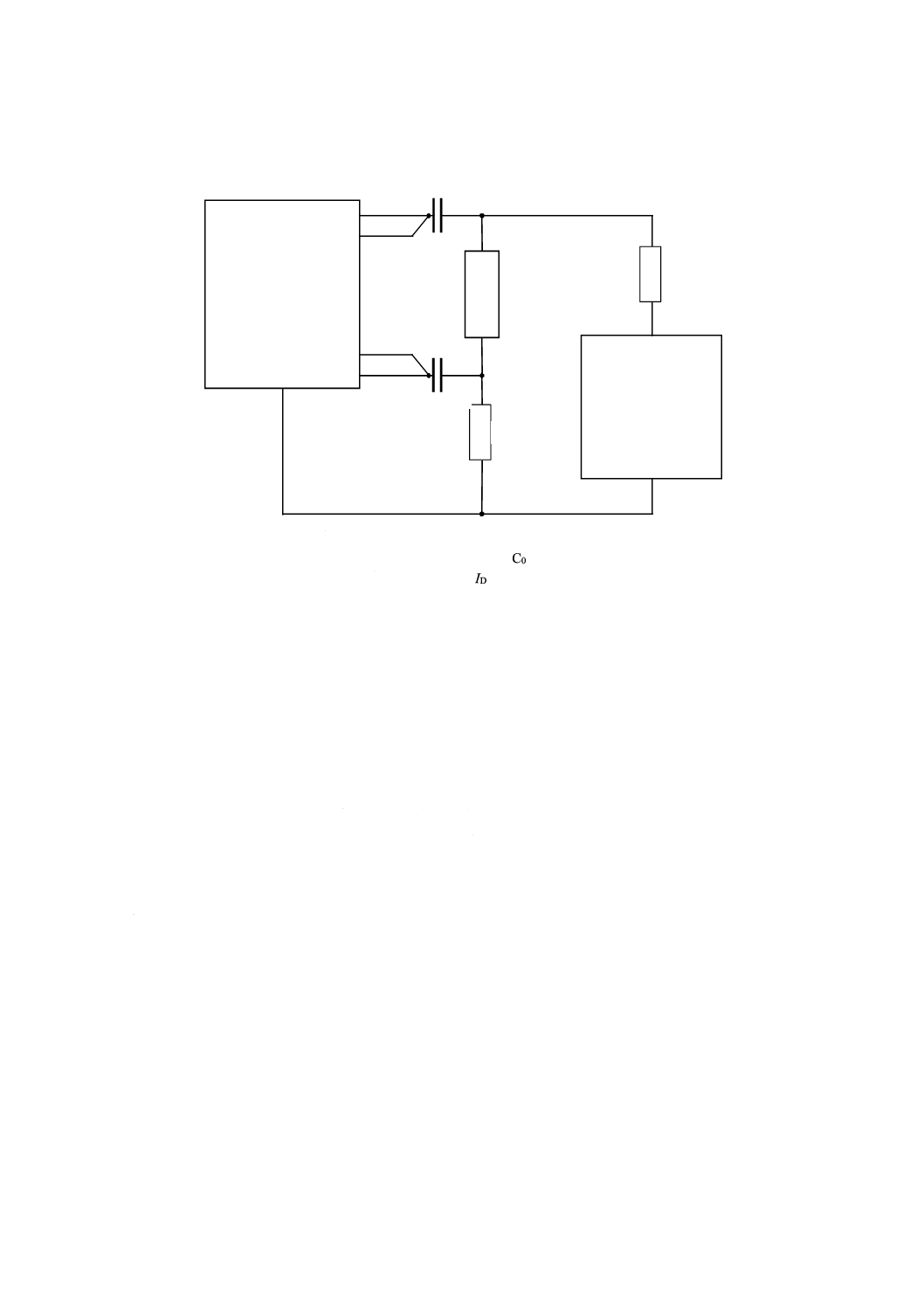

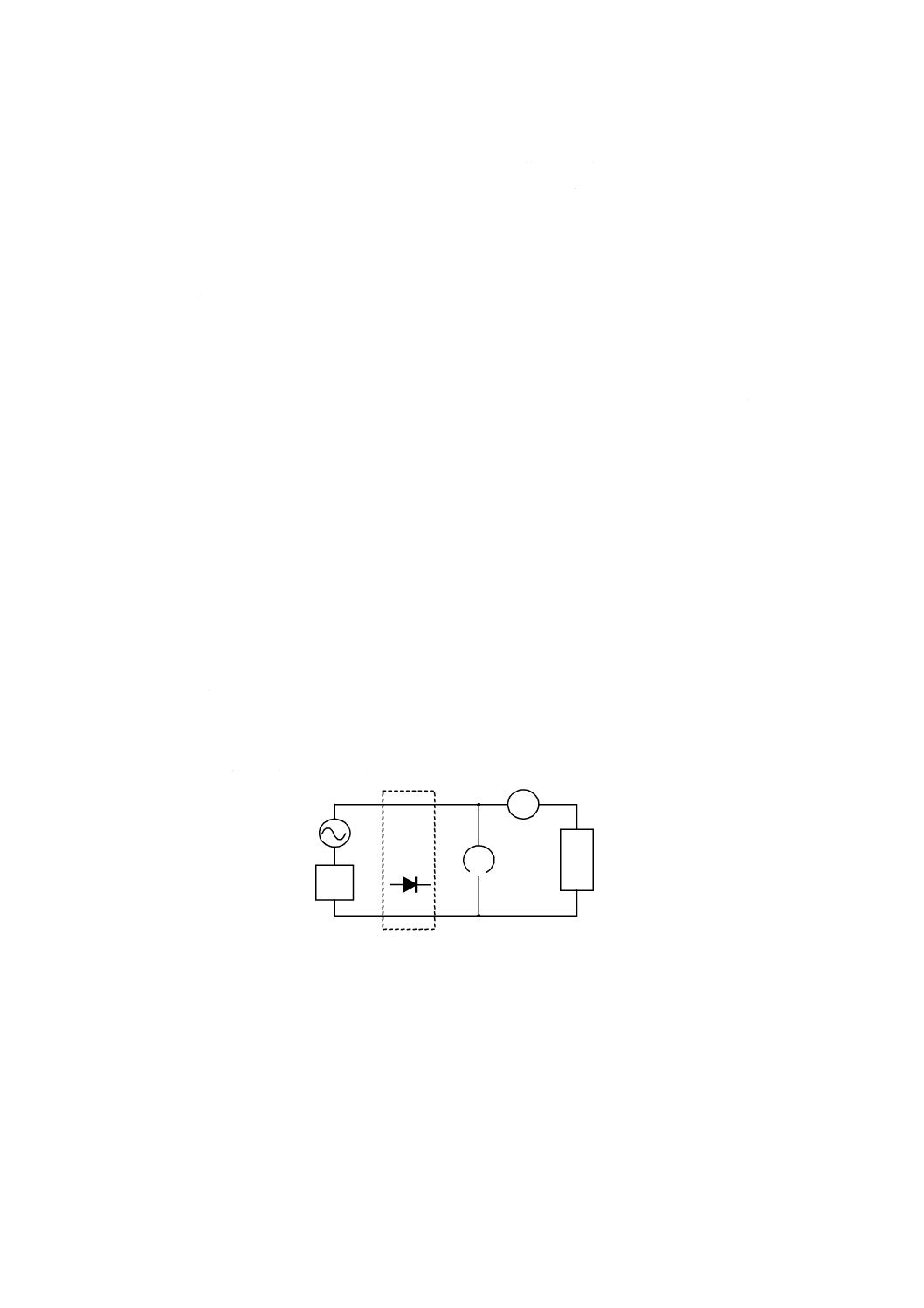

繰返しピークオフ電圧VDRM この試験の目的は,繰返しピークオフ電圧を連続的に印加したとき,

TSSが高インピーダンスオフ状態を維持することを検証することである。主端子間に繰返しピークオフ電

圧VDRMの定格値を印加し,繰返しピークオフ電流IDRMの定格値を測定しなければならない。使用する回

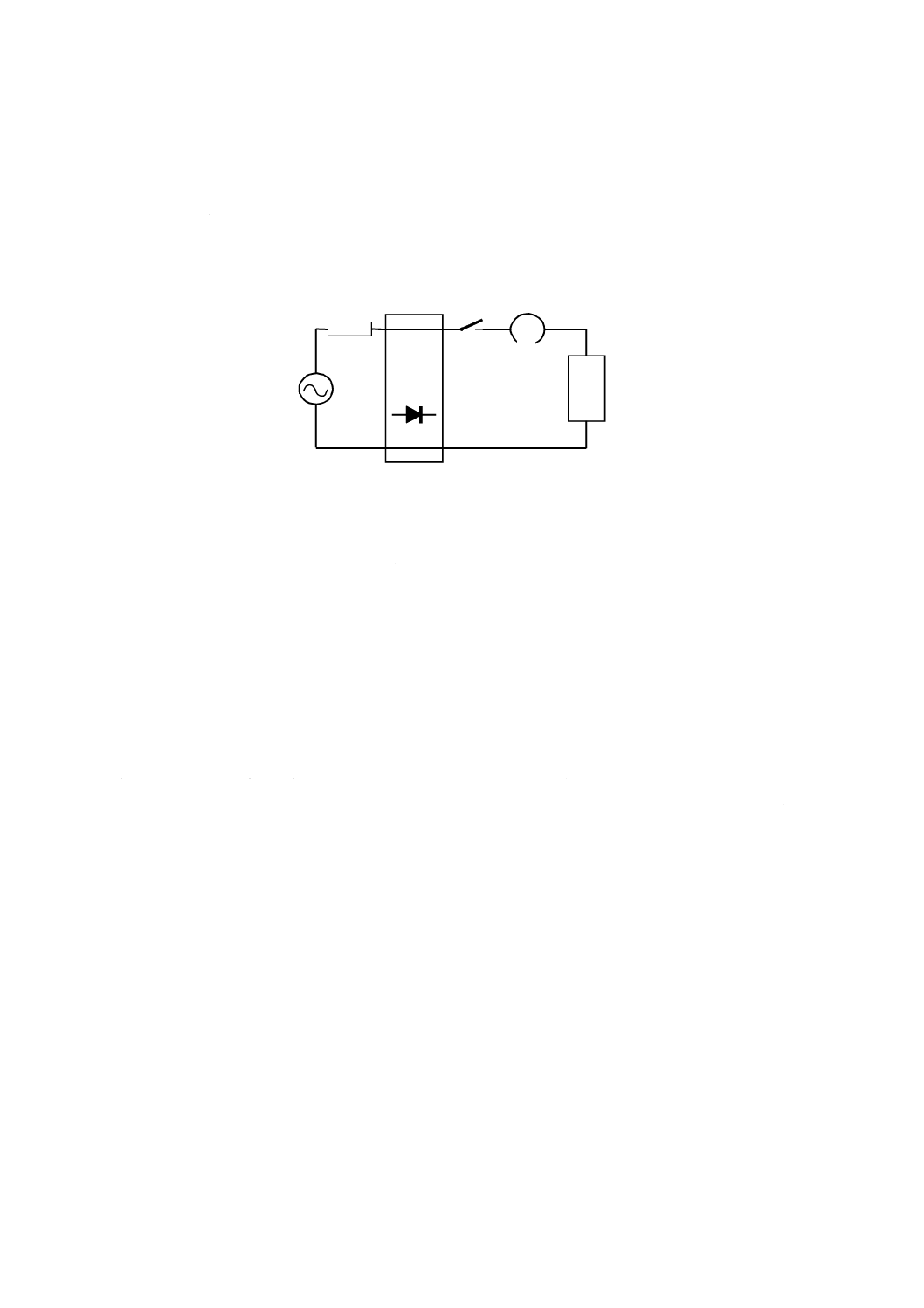

路は,図10と機能的に等価でなければならない。

DUT

V

A

PS2

REC

PS1

DUT

A

V

PS1

PS2

REC

:供試品

:ピーク電流計

:交流電圧計(平均,ピーク及び実効値)

:直流部品のVDRMに設定する直流電源

:交流部品のVDRMに設定する交流電源

:VDRM逆極性の交流部品のときの片方向試験に

使用する全波又は半波整流回路

:

図 10 繰返しピークオフ電圧VDRM検証用試験回路

測定した電流は,IDRMの最大規定値を超えてはならない。VDRMの試験後,デバイスはいかなる特性値に

ついても規格値を外れてはならない。測定持続時間は,デバイスに期待される信頼性を確立するために十

22

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

分となるようにしなければならない。試験及び測定は,TSSの各スイッチング象限ごとに分けて行わなけ

ればならない(試験前後で大きく変化する特性値については,デバイス劣化の兆候の可能性がある。)。試

験による故障については,5.3の規定に沿って分類しなければならない。

5.4.2

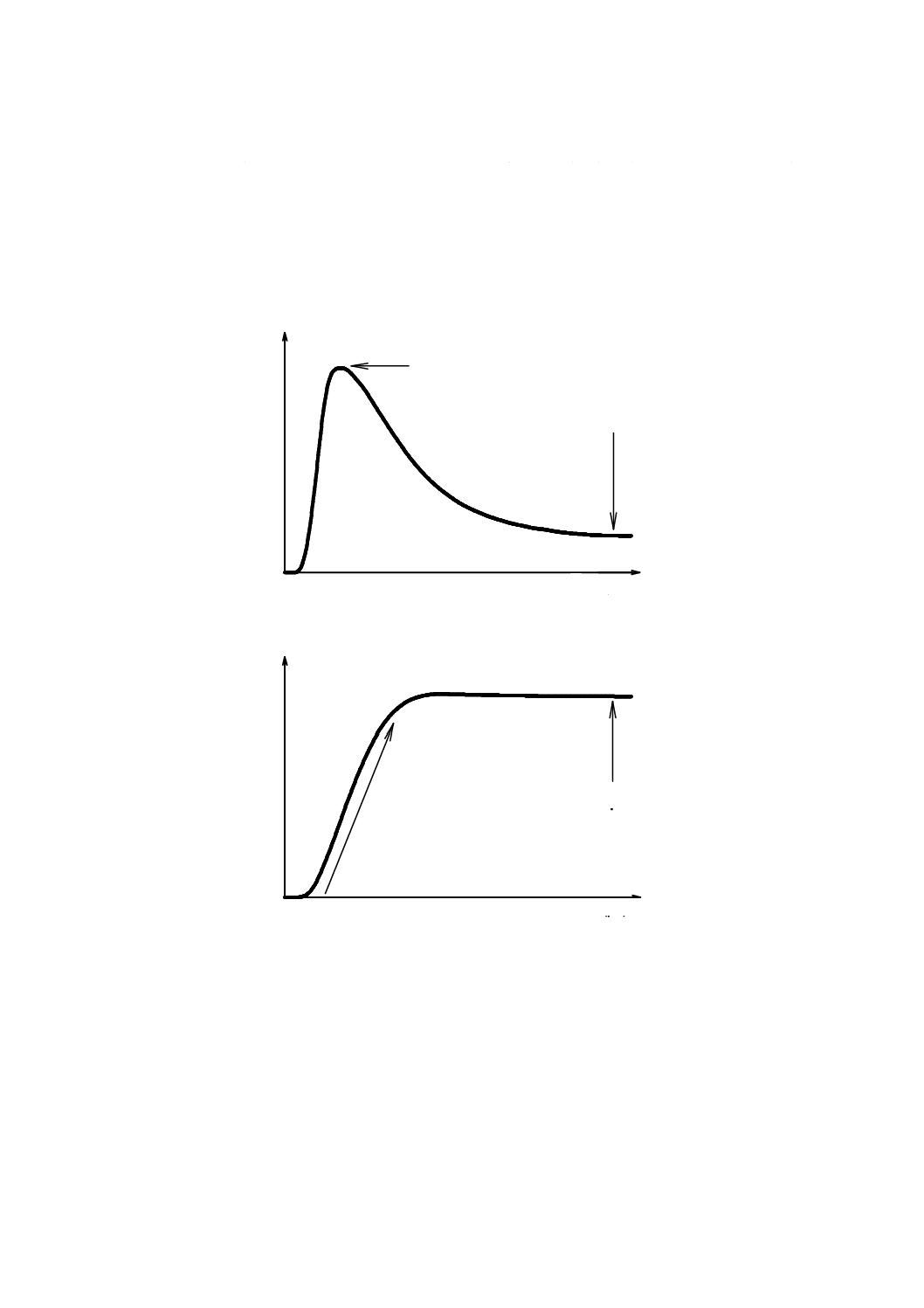

繰返しピークオン電流,ITRM この試験の目的は,TSSが故障することなく又は最大定格接合温度

を超えることなく,定格ピークオン電流(準正弦波)を連続的に流すことができることを検証することで

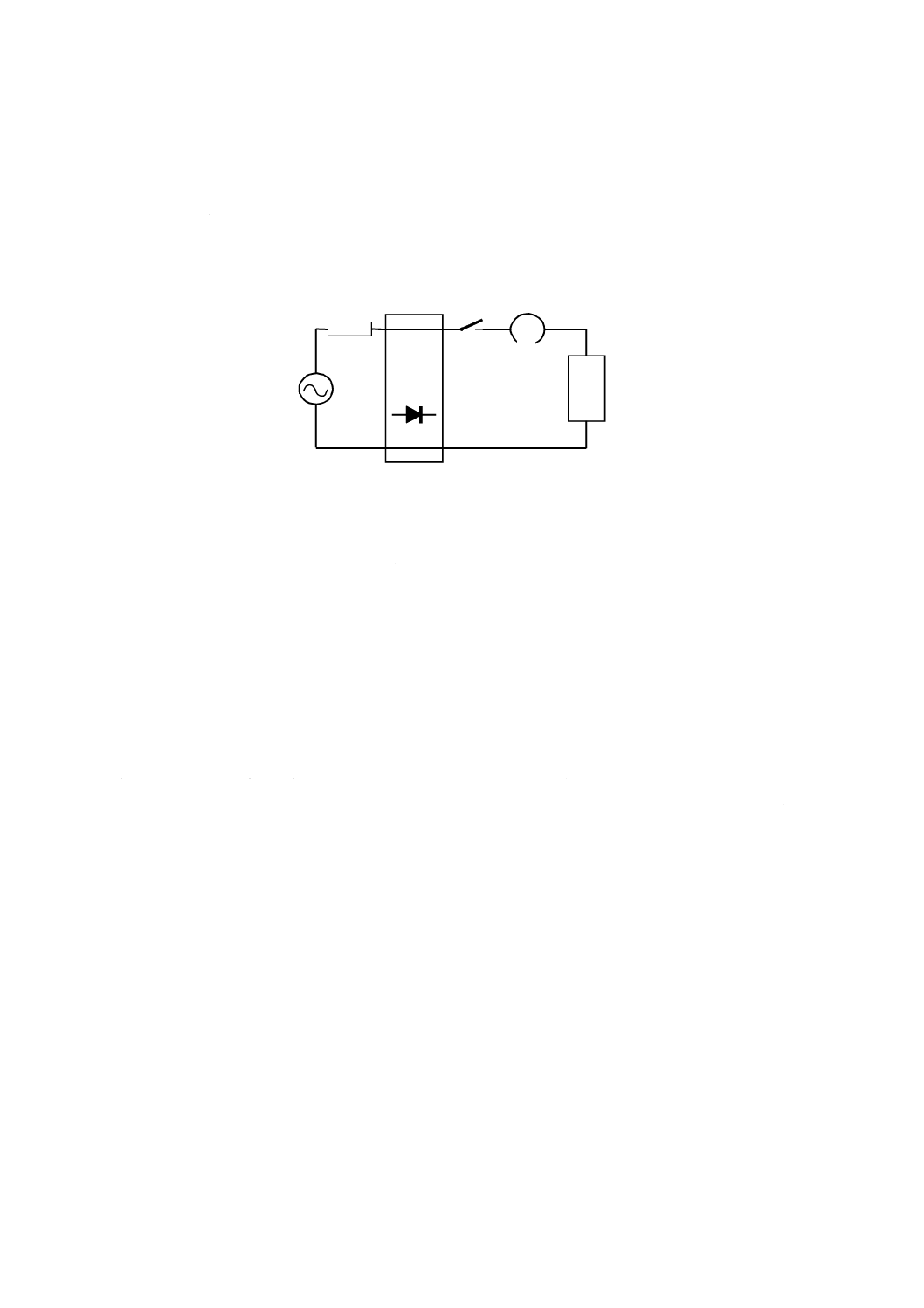

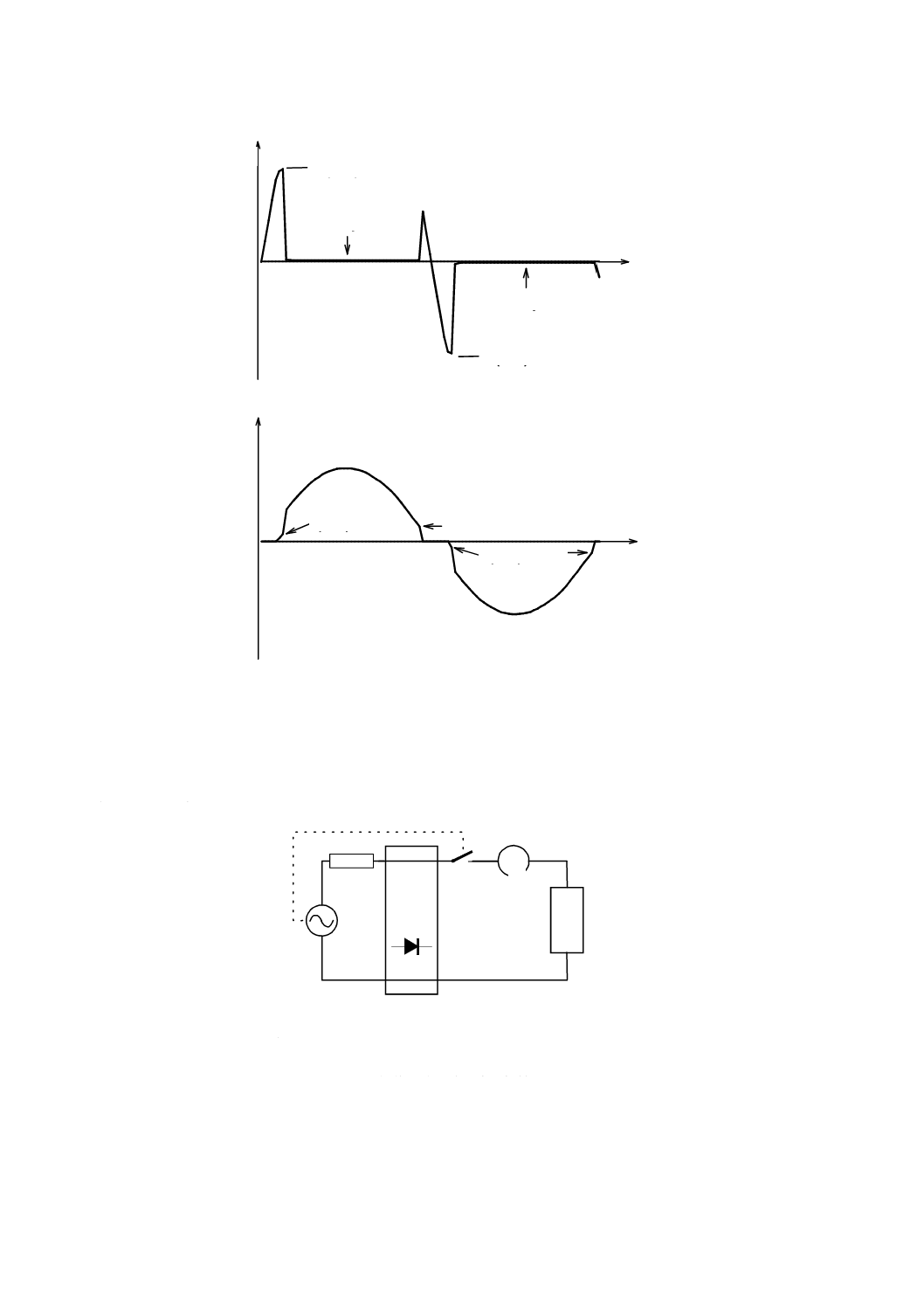

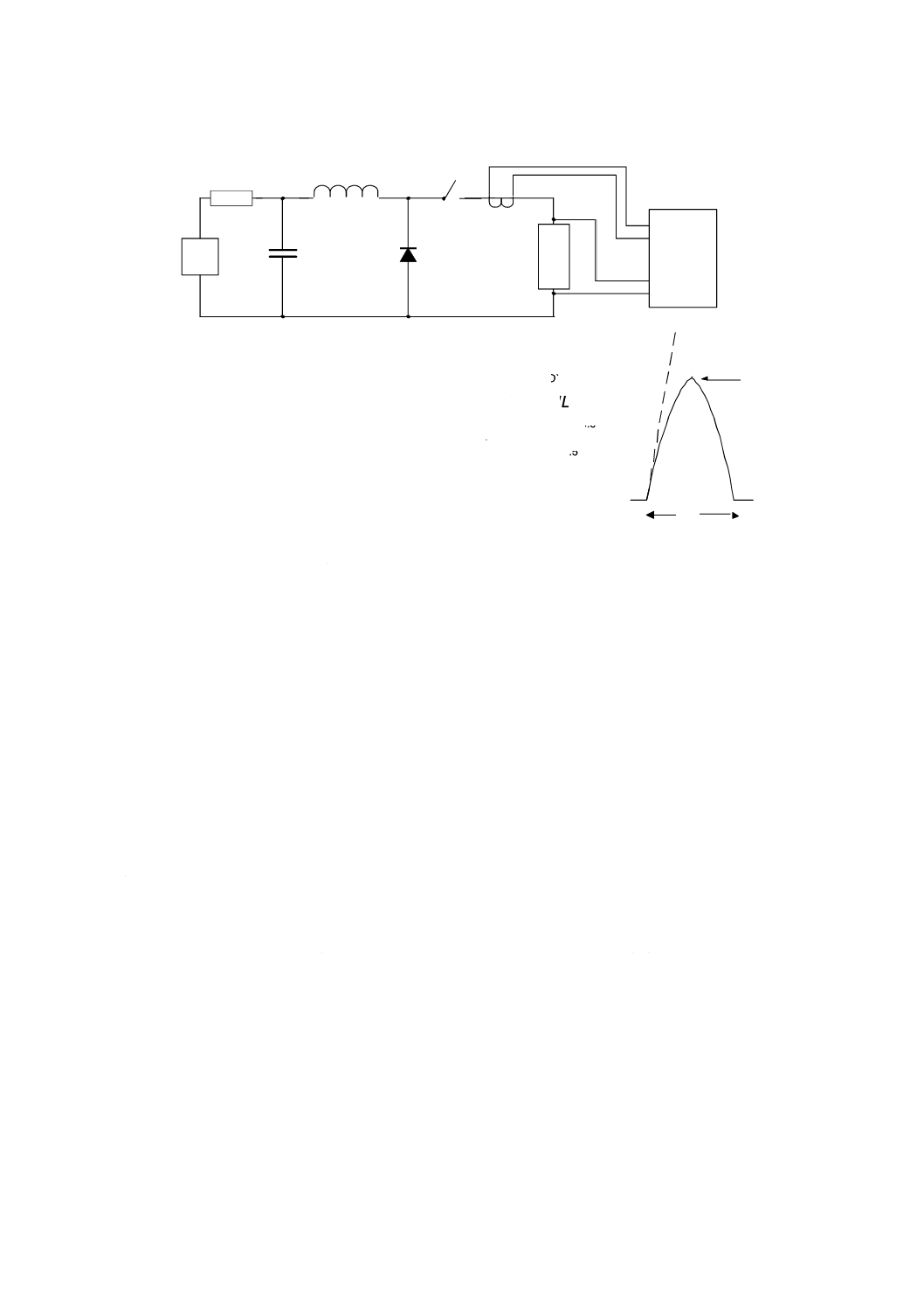

ある(図12参照)。使用する回路は図11と機能的に等価でなければならない。

DUT

S1

REC

R1

PS

A

DUT

A

PS

R1

S1

REC

:供試品

:ピーク電流計

:規定の電圧に設定する交流電源

:ピーク短絡回路電流設定用抵抗

:スイッチ

:片方向試験時に接続する全波又は半波整流回路

図 11 繰返しピークオン電流ITRM検証用試験回路

交流試験機の開回路電圧及び短絡回路電流値,又はこれと同等な波形,波形ピーク値を規定しなければ

ならない。試験機は,確実にTSSをオン状態にスイッチする能力がなければならない。双方向電流動作を

評価しない片方向TSSには,全波又は半波試験をするためにブリッジ又は半波整流器を交流電源に加える

ことが必要である。ITRM試験の間,IHのような温度に敏感なデバイスパラメータは,図15で示すように,

電流及び電圧プローブを供試品に接続したオシロスコープによって観測できる。

平均動作接合温度は,測定したパラメータ値,パラメータ温度係数及び供試品の初期温度から計算でき

る。ITRMの試験後,熱平衡状態に復帰したデバイスは,いかなる特性値についても規格値を外れてはなら

ない。測定持続時間は,デバイスに期待される信頼性を確立するために十分となるようにしなければなら

ない(試験前後で大きく変化する特性値については,デバイス劣化の兆候の可能性がある。)。試験による

故障については,5.3の基準に沿って分類しなければならない。

23

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

V(BO)

V(BO)

VT

VT

v

t (ms)

i

t (ms)

IH

I(BO)

IH

I(BO)

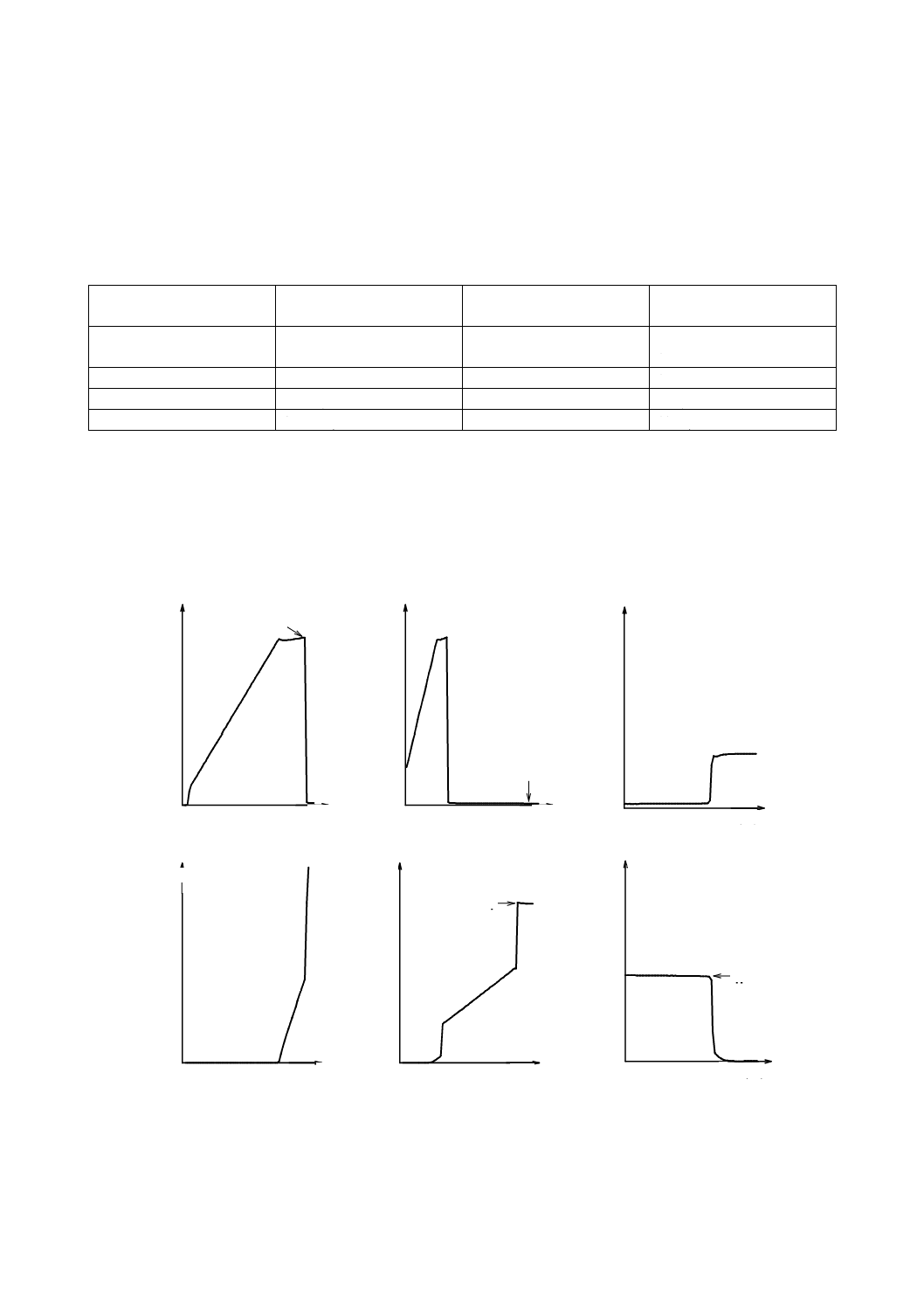

図 12 繰返しピークオン電流波形

5.4.3

非繰返しピークオン電流,ITSM この試験の目的は,TSSが故障することなく規定継続時間の(正

弦波に準じる)交流サージ電流に耐えることを検証することである。使用する回路は,図13と機能的に等

価でなければならない。

PS

DUT

A

S1

REC

R1

DUT

A

PS

R1

S1

REC

:供試品

:ピーク電流計

:規定の電圧に設定する交流電源

:ピーク短絡回路電流設定用抵抗

:交流電圧ゼロクロスに同期し,規定の期間閉路するスイッチ

:片方向試験時に接続する全波又は半波整流回路

図 13 非繰返しピークオン電流ITSM検証用試験回路

24

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

スイッチS1は,交流電源のゼロ電圧点で,単に開路又は閉路する。これは,デバイスを交流サイクル

の半波又は全波で確実に試験するためである。交流試験機の開回路電圧及び短絡回路電流値,又はこれと

同等な波形,波形ピーク値並びにスイッチS1の閉継続時間を規定しなければならない。試験機は,確実

にTSSをオン状態にスイッチする能力がなければならない。双方向電流動作を規定しない片方向TSSは,

全波又は半波試験をするためにブリッジ又は半波整流器を交流電源に加えることが必要である。スイッチ

S1が規定試験の継続時間動作した後,熱平衡状態に復帰したデバイスは,いかなる特性値についても規格

値を外れてはならない(試験前後で大きく変化する特性値については,デバイス劣化の兆候の可能性があ

る)。試験による故障については,5.3の基準に沿って分類しなければならない。

試験継続時間は,規定周波電源での時間又は交流サイクル数として規定してもよい。非繰返し電流定格

試験は,デバイスが熱平衡状態に戻るまで繰り返してはならない。特に規定がない限り,デバイスはその

寿命期間に故障することなく100回以上この試験に耐える能力をもつことが望ましい。ITSM定格は,試験

継続時間によって変動し,幾つかの波形値が適用上の要求を満たすために必要となる。推奨する継続時間

は0.1秒,1秒及び10秒での1サイクルである。

5.4.4

非繰返しピークインパルス電流,IPPSM この試験の目的は,TSSが故障することなく短絡電流値

IPPSMの規定のインパルス波形に耐えることを検証することである。使用する試験回路は,機能的に図14

と等価でなければならない。インパルス発生器は,開回路電圧及び短絡回路電流,又はこれらと同等な波

形及び波形ピーク値を規定しなければならない。発生器は,確実にTSSをオン状態にスイッチする能力が

なければならない。インパルスの通電を止めた後,熱平衡状態に復帰したデバイスは,いかなる特性値に

ついても規格値を外れてはならない(試験前後で大きく変化する特性値については,デバイス劣化の兆候

の可能性がある。)。試験による故障については,5.3の基準に沿って分類しなければならない。

A

SG

DUT

DUT

A

SG

:供試品

:ピーク電流計

:規定の特性を備えたインパルス発生器

図 14 非繰返しピークインパルス電流IPPSM検証用試験回路

TSSの各スイッチング象限は,個別に試験し,測定しなければならない。非繰返し電流定格試験は,デ

バイスが熱平衡状態に戻るまで繰り返してはならない。特に規定がない限り,デバイスがその寿命期間に

故障することなく100回以上この試験に耐える能力をもつことが望ましい。検証のためには,より少ない

試験回数を選んでもよい。IPPSM定格は,波形によって変動し,幾つかの波形値が適用上の要求を満たすた

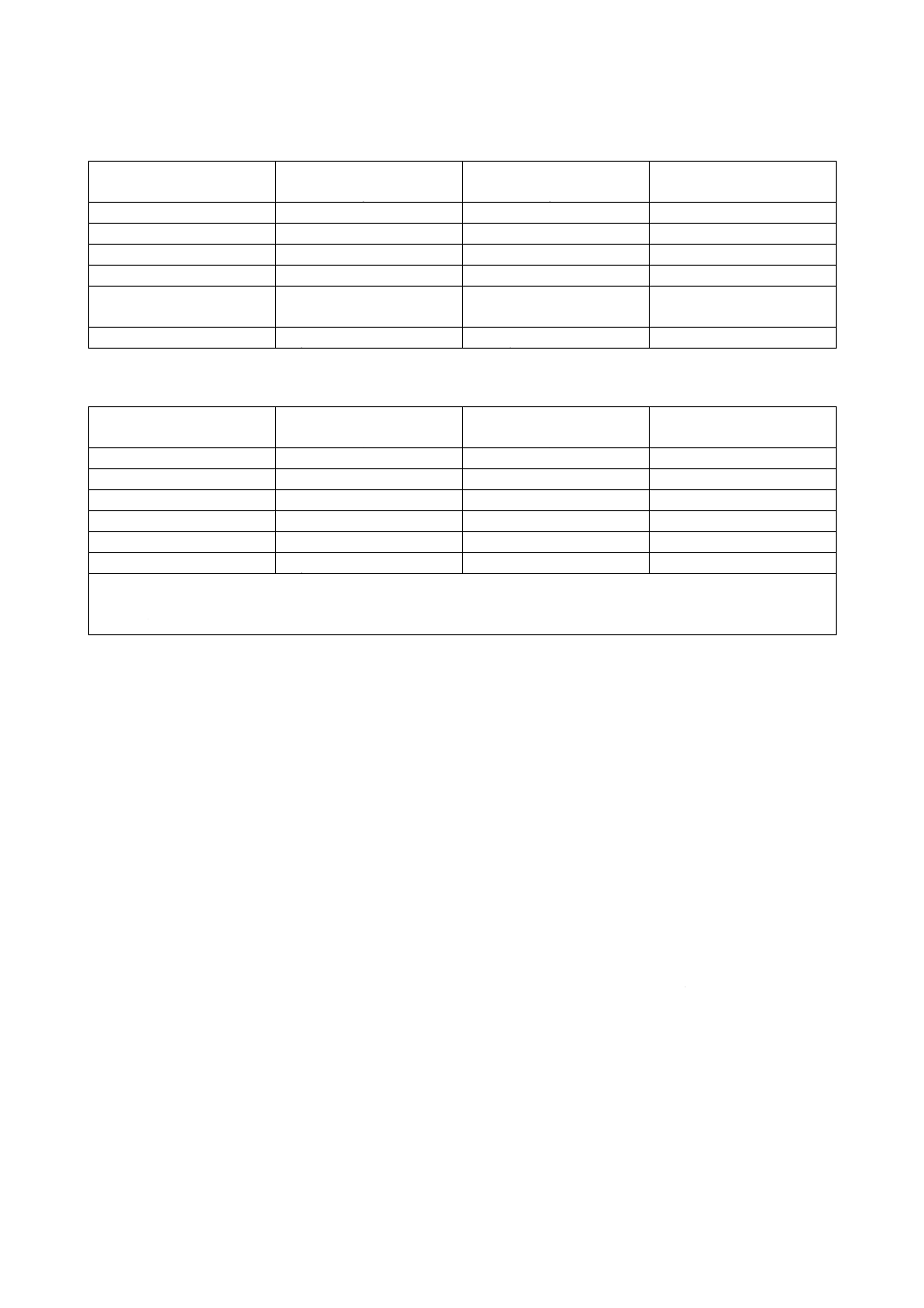

めに必要となる。表2及び表3に,電気通信用途におけるTSSの試験に共通的に用いられる幾つかの波形

を示す。

25

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表 2 電気通信分野に共通に適用するインパルス電圧波形

表 3 電気通信分野に共通に適用するインパルス電流波形

波形

波頭長

µs

波尾長

µs

参照

2/10

2(最大)

10(最小)

GR-1089-CORE[B.1]

8/20コンビネーション波形

8(±20 %)

20(±20 %)

JIS C 1000-4-5

10/160

10(最大)

160(最小)

FCC,47 CFR Part 68[B.2]

10/560

10(最大)

560(最小)

FCC,47 CFR Part 68[B.2]

5/320

5(±30 %)

320(±20 %)

FCC,47 CFR Part 68[B.2]

10/1 000

10+0

-5

1 000(±200)

IEEE Std C62.45[B.3]

備考 通信回線を試験するときには,1.2/50及び8/20のコンビネーション波形発生器に対して最小40 Ωの外部直列抵

抗の使用をJIS C 1000-4-5で規定している。適用時の短絡回路電流の波形は,8/20でなく,むしろ1.2/50電圧波

形に近い。

5.4.5

繰返しピーク逆電圧,VRRM この試験の目的は,規定の繰返しピーク逆電圧を連続して印加した

ときに,TSSが高インピーダンス絶縁状態を維持することを検証することである。図10と機能的に等価な

回路によって繰返しピーク逆電流IRRMを観測しながら,規定の繰返しピーク逆電圧VRRMを阻止方向に印

加しなければならない。測定した電流値は,IRRMの規定最大値を超えてはならない。VRRM試験後,デバイ

スはいかなる特性値についても規格値を外れてはならない。測定持続時間は,デバイスに期待される信頼

性を確立するために十分となるようにしなければならない(試験前後で大きく変化する特性値については,

デバイス劣化の兆候の可能性がある。)。試験による故障については,5.3の規定に沿って分類しなければな

らない。

5.4.6

非繰返しピーク順電流,IFSM この試験の目的は,順導通又は逆導通TSSのダイオード部が,規定

した持続時間の交流サージ電流に故障することなく耐えることを検証することである。非繰返しピーク順

電流IFSMの評価には,非繰返しピークオン電流ITSMと同じ試験方法(5.4.3及び図13参照)を用いなけれ

ばならない。導通時間が1サイクル又はそれ以上である場合には,IFSMよりもむしろITSMを適用する(ITSM

は,ダイオードとサイリスタの導通を含む。)。IFSM試験後,熱平衡状態に復帰したデバイスは,いかなる

特性値についても規格値を外れてはならない(試験前後で大きく変化する特性値については,デバイス劣

化の兆候の可能性がある。)。試験による故障については,5.3の規定に沿って分類しなければならない。

波形

波頭長

µs

波尾長

µs

参照

2/10

2(最大)

10(最小)

GR-1089-CORE[B.1]

1.2/50コンビネーション波形 1.2(±30 %)

50(±20 %)

JIS C 1000-4-5

10/160

10(最大)

160(最小)

FCC,47 CFR Part 68[B.2]

10/560

10(最大)

560(最小)

FCC,47 CFR Part 68[B.2]

10/700

10(±30 %)

9(±30 %)

700(±20 %)

720(±20 %)

JIS C 1000-4-5

FCC,47 CFR Part 68[B.2]

10/1 000

10+0

-5

1 000+1000

-0

IEEE C62.45[B.3]

26

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.4.7

繰返しピーク順電流,IFRM この試験の目的は,順導通又は逆導通TSSのダイオード部が,規定し

た連続的なピーク順電流を流し続けても故障しないこと又は最大接合温度の規定値を超えないことを検証

することである。繰返しピーク順電流IFRMの検証には,繰返しピークオン電流ITRMと同じ試験方法(5.4.2

及び図11)を用いなければならない。特に規定がない限り,ITRMはダイオード及びサイリスタの導通を含

むことから,IFRMの代わりにITRMを用いることが望ましい。

5.4.8

臨界オン電流上昇率,di/dt(Critical rate of rise of on-state current) この試験の目的は,TSSが,

インパルス波形の波頭に現れることのある電流の急しゅんな立ち上がりに耐えることを検証することであ

る。使用する試験回路は,図15と機能的に等価でなければならない。

DUT

CT

CRO

I

V

RG

DUT

CT

RG

CRO

:供試品

:変流器又は同等品

:規定のdi/dtを備えた上昇波形発生器

:2チャンネルオシロスコープ又は同等品

図 15 臨界オン電流上昇率(di/dt)検証用試験回路

電圧V及び電流Iの観測装置(通常,電圧及び電流プローブを備えたデジタル又はストレージオシロス

コープ)は,回路状態を記録するために用いる。デバイスにdi/dtインパルスを印加後,熱平衡状態に復帰

したデバイスは,いかなる特性値についても規格値を外れてはならない(試験前後で大きく変化する特性

値については,デバイス劣化の兆候の可能性がある。)。試験による故障については,5.3の規定に沿って分

類しなければならない。

di/dt発生器については,波頭部のdi/dt,ピーク(最大)電流値及び波形(一般に波尾長は比較的短い。)

を規定しなければならない。この試験には正確な波形を用いることが不可欠であり,デバイスの製造業者

は,試験回路及び波形の詳細に精通していなければならない。特に規定がない限り,標準的なサイリスタ

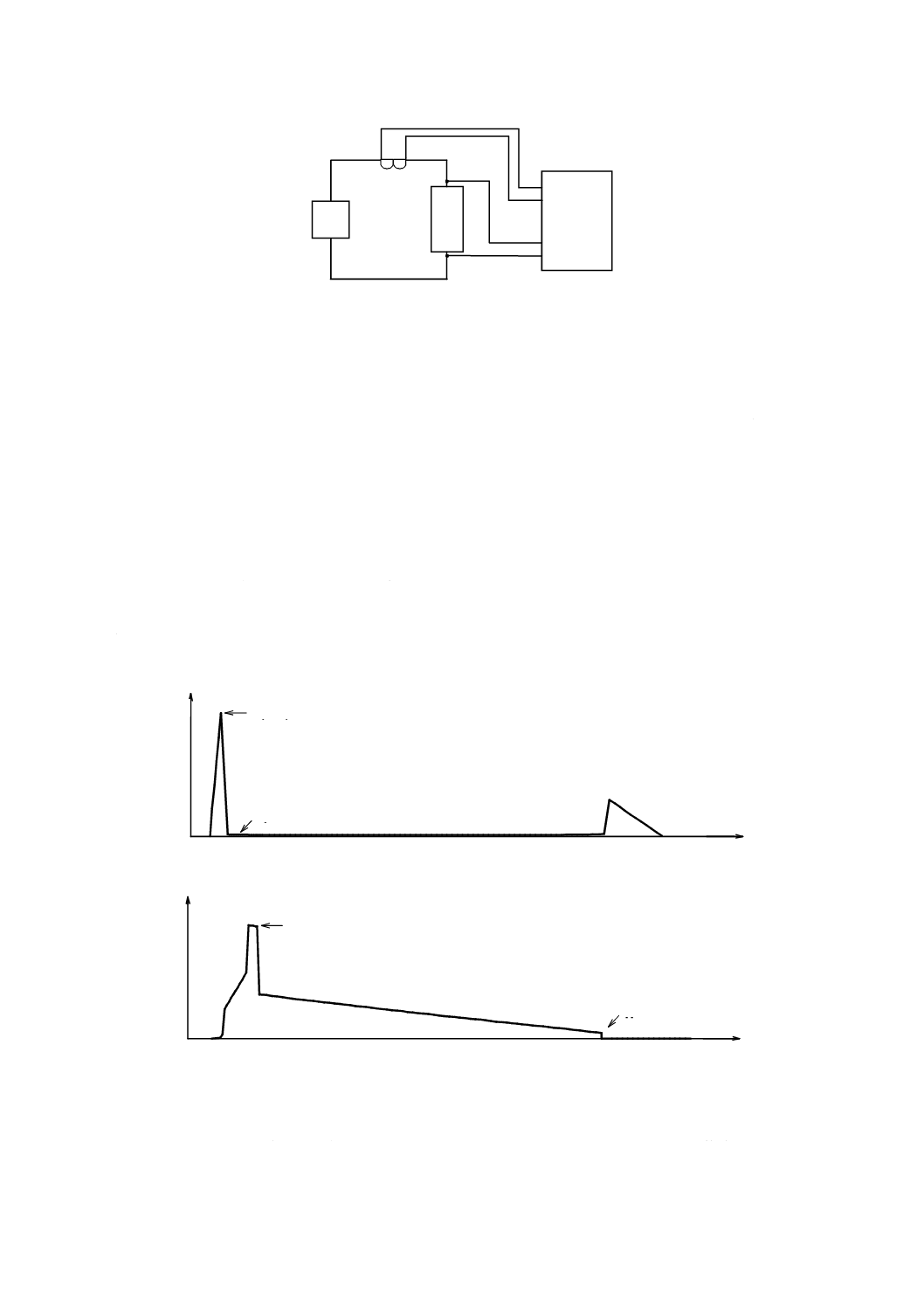

di/dt試験回路に基づいた発生器を用いることが望ましい。基本回路構成及び波形を図16に示す。

TSSの各スイッチング象限は,個別に試験し,測定しなければならない。非繰返し電流定格試験は,デ

バイスが熱平衡状態に戻るまで繰り返してはならない。特に規定がない限り,デバイスがその寿命期間に

故障することなく100回以上この試験に耐える能力をもつことが望ましい。検証のためには,より少ない

試験回数を選んでもよい。

27

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

DUT

S1

PS

R1

CT

CRO

I

V

REC

L

C

VS

V(BO)

di/dt

VS/L

Ipk

VS(C/L)0.5

tW

π(LC)

0.5

Ipk

tW

di/dt

P

P

P

P

VS >> V(BO)

di/dt >> VS/L

Ipk >> VS (C/L)0.5

tW >> π(LC)0.5

Ipk

di/dt

tW

DUT

CT

PS

R1

S1

REC

C

L

CRO

:供試品

:変流器又は同等品

:VSに設定する直流電源

:充電電流制限用抵抗

:試験開始時閉路,電流ゼロクロス時開路するスイッチ

:マイナス電流導通用整流回路

:エネルギー貯蔵及びタイミング用コンデンサ

:di/dt設定用インダクタンス

:2チャンネルオシロスコープ又は同等品

図 16 正弦半波di/dt試験回路

5.5

特性試験手順 防護電圧を設定するための過電圧及び過電流試験レベルについては,一つ以上の

IEC及びITU-T規格を利用しなければならない。これらの試験レベルは,試験回路に装置機器のサージ協

調部品を含めることによって,最終の装置機器レベルに変更してもよい。

5.5.1

オフ電流,ID この試験の目的は,規定した直流オフ電圧を印加したときの,TSSのオフ電流を決

定することである。 使用する試験回路は,図17と機能的に等価でなければならない。直流供給源の電圧

出力は,オフ電圧の立ち上がりの臨界電圧上昇率の最小値より低い割合で,0 Vから規定した直流オフ電

圧VDまで電圧を上昇しなければならない。直流電圧は,オフ電流IDの値が安定するまで印加する。IDの

最終値を測定しなければならない。特に規定がない限り,TSSの各スイッチング象限は,個別に試験し測

定しなければならない。

28

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

PS1

DUT

V

A

DUT

A

V

RS1

:供試品

:微少電流計

:直流電圧計

:VDまで電圧上昇する直流電源

図 17 オフ電圧VD印加時のオフ電流ID試験回路

5.5.2

繰返しピークオフ電流,IDRM この試験の目的は,規定した繰返しピークオフ電圧を印加したとき

の,TSSのピークオフ電流を決定することである。図10と機能的に等価な回路で繰返しピークオフ電圧

VDRMの定格値を主端子間に印加し,繰返しピークオフ電流IDRMを測定しなければならない。特に規定がな

い限り,TSSの各スイッチング象限は,個別に試験し,測定しなければならない。

5.5.3

繰返しピーク逆電流,IRRM この試験の目的は,規定した繰返しピーク逆電圧を印加したときの,

逆阻止TSSのピーク逆電流を決定することである。図10と機能的に等価な回路でのブロッキング象限に

おいて主端子間に繰返しピーク逆電圧VRRMの定格値を印加し,デバイスの繰返しピーク逆電流IRRMのピ

ーク値を測定しなければならない。

5.5.4

ブレークオーバ電圧,V(BO)及び電流,I(BO) この試験の目的は,規定した上昇率でのTSSのブレー

クオーバを決定することである。

使用する試験回路は,図18と機能的に等価でなければならない。試験機は,開回路電圧及び短絡回路電

流値,又はこれと同等な上昇率,波形,波形ピーク値並びに交流試験時間を規定しなければならないが,

試験機の回路図を示すことで代用できる。オフ状態からオン状態にスイッチングするときに供試品に発生

するピーク電圧V(BO)を測定しなければならない(図19〜図24参照)。複数サイクルの交流試験では,測定

値は全個々のサイクルV(BO)値の最大値でなければならない。V(BO)に対応する瞬時デバイス電流I(BO)は,商

用周波数の立ち上がり電圧比に対しても測定しなければならない(図20,図22及び図24参照)。

29

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

DUT

I

V

CT

TG

CRO

DUT

CT

TG

CRO

:供試品

:直流カレントプローブ又は同等品

:オフからオンへ供試品を規定条件でスイッチングさせる試験機

:2チャンネルオシロスコープ又は同等品

例 図19〜24を得るために使用した試験機TGは,電流源及び短絡用300 Ωの抵抗器からなる。電流を,

0 Aからスタートさせ,3.33 A/ms(開回路電圧1 000 V/ms)で3 Aに上昇させる。その後,5 Aに上

昇させ200 μsの間維持する。さらに2 Aに低下させ,0.2 A/msで0 Aとする。この一連の手順は,

デバイスの特性値V(BO),I(BO),VS,IS,VT及びIHを測定するために使用する。

図 18 ブレークオーバV(BO)及びI(BO)並びにオン電圧VT試験回路

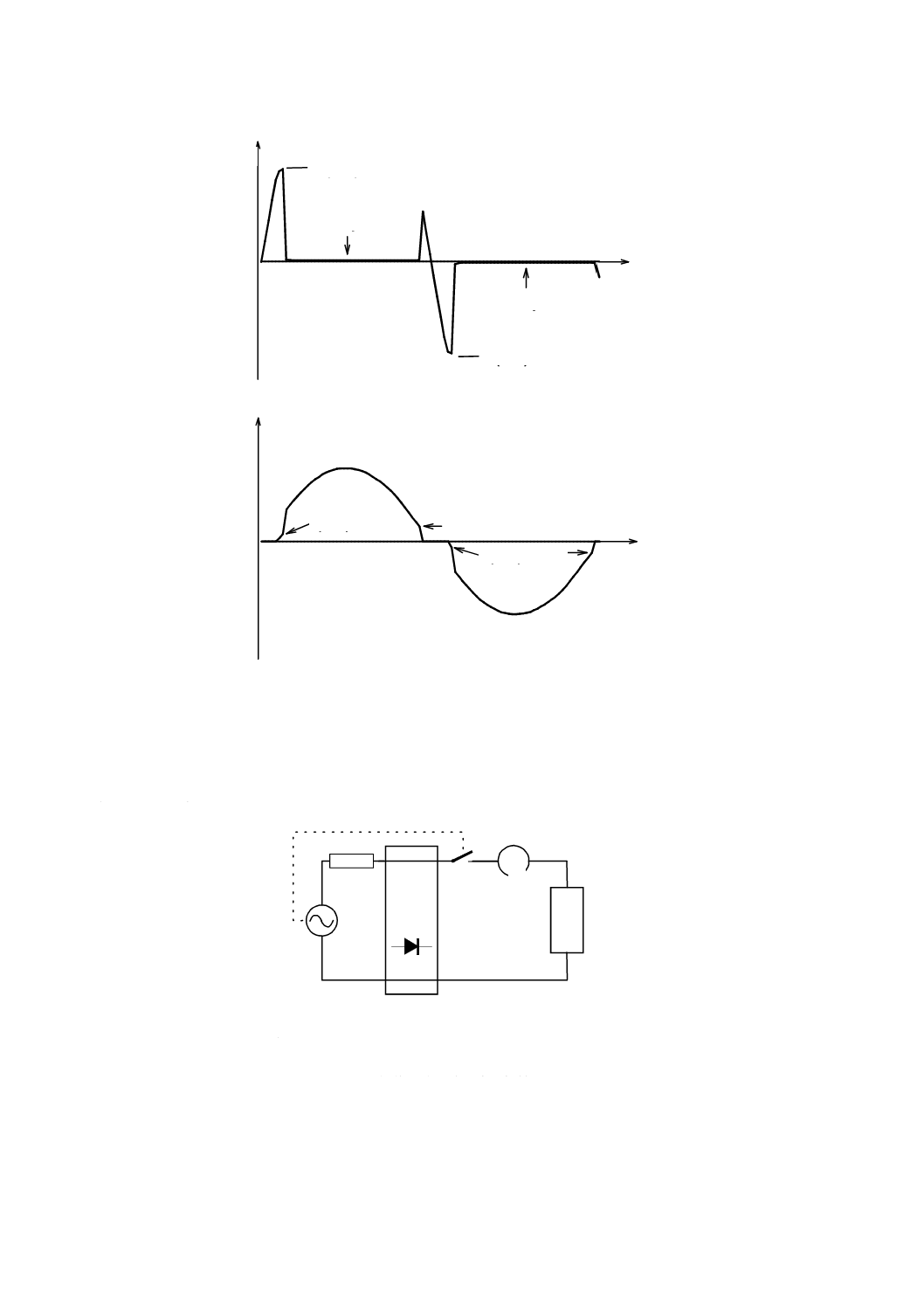

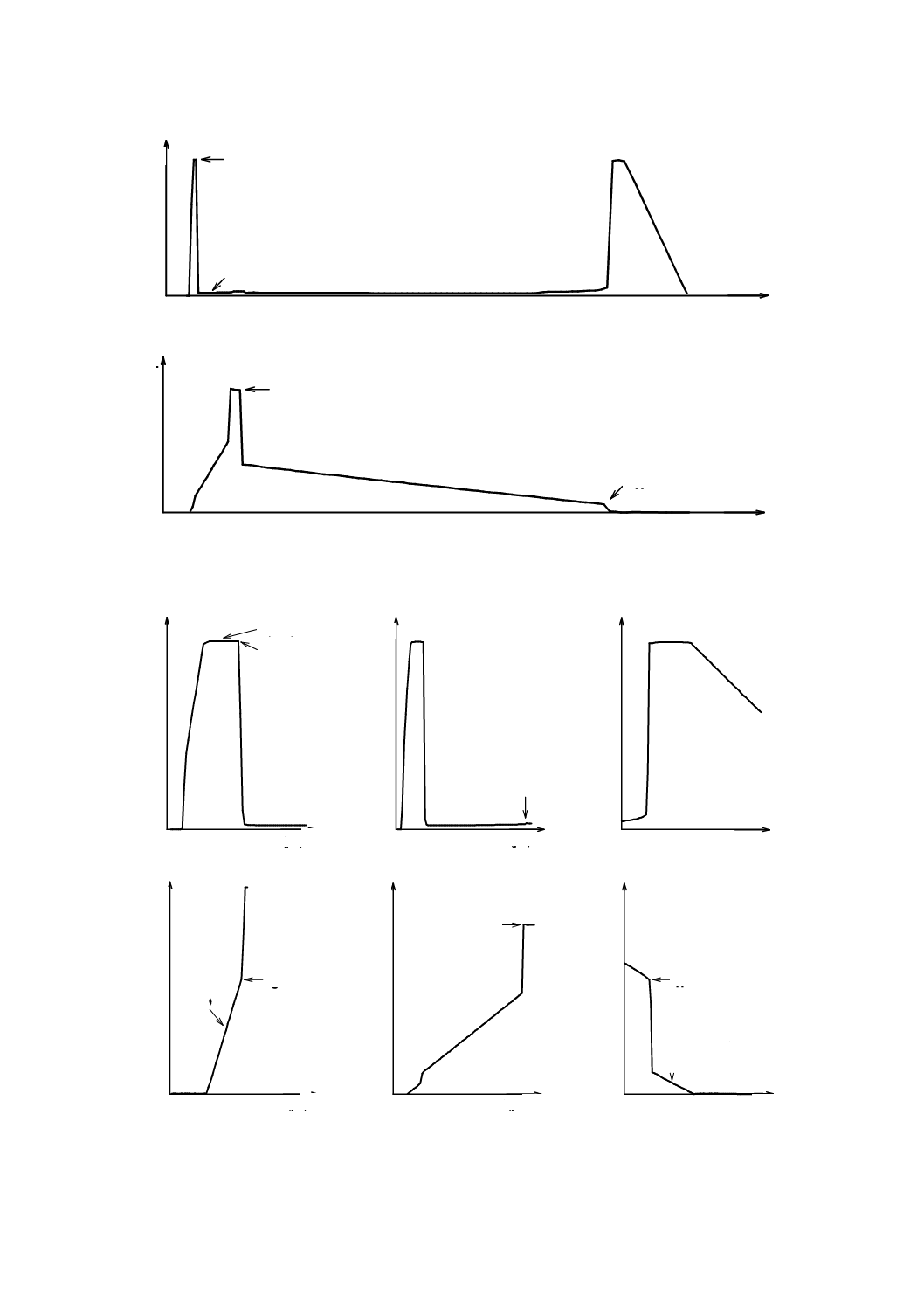

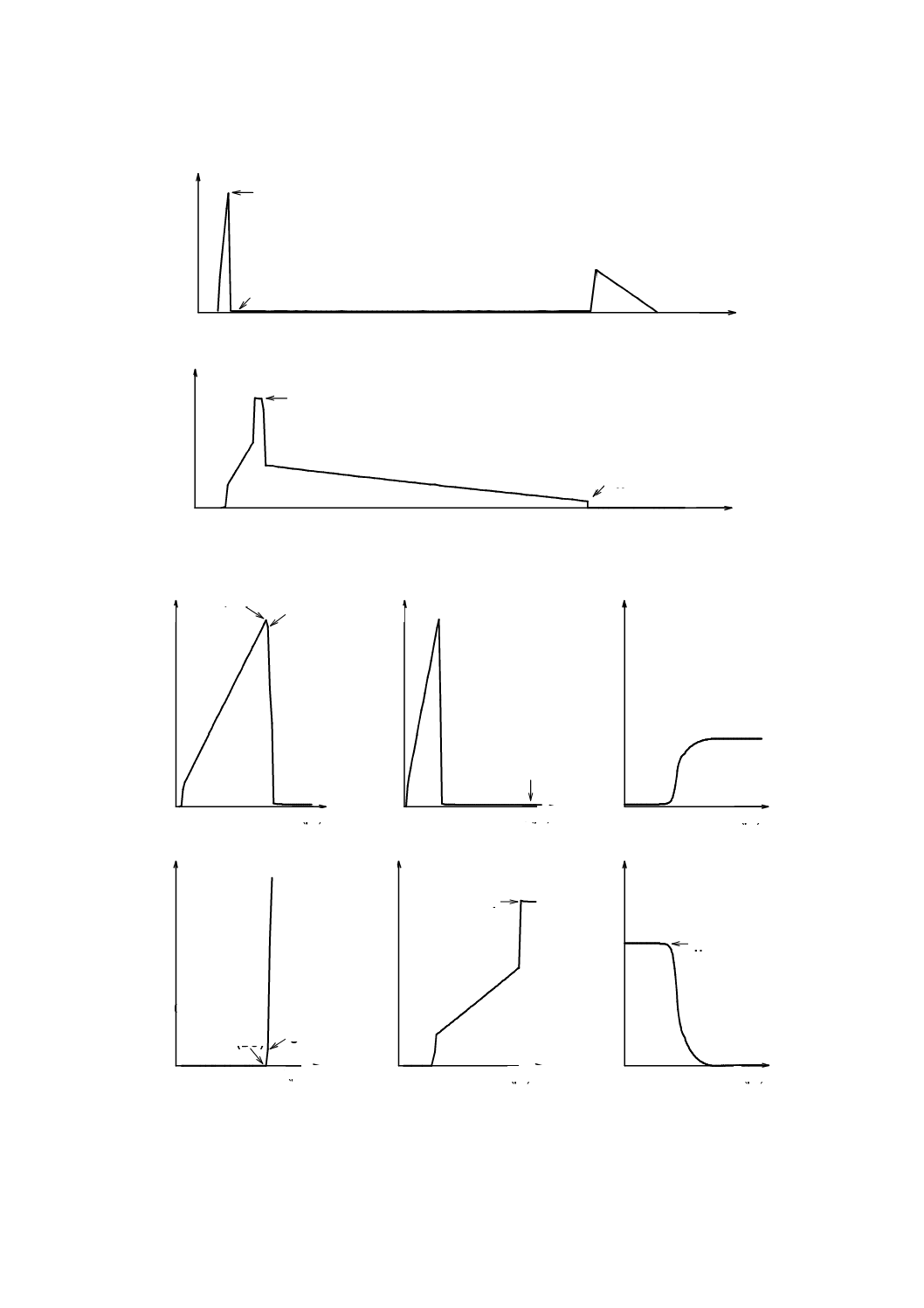

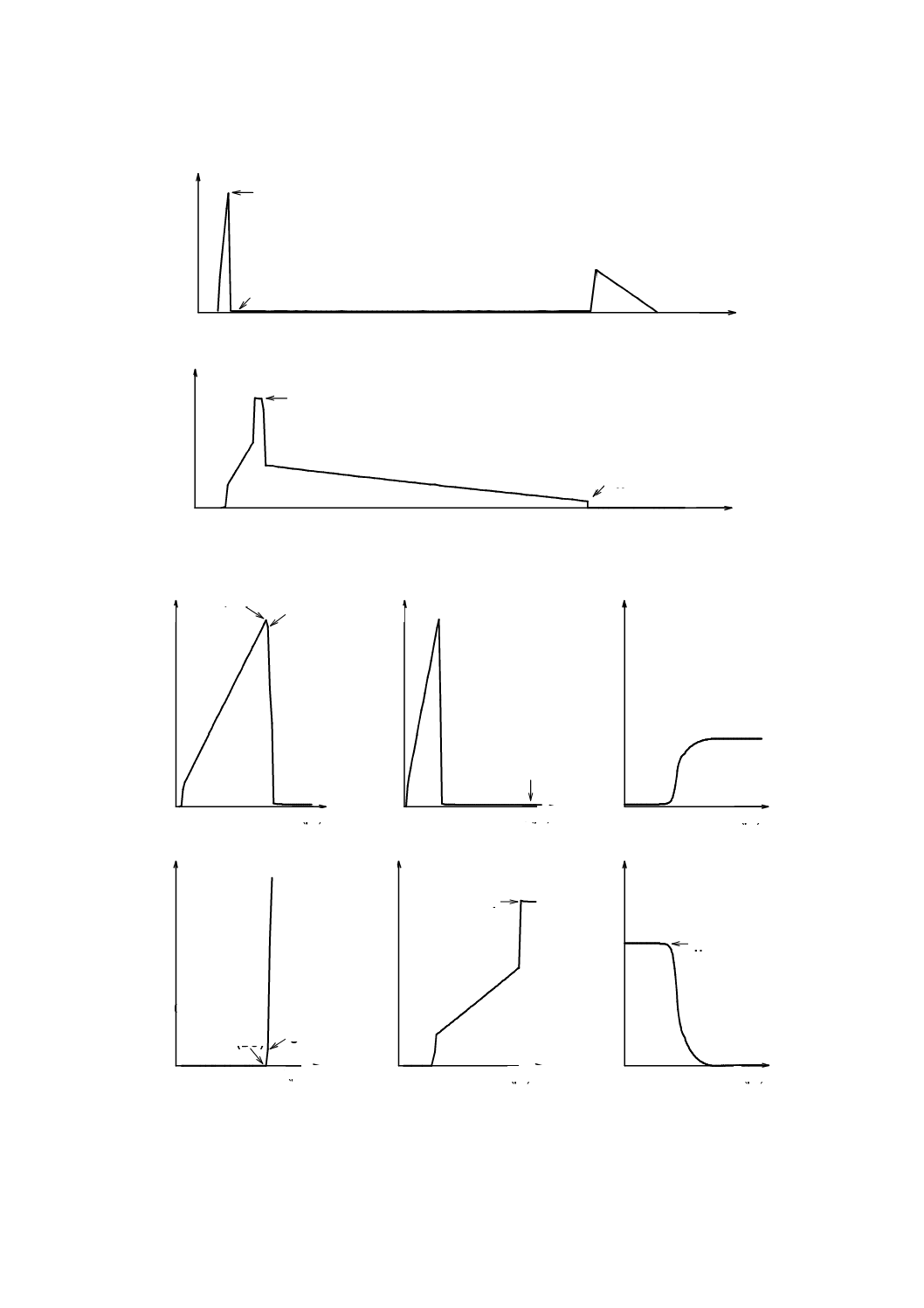

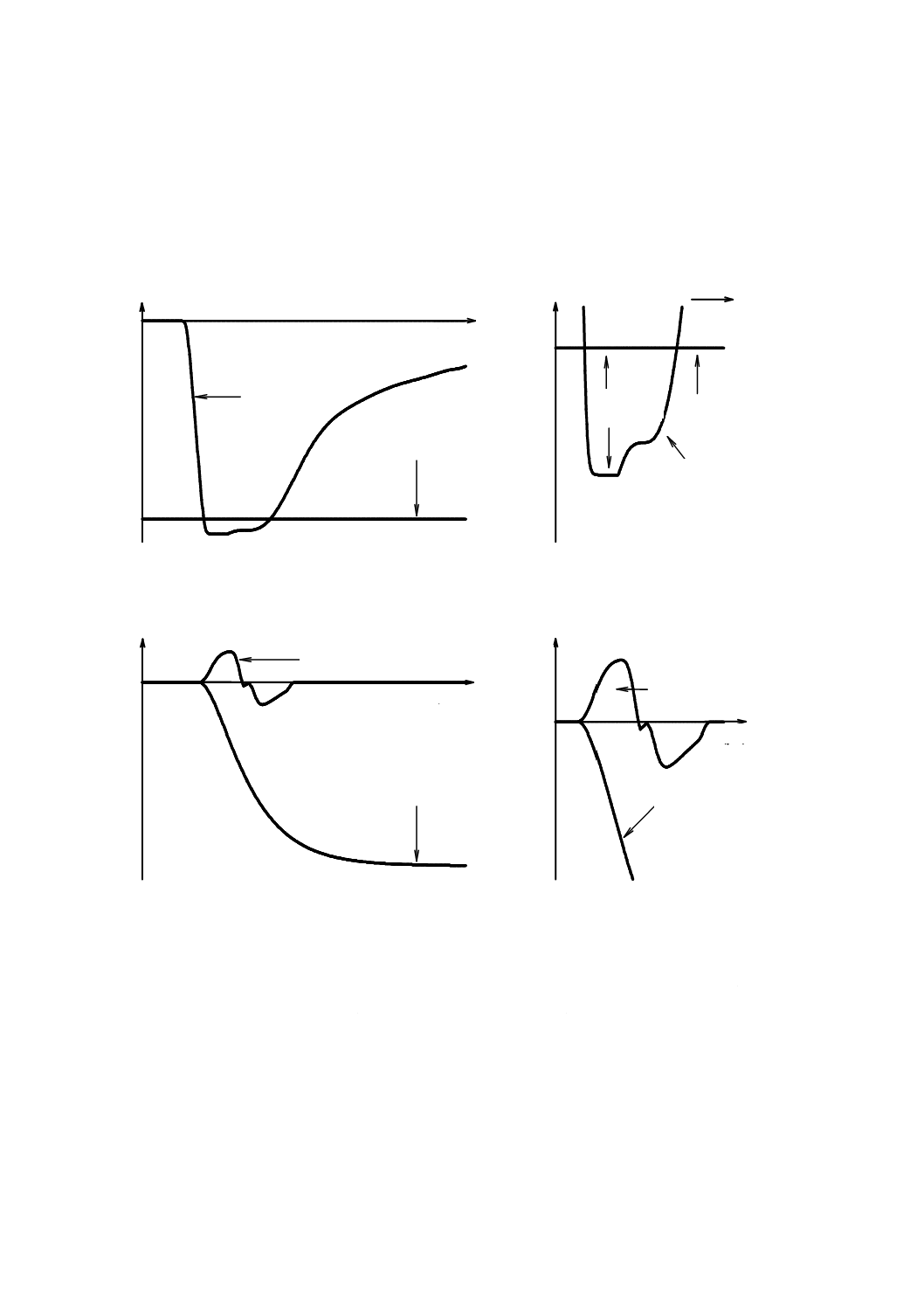

TSSの正性ブレークダウンスロープ,負性ブレークダウンスロープ及びゲート制御の3タイプのスイッ

チング現象の電圧及び電流波形を図19〜図24に示す。全体的な波形の拡大部分は,クランピング,オン

状態及びオフ状態の条件を示している(デバイスの3タイプの原理的な電圧電流特性について,図1に示

す。)。図示した波形は,デバイスタイプの一般的な波形を表しており,これらは,代表値として扱うこと

が望ましい。

t (ms)

i

IT

IH

t (ms)

v

V(BO)

VT

図 19 正性ブレークダウンスロープTSSのスイッチング及びオン状態波形

TSSの各スイッチング象限は,個別に試験し測定しなければならない。片方向TSSの複合サイクル交流

30

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

試験は,適用上の要求に従い全波又は交流半波で実施しなければならない。V(BO)及びI(BO)は,上昇率によ

って変化し,幾つかの傾斜が適用上の要求を満たすために必要となる。特に規定がない限り,表4に示す

上昇率の1以上を試験に使用することが望ましい。

表 4 ブレークオーバ傾斜率試験値

適用

dv/dt

(開回路)

電源内部抵抗

R

di/dt

(短絡回路)

緩傾斜

4 V/ms

500 Ω(正性スロープ)

4 000 Ω(負性スロープ)

8 mA/ms

1 mA/ms

交流

250 V/ms

250 Ω

1 A/ms

遅い波形インパルス

100 V/µs

100 Ω

1 A/µs

速い波形インパルス

1 000 V/µs

100 Ω

10 A/µs

5.5.5

オン状態電圧,VT この試験の目的は,規定の電流におけるTSSのオン電圧を決定することであ

り,この電圧値は,オン状態電力損失を計算するために使用する。使用する試験回路は,図18と機能的に

等価でなければならない。試験機は,開回路電圧及び短絡回路電流,又は同等の波形及び波形ピーク値を

規定しなければならないが,試験機の回路図を示すことで代用できる。

t (μs)

v

t ( μs)

i (mA)

I(BO)

v

V(BO)

t (μs)

i

IT

IH

t (μs)

v

VT

t (μs)

i

(mA

)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

I(BO)

i(mA)

I(BO)

V(BO)

図 20 図19の拡大図

31

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図 21 ゲート付きTSSのスイッチング及びオン状態波形

IH

電圧クランプ時の電流

VT

t (μs)

VS

V(BO)

t (μs)

I

(

B

O

)

IS

t (μs)

IT

t (μs)

t (ms)

v

v

v

i (mA)

i

i (mA)

t (ms)

t (μs)

t (μs)

t (μs)

t (μs)

I(BO)

t (μs)

I(BO)

t (ms)

図 22 図21の拡大図

IT

IH

V

(BO)

VT

v

i

t (ms)

t (ms)

V(BO)

32

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

IT

IH

i

t (ms)

V(BO)

VT

v

t (ms)

図 23 負性ブレークダウンスロープTSSのスイッチング及びオン状態波形

IH

IT

I(BO)

V(BO)

VT

I(BO)は小さすぎて

決定できない。

i (mA)

i (mA)

VS

IS

v

v

v

i

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

t (μs)

I

図 24 図23の拡大図

試験機は供試品をオン状態にスイッチングし,オン電圧VTは規定した時間及びオン電流値ITで測定し

33

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

なければならない(図20,図22及び図24のVT波形を参照)。TSSの各スイッチング極性は,個別に試験

し,測定しなければならない。VTの値は,IT値及び時間の値に応じて変化する。オン電圧VTの小電流値及

び大電流値は,交流及びインパルス動作にわたって必要となる場合もある。

DUT

I

V

CT

R

CRO

TG

DUT

CT

TG

R

CRO

:供試品

:直流カレントプローブ又は同等品

:オフからオンへ供試品を規定条件でスイッチングさせる試験機

:電源抵抗設定用抵抗(要求がある場合)

:2チャンネルオシロスコープ又は同等品

図 25 保持電流IH試験回路

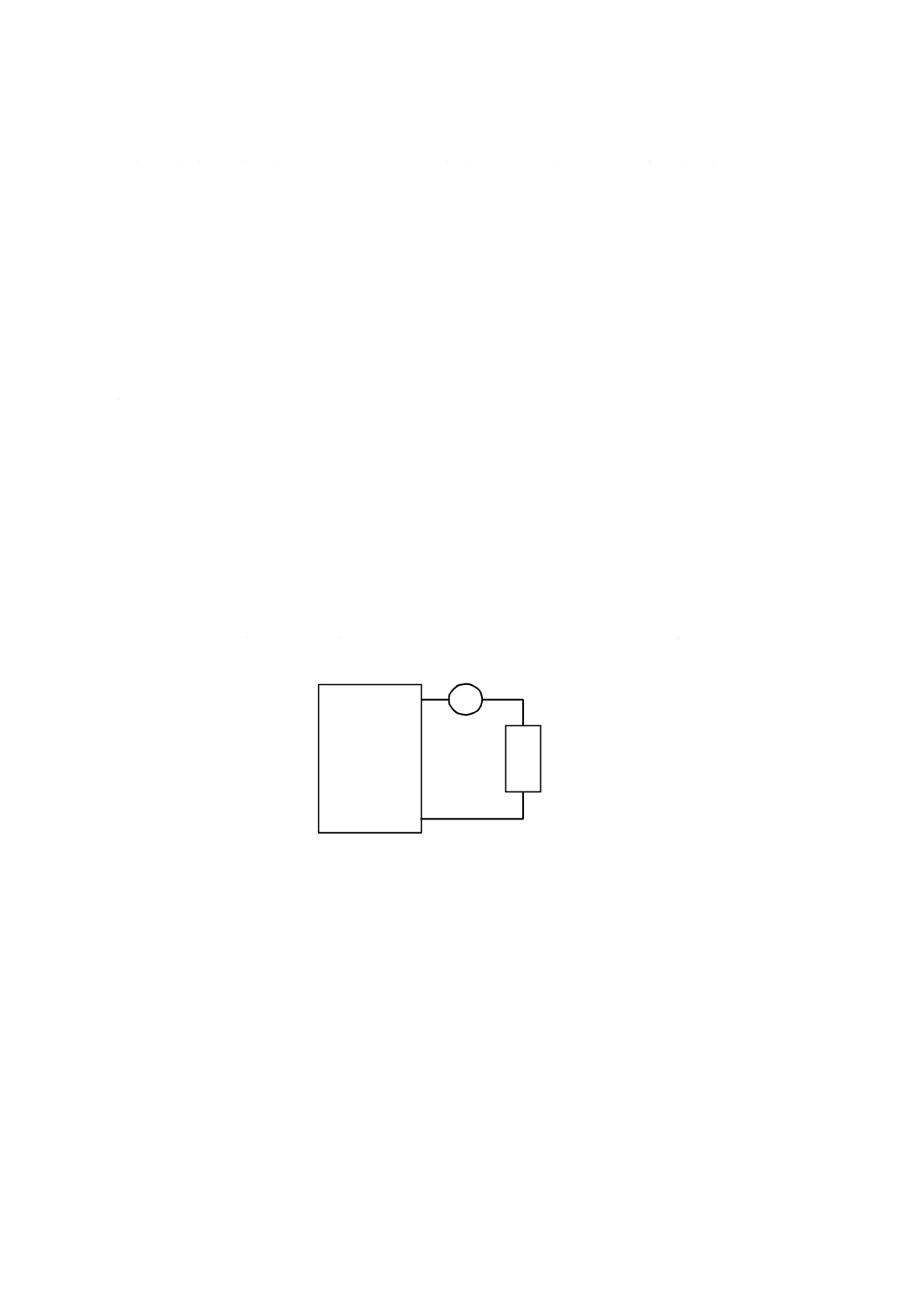

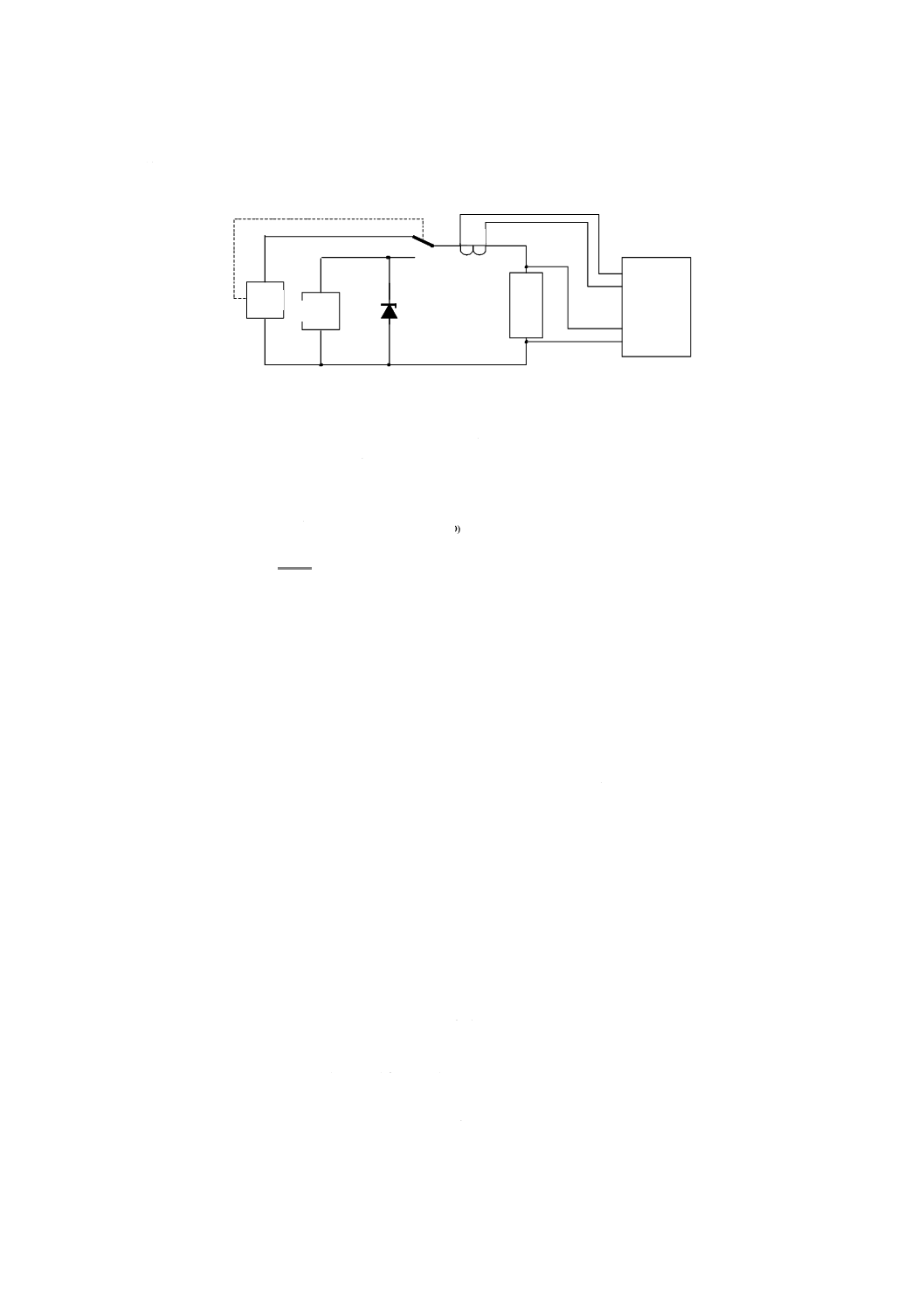

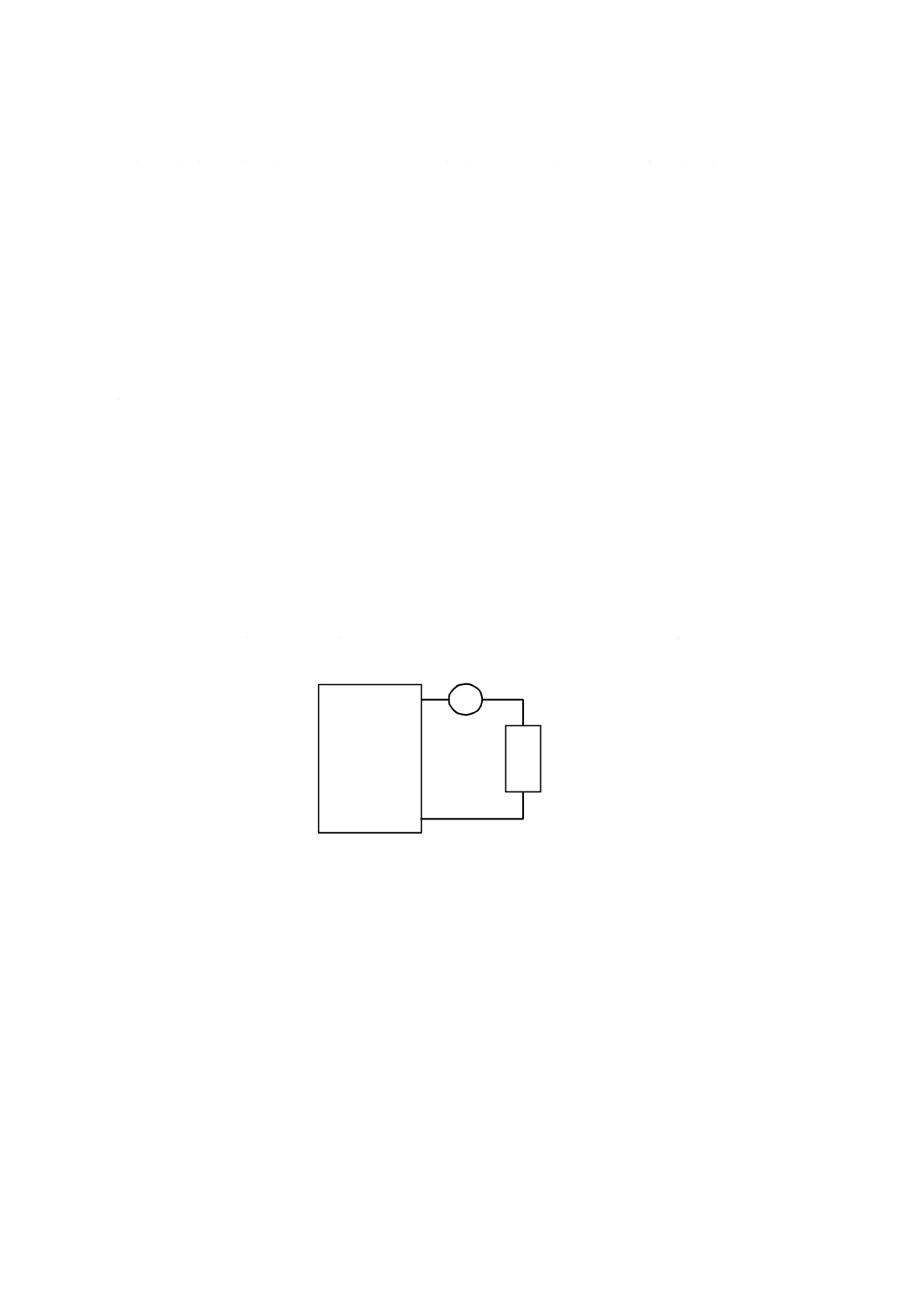

5.5.6

保持電流,IH この試験の目的は,TSSの保持電流を決定することである。使用する試験回路は,

図25と機能的に同等でなければならない。試験機は,開回路電圧及び短絡回路電流,又は同等の波形及び

波形ピーク値を規定しなければならない。

試験機は,供試品をオン状態に切り替えなければならない。次にデバイスがスイッチオフするまでオン

電流を滑らかに下げなければならない(図20,図22及び図24のIH波形を参照)。

スイッチオフは,デバイスの電圧が規定した境界レベルを超えたときである。保持電流は,この現象が

起こるときの傾斜波形の瞬時値を推定し測定する。この確立した手法は,デバイスがオン状態を維持する

電流ではなくむしろデバイスがスイッチオフするときの電流である。ほとんどの用途において,保持する

値よりスイッチする値が必要である。

試験機としてインパルス発生器を使用するとき,スイッチオフポイントを適切に識別するには,その出

力電圧が非常に小さい場合がある。スイッチオフレベルを増大させるために,発生器及び直流電圧電源

(VDRM)から保持電流IHの最小規定値を下回る電流をダイオード(ORed)を介して供給するのが望まし

い(図26参照)。TSSの各スイッチング象限は,個別に試験し,測定しなければならない。

34

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

DUT

I

V

CT

R

D1

D2

+

-

+

-

CRO

PS

SG

DUT

CT

SG

PS

R

D1

D2

CRO

:供試品

:直流カレントプローブ又は同等品

:規定の特性を備えたインパルス発生器

:規定の電圧に設定する直流電源

:直流電源設定用抵抗

:電源絶縁用ダイオード

:インパスル発生器絶縁用ダイオード

:2チャンネルオシロスコープ又は同等品

図 26 直流バイアス印加時の保持電流IH試験回路

5.5.7

オフ状態静電容量,Co この試験の目的は,規定した条件でTSSのオフ状態の静電容量を決定す

ることである。使用する試験回路は,図27と機能的に等価でなければならない。供試品のオフ状態静電容

量C0は,規定した直流(VD)及び交流(Vd及びf)バイアスレベルで測定しなければならない。特に規定

がない限り,100 kHz < f < 1 MHzの周波数で,Vd=0.1 Vrmsの交流バイアスレベルを使用することが望ま

しい。直流バイアスレベルは,意図する適用を代表するレベル及び0 Vでなければならない。

DUT

HI

LV

HV

LI

静電容量測定器

VD,f,Vd

Li

Hi

DUT

HV

Hi

LV

Li

:供試品

:Hi,電圧検出

:Hi,電流供給

:Lo,電圧検出

:Lo,電流帰還

図 27 静電容量測定回路

35

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

静電容量測定装置が所要の直流バイアス電圧を供給できない場合は,図28に示す回路を使用する。

C1

R1

R2

C2

HI

LV

HV

LI

DUT

PS1

静電容量

測定器

Guard

f,Vd

(VD)

Hi

Li

DUT

C1,C2

R1,R2

PS1

HV

Hi

LV

Li

Guard

:供試品

:直流阻止用コンデンサ,C1=C2>>C0

:直流供給抵抗,R1=R2<<VD/ID

:VDに設定する直流電源

:Hi,電圧検出

:Hi,電流供給

:Lo,電圧検出

:Lo,電流帰路

:ガード接地端子[測定器のきょう(筐)体に接続する中性端子]

図 28 外部直流バイアス印加時の静電容量測定回路

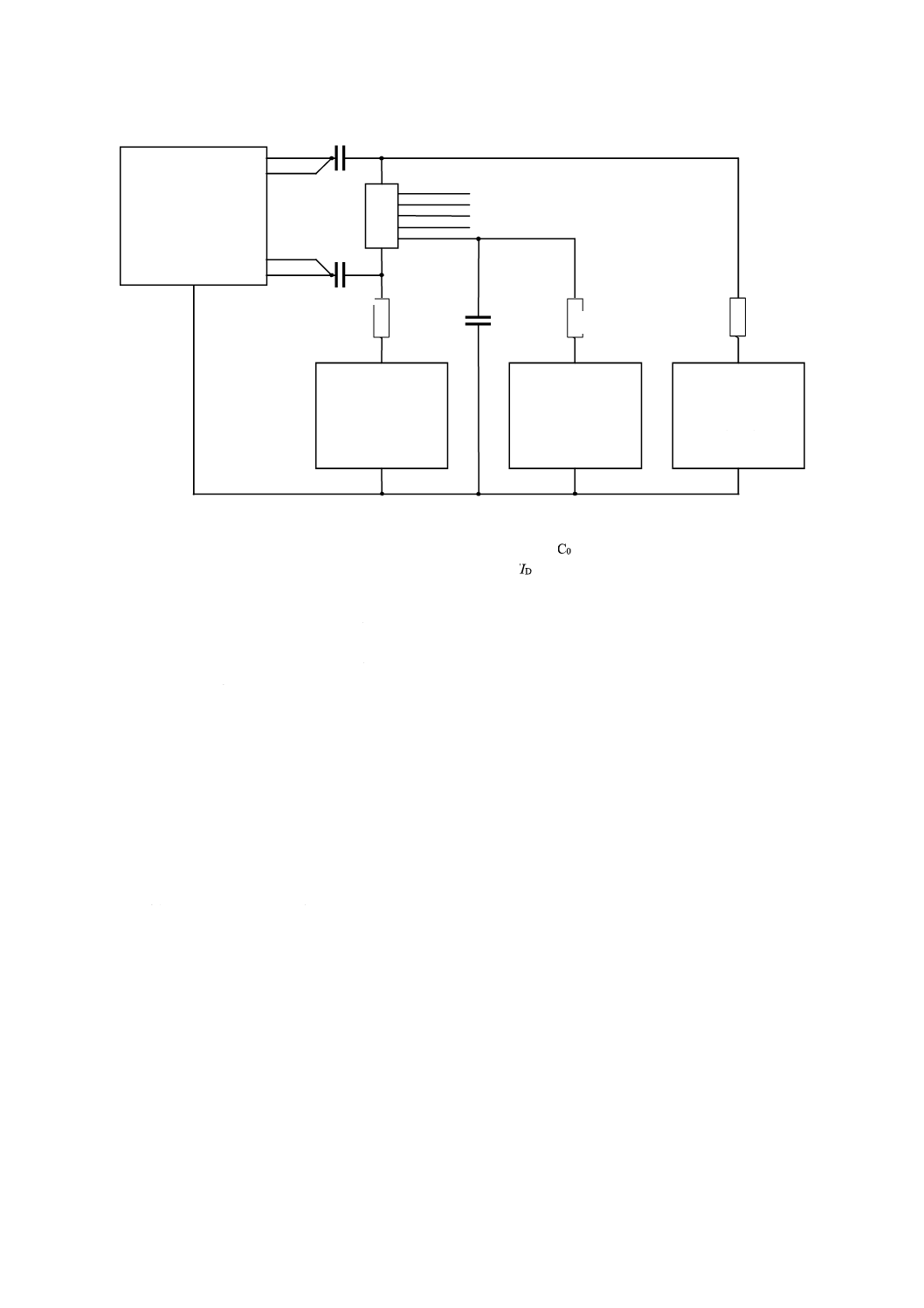

3端子TSSの場合,測定しない端子は,静電容量測定及び適用しようとする代表的な直流バイアスレベ

ルから影響のないようにしなければならない(図29参照)。

4端子又はそれ以上の端子をもつ同一パッケージの多端子TSSでは,測定しないTSSが測定端子と中性

端子との間に直にあるならば,同様の測定手法を用いてもよい(図29参照)。この測定手法は,一つ以上

の測定しないTSSが内部ノード(端子ではない接続点又は節点)で測定端子対に接続している場合は適用

できない。

36

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

CN

Guard

C1

R2

C2

HI

LV

HV

LI

DUT

R1

PS1

RN

PSN

PS2

静電容量

測定器

他端子

f,Vd

(VD1)

(VDN)

(VD2)

Hi

Li

DUT

C1,C2…CN

R1,R2…RN

PS1,PS2…PSN

HV

Hi

LV

Li

Guard

:供試品

:直流阻止用コンデンサ,C1=C2…CN>>C0

:直流供給抵抗,R1=R2…RN<<VD/ID

:VD1,VD2…VDNに設定する可変電圧直流電源

:Hi,電圧検出

:Hi,電流供給

:Lo,電圧検出

:Lo,電流供給

:ガード接地端子[測定器のきょう(筐)体に接続する中性端子]

図 29 多端子TSSの静電容量試験回路

5.5.8

ブレークダウン電圧,V(BR) この試験の目的は,規定した電流レベルでのTSSのブレークダウン

電圧を決定することである。規定幅のパルス及びブレークダウン電流I(BR)を供試品に流さなければならな

い。安定したブレークダウン電圧V(BR)値は,図30と機能的に等価な回路でのパルス終端近傍で測定する。

特に規定がない限り,試験電流1 mAのI(BR)で40 ms以下のパルス幅を用いることが望ましい。TSSの各

スイッチング極性は,個別に試験し測定しなければならない。V(BR)の値は,接合温度(初期値及び試験に

よる温度)及び試験電流に依存する。

37

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

DUT

I

V

CT

CRO

ZD1

PG1

DUT

CT

PG1

ZD1

CRO

:供試品

:直流カレントプローブ又は同等品

:定電流パルス発生器,I(BR)

:クランプ電圧>V(BO)

:2チャンネルオシロスコープ又は同等品

図 30 I(BR)におけるブレークダウン電圧V(BO)試験回路

正性(正の傾きをもった)ブレークダウンスロープTSS(図1参照)は,電流増加によってブレークダ

ウン電圧が減少するところで,ブレークダウン特性の小電流部分をもつ場合もある。ゼロから規定した試

験電流I(BR)まで電流を徐々に流し,ピーク読取メータでの供試品電圧の測定を行うことで,ブレークダウ

ン電圧V(BR)のピーク値はゼロからI(BR)の電流範囲で規定できる。I(BR)をIDRMに設定しているならば,V(BR)M

値は,VDRM定格を決定するために使用することができる。負性(負の傾きをもった)ブレークダウンスロ

ープTSS(図1参照)では,この測定方法をV(BR)を決定するために使用することができる。

5.5.9

スイッチング電圧,Vs及び電流,Is この試験の目的は,規定した定格でのTSSのスイッチングポ

イントを決定することである。使用する試験回路は,図18と機能的に等価でなければならない。試験機は,

開回路電圧及び短絡回路電流値又は等価回路,上昇率,波形並びに波形ピーク値を規定しなければならな

い。実効電流インピーダンスは,デバイススイッチング抵抗Rsの最大よりも大きくなければならない。供

試品がオフ状態からオン状態にスイッチするときの電圧電流波形を記録しなければならない(図20,図22

及び図24参照)。電圧電流特性は,電圧対電流の記録をプロットすることによって作成することができる。

この特性からスイッチングポイントが視覚的に作成できる。数学的にスイッチングポイントは,特性増分

スロープインピーダンスが電源インピーダンスより負性値となるときに起こる。微小電源インピーダンス

値,発熱及びスイッチング時間の影響は,スイッチングポイントを決定するときに誤差を引き起こす。ス

イッチング電圧及び電流値は,注意して使用することが望ましい。ゲート付きTSSのスイッチング電圧

Vsは,ゲート供給電圧VGG値に近似してよい。

TSSの各スイッチング極性は,個別に試験し測定しなければならない。

5.5.10 順電圧,VF この試験の目的は,規定した電流での順方向導通TSSの順電圧を決定することであ

る。この電圧値は,順方向電力損失を計算するために用いる。使用する試験回路及び波形は,オン電圧VT

の決定に用いるものと同じでなければならない(図18参照)。試験機で順導通に供試品をスイッチし,順

電圧VF値を規定した時間又は規定した順電流値で測定しなければならない。急しゅんな立ち上がりの電流

波形の場合,付加的な順リカバリ電圧を発生することがある。これはVFの測定に含めないほうがよい(図

31参照)。

VFの小電流値及び大電流値は,交流及びインパルス動作を含むことを要求する場合もある。

38

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.5.11 ピーク順リカバリ電圧,VFRM この試験の目的は,急しゅんな電流波形の条件下での順導通TSS

のピーク順電圧を決定することである。この電圧値は,保護する回路の最大負荷である。使用する試験回

路及びレベルは,速いインパルスブレークダウン電圧V(BO)の決定に用いるものと同じでなければならない

(図18参照)。試験機は,順電流立ち上がりdi/dtの規定した定格でダイオードをスイッチし,ピーク順リ

カバリー電圧VFRM値を測定しなければならない(図31参照)。特に規定がない場合,表4に示す速いイン

パルス上昇率1 000 v/μs,10 A/μsを試験に使用することが望ましい。

VF

V

FRM

dIF/dt

IF

v

i

t (μs)

t (μs)

t (μs)

t (μs)

VF

dIF/dt

VFRM

図 31 ダイオードのピーク順リカバリ波形

39

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.5.12 臨界オフ電圧上昇率,dv/dt この試験の目的は,TSSがVDRM定格より低いピーク値の急しゅんな

システム電圧によってスイッチオンしないことを検証することである。臨界dv/dt及びVDRMの最小値に等

しく規定した電圧を動作していない供試品に印加しなければならない。ピーク負荷電圧は,少なくとも50

μsの間隔を持続しなければならない。供試品は,部分的にも試験中にスイッチオンしてはならない。電圧

上昇は,指数関数形又は線形である(図32及び図33参照)。指数関数形上昇波形では,dv/dt値は,0.632VDRM

/ t として計算する。tは,電圧が上昇の始まりから0.632VDRMまで上昇するまでの時間である。線形上昇

の場合,dv/dt値は0.8VDRM / (t90−t10)として計算する。t10及びt90は,各電圧が0.1VDRM及び0.9VDRMに上昇

するまでの時間である。

TSSの各スイッチング極性は,個別に試験し,測定しなければならない。

DUT

V

S1

R3

C1

R1

R2

CRO

PS

DUT

PS

S1

R1

:供試品

:直流電圧電源

:スイッチ

:充電抵抗

R2

R3

C1

CRO

:DUTスイッチ時の電流制限抵抗

:S1開路後の放電抵抗

:充電コンデンサ

:オシロスコープ又は同等品

図 32 指数関数形臨界オフ電圧上昇率di/dt試験回路

S1

ZD1

V

DUT

C1

R1

R2

CRO

PS

DUT

PS

S1

R1

:供試品

:定電流電源

:試験開始時開路するNCスイッチ

:S1閉路後の充電抵抗

R2

C1

ZD1

CRO

:DUTスイッチ時の電流制限抵抗

:充電コンデンサ

:VDRMのクランプ電圧

:オシロスコープ又は同等品

図 33 線形臨界オフ電圧上昇率di/dt試験回路

5.5.13 ブレークダウン電圧の温度係数,αV(BR) この試験の目的は,回路電圧のクリッピングレベルを示

すTSSの小電流ブレークダウン電圧V(BR)が温度によってどのように変化するかを決定することである。

V(BR)の値は,規定した動作温度範囲にわたって測定しなければならないV(BR)の温度変化が非線形である場

合は,電圧対温度のグラフとして表記しなければならない。V(BR)の温度変化が本質的に線形である場合は,

規定した温度範囲にわたって平均%/K又はmV/K変化として表記しなければならない。

αV(BR)=1 000(V(BR)Tmax−V(BR)Tmin)/(Tmax−Tmin) mV/K

40

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

又は,

αV(BR)=100(V(BR)Tmax−V(BR)Tmin)/[(Tmax−Tmin)(V(BR)T25)] %/K

Tmax: 最高動作温度(℃)

Tmin: 最小動作温度(℃)

T25: 周囲温度25 ℃

V(BR)Tmax: TmaxでのV(BR)

V(BR)Tmin: TminでのV(BR)

V(BR)T25: T25でのV(BR)

5.5.14 温度による保持電流変化 この試験の目的は,デバイスが常にスイッチオフであることを保証する

ために,TSSの保持電流IHが温度によってどのように変化するかを決定することである。IHの値(5.5.6

参照)は,規定した使用温度範囲にわたって測定し,電流対温度のグラフとして表記しなければならない。

5.5.15 温度軽減 この試験の目的は,規定した温度範囲にわたって信頼できる防護動作を確保するために,

TSSの軽減カーブを検証することである。TSSの定格は,高温と同様に低温で軽減する場合もある。VDRM,

VRM,IFRM,IFSM,IPPSM,ITRM,ITSM及びdi/dtに関与する定格試験手順は,試験温度のストレスレベルを適

切に調整して使用しなければならない。電力軽減は,Rthの決定値を用いて最高接合温度及び規定基準温度

(周囲,ケース及びリード)での最高電力を計算することで検証できる。

5.5.16 熱抵抗,Rth この試験の目的は,TSSの連続的電力容量を決定することである。使用する試験回

路は,図34と機能的に等価でなければならない。電力を消費させる直前に,温度依存特性値を基準周囲温

度で測定しなければならない。次に,一定値の電力をデバイスに印加する。温度依存特性の測定であるこ

とを考慮して,短期間(< 2 %デューティサイクル)電力を遮断する。これらの測定が安定したとき,安

定した測定条件が達成されたといえる。事前の温度特性から,初期及び安定期の測定値は,接合温度値に

変換することができる。安定している接合温度が,デバイス最高接合温度TJMの+0 % −20 %の範囲内

にない場合は,試験の電力レベルを,範囲内に到達するまで適切に調整し,試験し続けなければならない。

測定値を熱抵抗Rthで表現すると,異なる基準温度及び接合温度での電力容量を計算できる。Rthの値は,

次の式によって計算する。

熱抵抗(接合部及び周囲間):

RthJA = (TJPK−TA ) / PTOT (K/W)

熱抵抗(接合部及びケース間):

RthJC= (TJPK−TC ) / PTOT (K/W)

熱抵抗(接合部及びリード間):

RthJL=(TJPK−TL)/PTOT (K/W)

TA: 基準周囲温度

TC: 冷却によって一定に維持された基準ケース温度

TL: 冷却によって一定に維持された基準リード温度

TJPK: ピーク接合温度 0.8TJM<TJPK<TJM

PTOT: 動力パルスの振幅

TSSのスイッチング及び順導通極性は,個別に試験し,測定しなければならない。測定に際しては,測

定条件が整い,値を読み取るまでに時間を要する。この間,接合温度が冷やされるので,計算温度は低く

41

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

なる。この温度誤差は,電力パルス消費後に連続測定を行って,パルス消費直後の温度を推定することに

よって修正できる。

DUT

CT

I

V

S1

CRO

TG2

TG1

ZD1

DUT

CT

TG1

TG2

S1

ZD1

CRO

------

:供試品

:直流カレントプローブ又は同等品

:温度感知特性測定器

:定電力発生器

:TG1及びTG2のスイッチ

:クランプ電圧>V(BO)

:2チャンネルオシロスコープ又は同等品

:TG1及びS1は同期

図 34 熱抵抗及び熱インピーダンス試験回路

5.5.17 過渡熱インピーダンス,Zth(t) この試験の目的は,規定した電力パルス継続時間tのTSS電力容量

を測定し,決定することである。使用する試験回路は,図34と機能的に等価でなければならない。電力パ

ルスの消費直前に,温度依存特性値を基準周囲温度で測定しなければならない。次に,一定電力のパルス

を規定した時間消費させる。パルス消費後,直ちに温度依存特性値を再測定しなければならない。事前の

温度特性によって,これら二つの温度における特性値は,接合温度に変換することができる。電力パルス

消費後の温度が最大接合温度(TJM)の+0 %−20 %の範囲内にない場合は,範囲内となるまで電力レベ

ルを適切に調整し,試験を繰り返さなければならない。試験を繰り返すとき,TSSの熱平衡が回復するま

での適切な時間間隔をとらなければならない。測定値を過渡熱インピーダンスZth(t)で表現すると,異なる

基準温度及び接合温度での電力容量を計算できる。過渡熱インピーダンスZth(t)の値は,次の式によって算

出する。

過渡熱インピーダンス[規定した時間間隔(t)で,接合部及び周囲間]

ZthJA(t)=(TJPK−TA)/PTOT (K/W)

過渡熱インピーダンス[規定した時間間隔(t)で,接合部及びケース間]

ZthJC(t)=(TJPK−TC)/PTOT (K/W)

過渡熱インピーダンス[規定した時間間隔(t)で,接合部及びリード間]

ZthJL(t)=(TJPK−TL)/PTOT (K/W)

TA: 基準周囲温度

TC: 冷却によって一定に維持された基準ケース温度

TL: 冷却によって一定に維持された基準リード温度

42

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

TJPK: ピーク接合温度 0.8TJM<TJPK<TJM

PTOT: 電力パルスの振幅

t: 電力パルスの継続時間

TSSのスイッチング及び順導通極性は,それぞれ個別に試験し,測定しなければならない。電力パルス

消費後,測定条件が整い,値を読み取るまでに時間を要する。その間,接合温度が低いため,計算温度は

低くなる。この温度誤差は,電力パルス消費後に連続測定を行って,パルス消費直後の温度を推定するこ

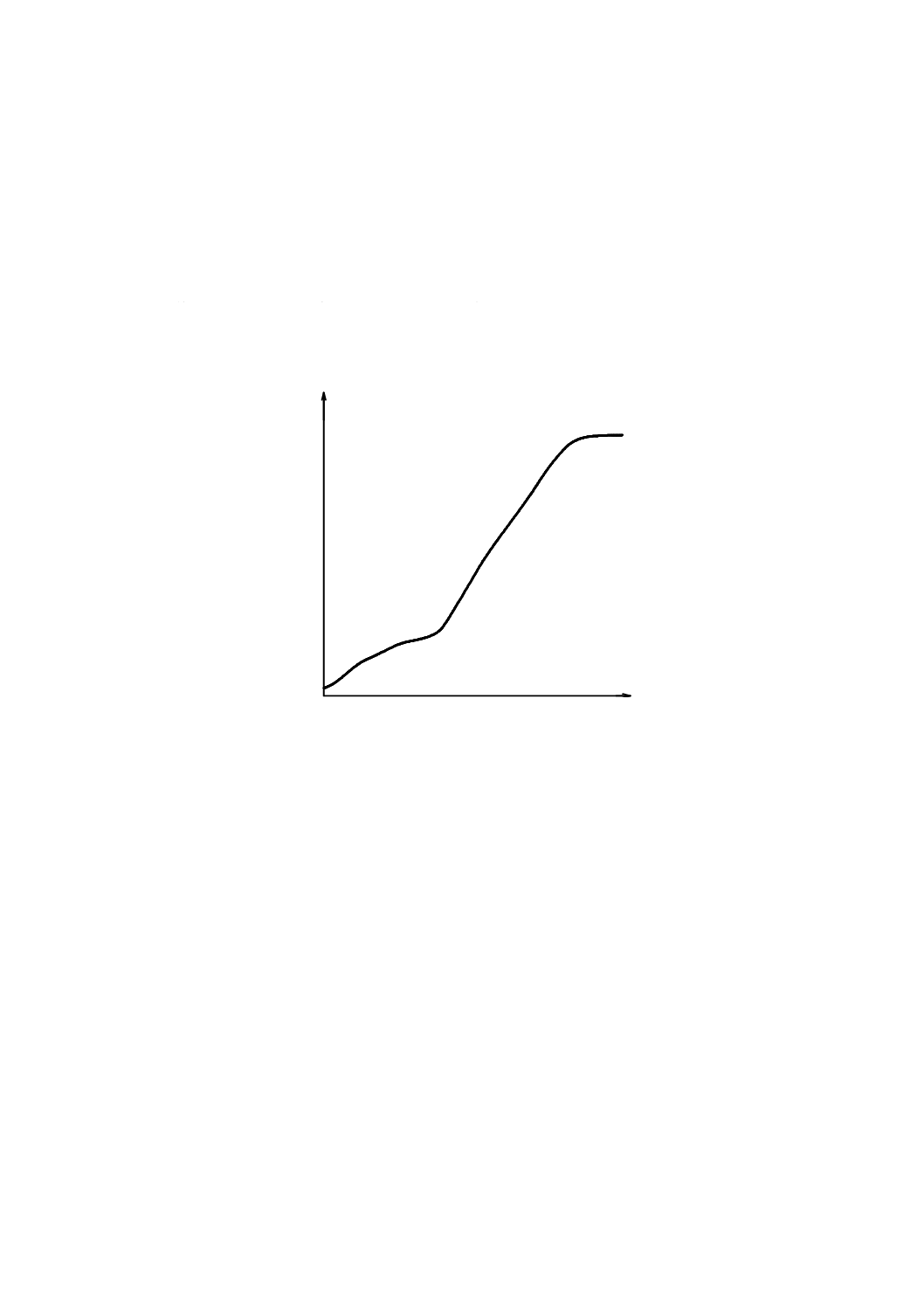

とによって修正できる。特に規定がない限り,Zth(t)はグラフ上での100 μsから定常状態までの時間特性で

決定することが望ましい(図35参照)。

t (s)

0.0001

0.001

0.01

0.1

1

10

100

ZthJA

(K/W)

1

10

100

ZthJA

図 35 熱インピーダンスと時間との関係

5.5.18 ゲート隣接端子間ピークオフ電圧,VGDM及びピークオフゲート電流,IGDM この試験の目的は,

規定した電圧において防護端子間を高インピーダンスのオフ状態に維持したまま,TSSのゲート隣接端子

間の最大電圧を決定することである。図36の適切な回路を用いて,規定したVDをデバイスの防護端子間

に印加しながら,ゲート隣接端子間電圧を0 Vから防護端子間電流IDが規定値に達するまで増加しなけれ

ばならない。ここで測定したゲート隣接端子間電圧をVGDM,ゲート隣接端子間電流をIGDMとする。

TSSの各スイッチング極性は,個別に試験し測定しなければならない。ゲート制御TSSの繰返しピーク

オフ電圧はVGG+VGDMで示し,これは一定電圧であるVDRMに等しい。

43

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

P-TYPE

GATE

DUT

-

+

PS2

-

+

PS1

V

A1

A2

N-TYPE

GATE

DUT

-

+

PS2

-

+

PS1

V

A1

A2

Pゲート

DUT

Nゲート

DUT

DUT

A1

A2

V

PS1

PS2

:供試品

:ゲート電流測定用電流計

:IDモニタ用電流計

:ゲート隣接端子間測定用電圧計

:ID規定値に設定する可変直流電圧電源

:VDに設定する直流電圧電源

図 36 ゲート隣接端子間ピークオフ電圧VGDM及び電流IGDM試験回路

5.5.19 隣接端子開放時のゲート逆電流,IGAO,IGKO この試験の目的は,隣接端子が開放である場合,ゲ

ート端子電圧供給時にゲートに流れる電流値を決定することである。 図37の適切な回路を用いて,規定

したゲートバイアスVGGをゲートに印加し,ゲートに流れる電流を測定しなけらばならない。この試験は,

正極を開放したPゲートデバイスの逆ゲートから負極へのオフ電流IGAO又は負極を開放したNゲートデバ

イスの逆ゲートから正極へのオフ電流IGKOを決定する。

TSSの各スイッチング極性は,個別に試験し測定しなければならない。

+

-

N-TYPE

GATE

DUT

A

PS

-

+

P-TYPE

GATE

DUT

A

PS

Pゲート

DUT

Nゲート

DUT

DUT

A

PS

:供試品

:逆ゲート電流用電流計

:規定のゲート電圧VGGに設定する直流電源

図 37 隣接端子開放時のゲート逆電流IGAO,IGKO試験回路

5.5.20 主端子短絡時のゲート逆電流,IGAS,IGKS この試験の目的は,隣接端子が他の防護端子に短絡し

ている場合,ゲート端子電圧供給時にゲートに流れる電流値を決定することである。図38の適切な回路を

用いて,規定したゲートバイアス電圧VGGをゲートに印加し,ゲートに流れる電流を測定しなければなら

ない。この試験は,アノードにカソード短絡のPゲートデバイスの逆ゲートオフ状態電流IGAS又はカソー

ドにアノード短絡のNゲートデバイスの逆ゲートオフ状態電流IGKSを決定する。

TSSの各スイッチング極性は,個別に試験し,測定しなければならない。この試験は,ゲート阻止ダイ

オードを内蔵したデバイスに対して適用する。

44

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

-

+

PS

A

-

+

PS

A

DUT

TYPE P

DUT

TYPE N

Pゲート

DUT

Nゲート

DUT

DUT

A

PS

:供試品

:逆ゲート電流用電流計

:規定のゲート電圧VGGに設定する直流電源

図 38 主端子短絡時のゲート逆電流IGAS,IGKS試験回路

5.5.21 オン状態のゲート逆電流,IGAT,IGKT この試験の目的は,TSSがオン状態の場合,ゲート端子電

圧供給時にゲートに流れる電流値を決定することである。図39の適切な回路を用いて,規定したゲートバ

イアス電圧VGGをゲートに印加し,防護端子間に接続した試験機によってデバイスをオン状態にスイッチ

しなければならない。ゲート電流は,規定したオン状態電流ITで測定しなければならない。試験機及びIT

値は,VTの交流値又は直流値の決定に用いるものと同じでなければならない。この試験は,Pゲートデバ

イスの逆ゲート電流IGAT又はNゲートデバイスのオン状態の逆ゲート電流IGKTを決定する。

TSSの各スイッチング極性は,個別に試験し,測定しなければならない。この試験は,ゲート阻止ダイ

オードを内蔵したデバイスに対して適用する。

N-TYPE

GATE

DUT

A2

R1

A1

PS

PG

HV PULSE

GENERATOR

-

+

-

+

A2

P-TYPE

GATE

DUT

R1

PS

A1

PG

HV PULSE

GENERATOR

-

+

Pゲート

DUT

Nゲート

DUT

PG

PG

DUT

A1

A2

PG

PS

R1

:供試品

:ITに同期したピーク電流計

:ピーク電流計

:規定の特性を備えた高圧パルス発生器

:規定のゲート電圧VGGに設定する直流電源

:ITを決定する抵抗

図 39 オン状態のゲート逆電流IGAF,IGKF試験回路

-

+

45

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.5.22 順導通状態のゲート逆電流,IGAT,IGKT この試験の目的は,順導通TSSがダイオード導通状態の

場合,ゲート端子電圧供給時にゲートに流れる電流値を決定することである。図40の適切な回路を用いて,

規定したゲートバイアス電圧VGGをゲートに印加し,防護端子間に接続した試験機によってデバイスを順

導通状態にしなければならない。ゲート電流は,規定した順導通電流IFで測定しなければならない。試験

機及びIF値は,VFの交流又は直流値の決定に用いるものと同じでなければならない。この試験は,Pゲー

トデバイスの順導通状態における逆電流IGAF又はNゲートデバイスの順導通状態における逆ゲート電流

IGKFを決定する。

この試験は,ゲート阻止ダイオードを内蔵したデバイスに対して適用する。

N-TYPE

GATE

DUT

A1

A2

R1

PS

PG

HV PULSE

GENERATOR

A2

PS

A1

R1

P-TYPE

GATE

DUT

PG

HV PULSE

GENERATOR

-

+

-

+

-

+

-

+

Pゲート

DUT

Nゲート

DUT

PG

PG

DUT

A1

A2

PG

PS

R1

:供試品

:ITに同期したピーク電流計

:ピーク電流計

:規定の特性を備えた高圧パルス発生器

:規定のゲート電圧VGGに設定する直流電源

:ITを決定する抵抗

図 40 順導通状態のゲート逆電流IGAF,IGKF試験回路

5.5.23 ゲートスイッチング電荷QGS この試験の目的は,ゲート結合容量を決定するために,TSSが電圧

を制限するときに,ゲート端子供給に必要な要求電荷を決定することである。図41又は図42の適切な回

路を用いて,規定したゲートバイアス電圧VGGをゲートに印加し,防護端子間に接続した試験機によって

オン状態にスイッチしなければならない。ゲート電荷は,制限範囲の電流を記録し,それを積算すること

によって測定しなければならない(図43参照)。試験機は,V(BO)の速い上昇率の決定に用いるものと同じ

でなければならない。TSSの各スイッチング極性は,個別に試験し,測定しなければならない。

46

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

0

I GSM

Q GS

N-TYPE

GATE

DUT

V A

CT

V G CRO

I

PS

RG

RAMP

GENERATOR

D

CRO

PS

I

P-TYPE

GATE

DUT

V

K

V

G

CT

RG

RAMP

GENERATOR

Q GS

I GSM

0

D

-

+

-

+

-

+

-

+

RG

RG

Pゲート

DUT

Nゲート

DUT

DUT

VA,VK

VG

D

RG

PS

CT

CRO

:供試品

:隣接端子電圧

:ゲート端子電圧

:直列ゲート阻止ダイオード

:規定のdi/dt及び特性dv/dtの上昇波形発生器

:規定のゲート電圧VGGに設定する直流電源

:変流器又は同等品

:2チャンネルオシロスコープ又は同等品

図 41 ピークゲートスイッチング電流IGSM,ゲートスイッチング電荷QGS及び

ゲート隣接端子間ブレークオーバ電圧VGK(BO),VGA(BO)試験回路

47

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

0

I GSM

Q GS

N-TYPE

GATE

DUT

V A

CT

V G CRO

I

PS

RG

RAMP

GENERATOR

CRO

PS

I

P-TYPE

GATE

DUT

V K

V G

CT

RG

RAMP

GENERATOR

Q GS

I GSM

0

-

+

-

+

-

+

-

+

Nゲート

DUT

Pゲート

DUT

RG

RG

DUT

VA,VK

VG

D

RG

PS

CT

CRO

:供試品

:隣接端子電圧

:ゲート端子電圧

:直列ゲート阻止ダイオード

:規定のdi/dt及びdv/dt特性を備えた上昇波形発生器

:規定のゲート電圧VGGに設定する直流電源

:変流器又は同等品

:2チャンネルオシロスコープ又は同等品

図 42 ゲートダイオードを内蔵した供試品のピークゲートスイッチング電流IGSM,ゲートスイッチング

電荷QGS及びゲート隣接端子間ブレークオーバ電圧VGK(BO),VGA(BO)試験回路

5.5.24 ピークゲートスイッチング電流,IGSM この試験の目的は,TSSが電圧を制限をしているときに,

ゲート端子供給に必要なピーク電流を決定すること及び過度の電圧上昇が生じないように,ゲート供給に

ついての設計情報を提供することである。図41又は図42の適切な回路を用いて,規定したゲートバイア

ス電圧VGGをゲートに印加し,防護端子間に接続した試験機によってデバイスをオン状態にスイッチしな

ければならない。ピークゲートスイッチング電流IGSMは,電圧を制限している間に測定しなければならな

い。

試験機は,V(BO)の遅い上昇率の決定に用いるものと同じでなければならない。TSSの各スイッチング極

性は,個別に試験し,測定しなければならない。

5.5.25 ゲート隣接端子間ブレークオーバ電圧,VGK(BO),VGA(BO) この試験の目的は,ゲート供給電圧と

TSSのブレークオーバ電圧との差を決定し,供給電圧及び上昇率の範囲にわたってブレークオーバ電圧値

の計算を可能とすることである。図41又は図42の適切な回路を用いて,規定したゲートバイアス電圧VGG

をゲートに印加し,防護端子間に接続した試験機によってデバイスをオン状態にスイッチしなければなら

ない。

48

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ブレークオーバでのゲート隣接端子間電圧のピーク値を測定しなければならない(図43の例を参照)。

試験機は,V(BO)の決定に用いたものと同じでなければならない。この試験は,Pゲートデバイスのブレー

クオーバでのゲートカソード間電圧VGA(BO)及びNゲートデバイスのブレークオーバでのゲートアノード間

の電圧VGK(BO)を決定することである。TSSの各スイッチング極性は,個別に試験し,測定しなければなら

ない。

QGS

IK

VGK(BO)

VGG

VK

VGG

VK

i

i

v

v

t (μs)

t (μs)

t (μs)

t (μs)

IG

IK

t (μs)

t (μs)

t (μs)

t (μs)

VK

VGG

IG

IK

IK

VK

VGG

QGS

VGK(BO)

図 43 Pゲート供試品のVGK(BO)及びQGSの測定のための全体及び拡張クランピング波形

(diK/dt =10 A/μs,VGG= −72 V)

49

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

附属書A(規定)特殊な使用条件

TSSの製造又は適用において特別な配慮を要求する代表的な特殊使用条件を次に示す。これらについて

は製造業者に注意を促すことが望ましい。

A.1

環境条件

A.1.1 気候条件

a) 通常使用条件を超える温度,湿度及び圧力値

b) 降雨(雨,雪及びあられ)

c) 放射(日射,熱線及びイオン照射)

d) 他の水要因(滴下,水はね,蒸気,潜水,結露及び氷結)

A.1.2 生物による条件

a) 植物系

b) 動物系

A.1.3 化学的に影響のある物質

a) 有害ガス又は蒸気

b) 塩水噴霧

c) 可燃性又は爆発性ガス

A.1.4 機械的又は電気的に影響のある物質

a) ほこり

b) すす

c) 砂

A.1.5 汚染する流体

A.2

機械的な条件

a) 振動(定常又は衝撃)

b) 落下(定常又は衝撃)

c) 衝突

d) 定常的な負荷

A.3

様々な要因

a) 組立前及び組立中の条件

b) はんだ付け性

c) 可燃性

d) 特殊な輸送又は保存条件

e) デバイスの定格を超える電気的過負荷

f)

過負荷時における起こり得るパッケージ破裂

g) 特殊な地理的状況

h) 使用者が既知の他の特殊な条件

50

C 5381-341:2005 (IEC 61643-341:2001)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

附属書B(参考)基準インパルス波形による米国審査基準

この附属書は,本体及び附属書(規定)に関連する事柄を補足するもので,規定の一部ではない。

本体の表2及び表3の参照の項に記載された,対応する国際規格番号の規格名称である。

B.1 電話局装置の審査

Bellcore,GR-1089-CORE,Issue 2,November 1997,Electromagnetic Compatibility and Electric Safety ‒ Generic

Criteria for Network Telecommunications Equipment

B.2 加入者端末装置の審査書

FCC Title 47 CFR,March 1998,Part 68 Connection of terminal equipment to the telephone network,Subpart D

‒ Conditions for Registration.

B.3 試験波形

ANSI/IEEE Std C62.45 ‒1992,IEEE Guide on Surge Testing for Equipment connected to Low Voltage AC Power

Circuits